#### https://matheo.uliege.be

### Development of an on-board computer for a nanosatellite

Auteur : Horbach, Amadis

Promoteur(s) : Redouté, Jean-Michel

Faculté : Faculté des Sciences appliquées

Diplôme : Master : ingénieur civil électricien, à finalité spécialisée en "signal processing and intelligent robotics"

Année académique : 2020-2021

URI/URL : http://hdl.handle.net/2268.2/11659

Avertissement à l'attention des usagers :

Tous les documents placés en accès ouvert sur le site le site MatheO sont protégés par le droit d'auteur. Conformément aux principes énoncés par la "Budapest Open Access Initiative" (BOAI, 2002), l'utilisateur du site peut lire, télécharger, copier, transmettre, imprimer, chercher ou faire un lien vers le texte intégral de ces documents, les disséquer pour les indexer, s'en servir de données pour un logiciel, ou s'en servir à toute autre fin légale (ou prévue par la réglementation relative au droit d'auteur). Toute utilisation du document à des fins commerciales est strictement interdite.

Par ailleurs, l'utilisateur s'engage à respecter les droits moraux de l'auteur, principalement le droit à l'intégrité de l'oeuvre et le droit de paternité et ce dans toute utilisation que l'utilisateur entreprend. Ainsi, à titre d'exemple, lorsqu'il reproduira un document par extrait ou dans son intégralité, l'utilisateur citera de manière complète les sources telles que mentionnées ci-dessus. Toute utilisation non explicitement autorisée ci-avant (telle que par exemple, la modification du document ou son résumé) nécessite l'autorisation préalable et expresse des auteurs ou de leurs ayants droit.

Master's thesis carried out to obtain the degree of Master of Science in Electrical Engineering by Horbach Amadis

# Development of an on-board computer for a nanosatellite

University of Liège - School of Engineering and Computer Science

Supervisor: Jean-Michel Redouté

Academic year 2020-2021

# Acknowledgements

I would like to start by thanking Hervé Pierre. Firstly, for proposing this thesis to me. Then, for his follow-up and guidelines during the whole year. And finally, for his proofreading of this thesis. His help was really valuable to me. I would also like to thank Professor Jean-Michel Redouté for giving me and other students the chance to work on such an interesting project.

I would like to express my thanks to the Microsys team for the good atmosphere that always prevailed in the working room and their kind advice in case of need. I would especially like to thank Morgan with whom I was happy to share on the current OUFTI project.

I also would like to thank my friends for their support during this particularly strange and hard period we are all living. You have allowed me to get a bit of fresh air and to go through this work.

Finally, I want to thank my family for their constant support during my studies and particularly during this work. I would especially like to thank my mother, my sister and my uncle for their proofreading of this thesis.

# Abstract

The purpose of this master thesis is to develop the On-Board Computer (OBC) of the University educational CubeSat OUFTI. The OBC is the central part of a CubeSat allowing the control of all the other subsystems. Its development is therefore crucial and must be carried out effectively and efficiently. As this is not the first CubeSat developed by the university, the first thing to do is to analyze the previous ones in order to extract their strengths and more importantly their weaknesses. Thus, this work starts with an introduction of the concept of CubeSat followed by a brief analysis of the main elements that created difficulties in the previous CubeSat of the University.

Once the context of this thesis is introduced, the development of the electric circuit can be detailed. The choice of the components is logically based on the space conditions introduced in the first chapter. The most important part of the circuit is the microcontroller. Indeed, this is the component that will manage and monitor all the other components, whether they are on the OBC board or on one of the other boards in the CubeSat. It is thus essential that it works efficiently and without any failure. Then, the other components of the OBC can be selected and assembled in schematics. All the components are finally placed in a PCB to form the OBC's PCB.

When the hardware of the OBC is finished and its PCB is created, it is important to test that the OBC performs all its required tasks. To this end, a software has to be developed. This software implements a real time operating system architecture. The creation of the code implemented to test the correct functioning of the OBC is then detailed.

The final part of this thesis explores the various tests that have been performed along with the most important results obtained. These tests went from simple voltage measurements to communication with external devices. The tests allow a first validation of the OBC of the university CubeSat.

# List of acronyms

| ACK                  | Acknowledge                                         |

|----------------------|-----------------------------------------------------|

| ADC                  | Analog-to-Digital Converter                         |

| ADCS                 | Attitude Determination and Control Subsystem        |

| AFEC                 | Analog Front-End Controller                         |

| $\mathbf{ARM}$       | Advanced RISC Machine                               |

| COTS                 | Commercial Off The Shelf                            |

| CPHA                 | Clock Phase                                         |

| CPOL                 | Clock Polarity                                      |

| $\mathbf{CS}$        | Chip Select                                         |

| $\mathbf{DDR}$       | Double Data Rate                                    |

| DOUT                 | Data Out                                            |

| DRAM                 | Dynamic Random Access Memory                        |

| DTCM                 | Data Tightly Coupled Memory                         |

| ECC                  | Error Correction Code                               |

| EEPROM               | Electrically Erasable Programmable Read-Only Memory |

| EPROM                | Erasable Programmable Read-Only Memory              |

| $\mathbf{EPS}$       | Electrical Power System                             |

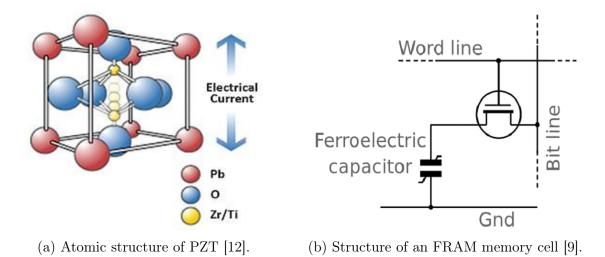

| $\mathbf{FRAM}$      | Ferroelectrical Random Access Memory                |

| $\mathbf{GCR}$       | Galactic Cosmic Rays                                |

| HSMCI                | High Speed Multimedia Card Interface                |

| I2C                  | Inter-Integrated Circuit                            |

| ICD                  | In-Circuit Debugger/Programmer                      |

| IDE                  | Integrated Development Environment                  |

| IO                   | Input/Output                                        |

| ITCM                 | Instruction Tightly Coupled Memory                  |

| LEO                  | Low Earth Orbit                                     |

| $\operatorname{LET}$ | Linear Energy Transfer                              |

| MCAN                 | Master Controller Area Networks                     |

| MCU                  | Microcontroller Unit                                |

| MISO                 | Master In Slave Out                                 |

| MOSI                 | Master Out Slave In                                 |

| MOSFET               | Metal-Oxide-Semiconductor Field-Effect Transistor   |

| MSB                  | Most Significant Bit                                |

| NASA                 | National Aeronautics and Space Administration       |

| NCPHA                | Not Clock Phase                                     |

| NVIC             | Nested Vector Interrupt Control                         |

|------------------|---------------------------------------------------------|

| OBC              | On-Board Computer                                       |

| OS               | Operating System                                        |

| PCB              | Printed Circuit Board                                   |

| $\mathbf{PMC}$   | Power Managment Controller                              |

| PROM             | Programmable Read-Only Memory                           |

| $\mathbf{PZT}$   | Lead zirconate titanate                                 |

| $\mathbf{RAM}$   | Random Access Memory                                    |

| $\mathbf{RMAP}$  | Remote Memory Access Protocol                           |

| ROM              | Read-Only Memory                                        |

| $\mathbf{RSD}$   | Redundant Signed Digit                                  |

| RSWDT            | Reinforced Safety Watchdog Timer                        |

| RTC              | Real Time Clock                                         |

| RTOS             | Real Time Operating System                              |

| $\mathbf{RTT}$   | Real-Time Timer                                         |

| $\mathbf{SAA}$   | South Atlantic Anomaly                                  |

| $\mathbf{SCL}$   | Serial Clock Line                                       |

| $\mathbf{SDA}$   | Serial Data                                             |

| $\mathbf{SDR}$   | Single Data Rate                                        |

| $\mathbf{SDRAM}$ | Synchronous Dynamic Random Access Memory                |

| SDRAMC           | Synchronous Dynamic Random Access Memory Controller     |

| $\mathbf{SEE}$   | Single-Event Effects                                    |

| $\mathbf{SEL}$   | Single-Event Latchup                                    |

| $\mathbf{SEU}$   | Single-Event Upset                                      |

| $\mathbf{SLC}$   | Single-Level Cell                                       |

| SPCK             | Serial Peripheral Interface Clock                       |

| SPE              | Solar Particle Events                                   |

| SPI              | Serial Peripheral Interface                             |

| SRAM             | Static Random Access Memory                             |

| $\mathbf{TCM}$   | Tightly Coupled Memory                                  |

| TID              | Total Ionizing Dose                                     |

| TWI              | Two Wire Interface                                      |

| UART             | Universal Asynchronous Receiver/Transmitter             |

| USART            | Universal Synchronous/Asynchronous Reveiver/Transmitter |

| VREFP            | Positive Voltage Reference                              |

| WDT              | Watch Dog Timer                                         |

| WREN             | Write Enable                                            |

# Contents

| A        | cknov            | vledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>2</b>        |  |

|----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| A        | bstra            | $\mathbf{ct}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3               |  |

| Li       | List of acronyms |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |  |

| Co       | onter            | ıts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6               |  |

| 1        | Intr             | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8               |  |

|          | 1.1              | Project's presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8               |  |

|          | 1.2              | CubeSat history and architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9               |  |

|          |                  | 1.2.1 History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9               |  |

|          |                  | 1.2.2 Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9               |  |

|          |                  | 1.2.3 On-Board Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11              |  |

|          | 1.3              | Space conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12              |  |

|          |                  | 1.3.1 Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12              |  |

|          |                  | 1.3.2 Radiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12              |  |

|          | 1.4              | Power management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14              |  |

| <b>2</b> | Har              | dware design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15              |  |

| -        | 2.1              | Choice of the microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $15^{-5}$       |  |

|          |                  | 2.1.1 SAMV71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17              |  |

|          | 2.2              | Selection of the other components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22              |  |

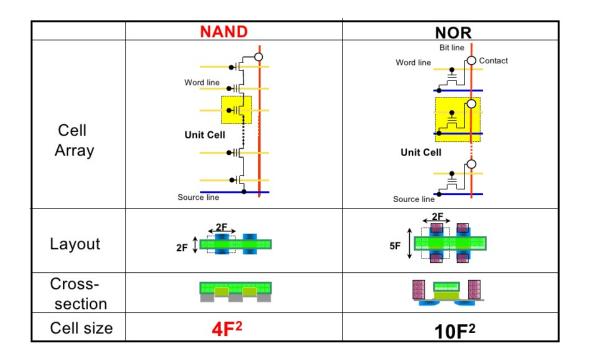

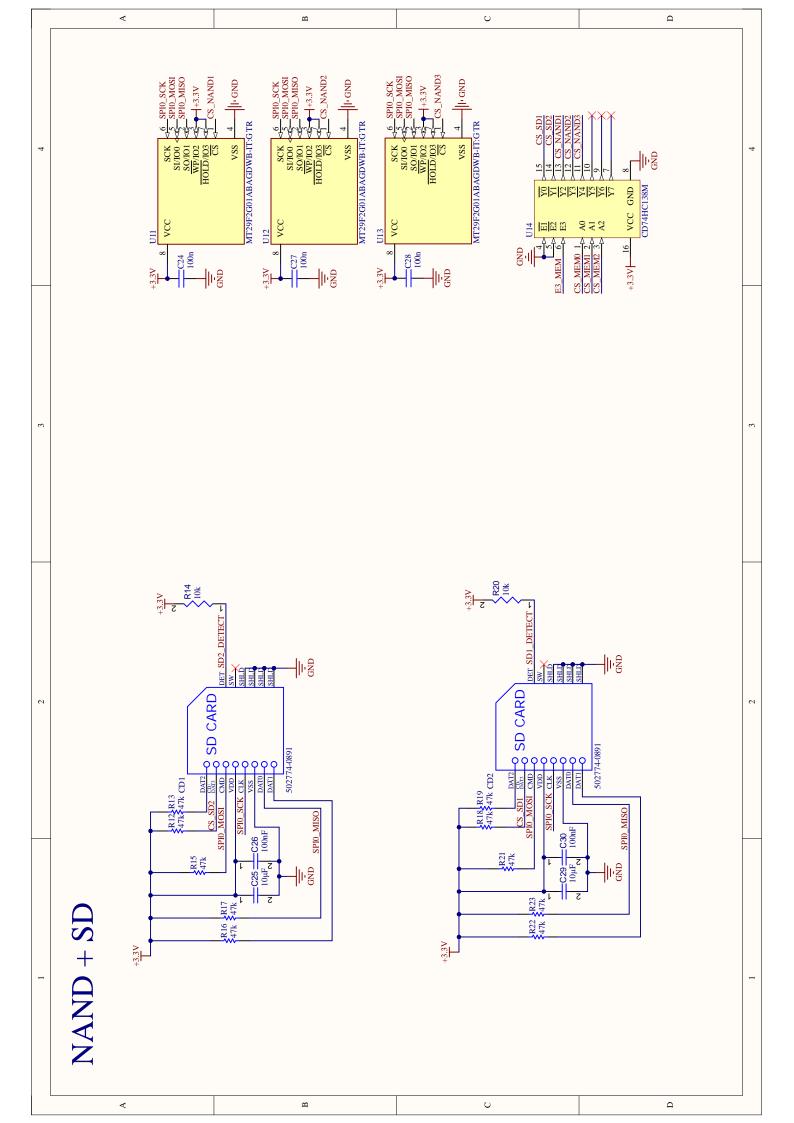

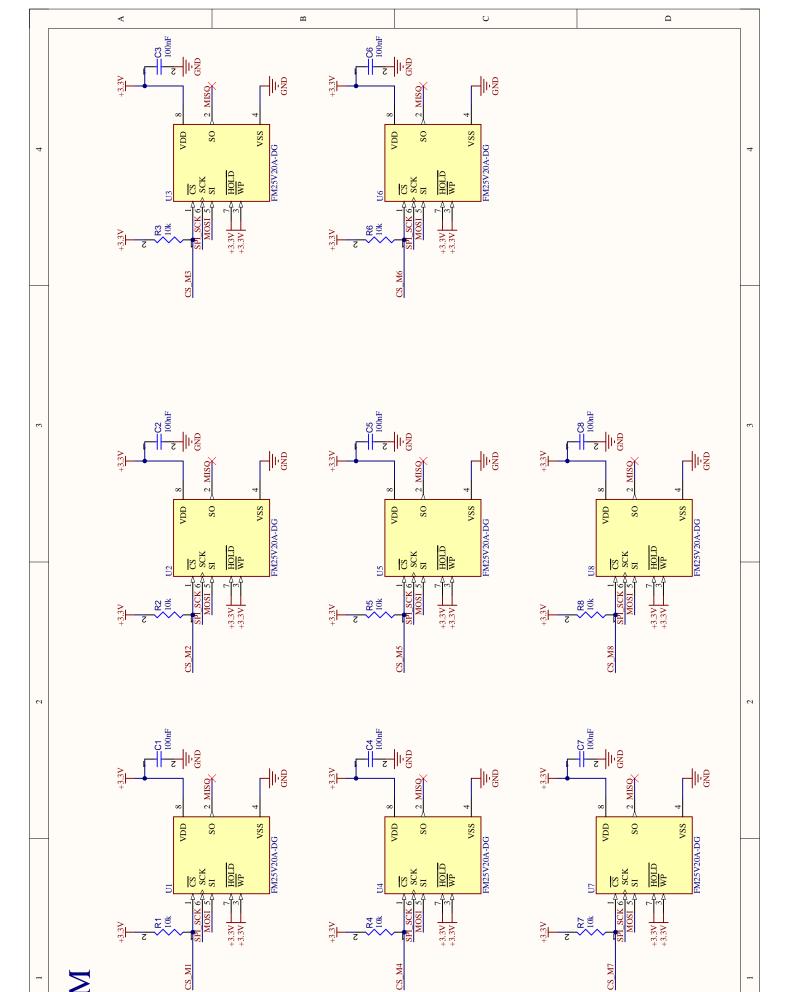

|          |                  | 2.2.1 Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23              |  |

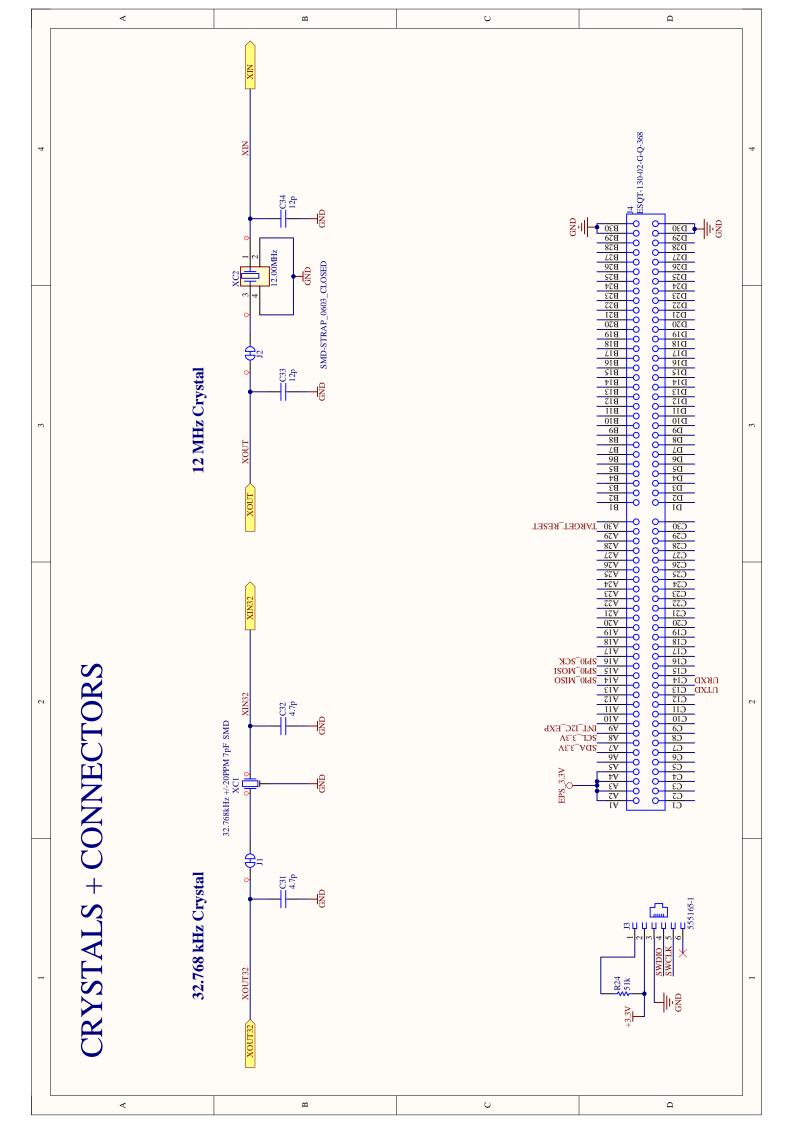

|          |                  | 2.2.2 Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31              |  |

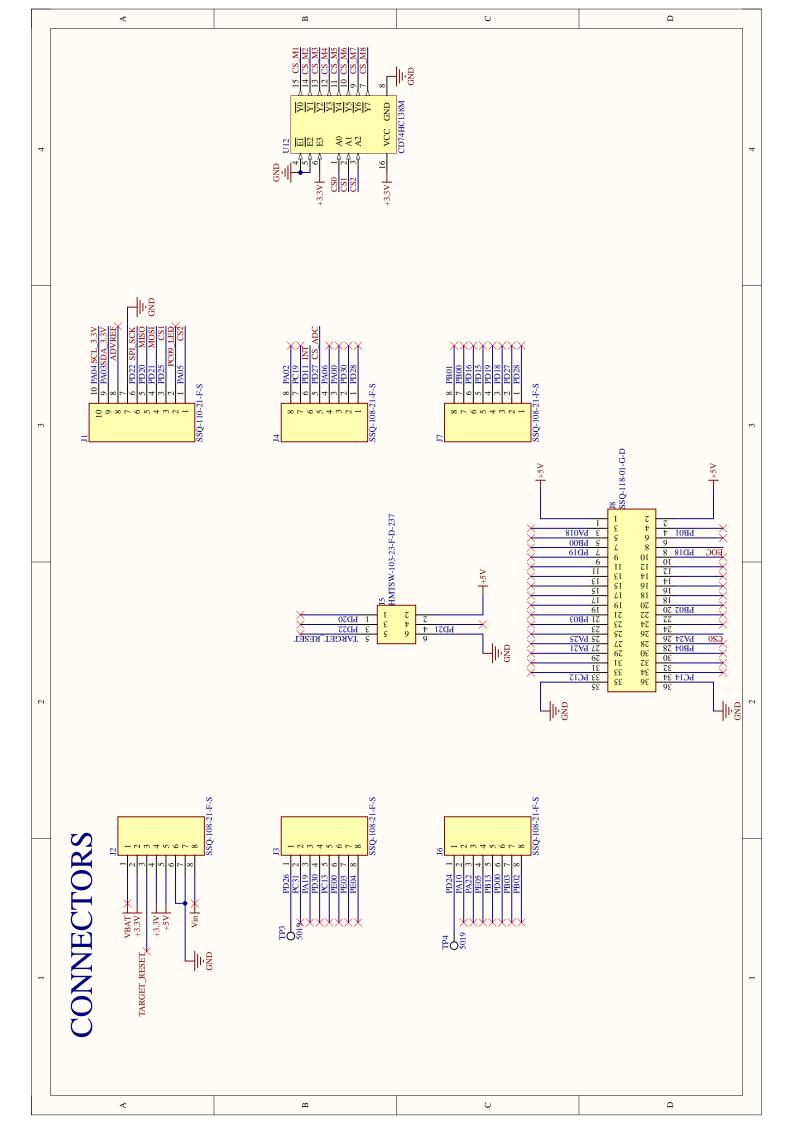

|          |                  | 2.2.3 Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31              |  |

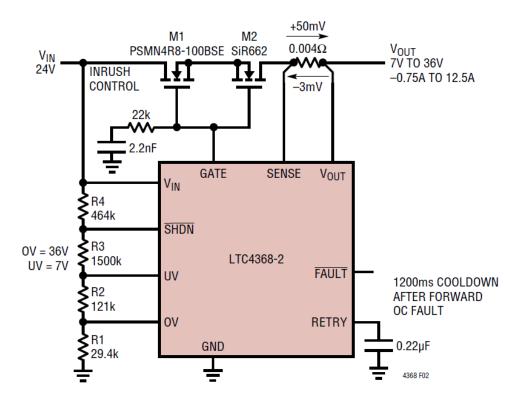

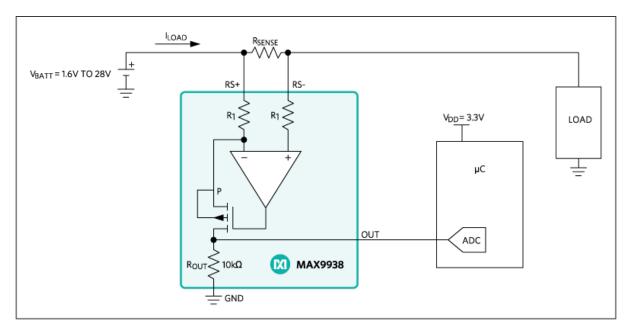

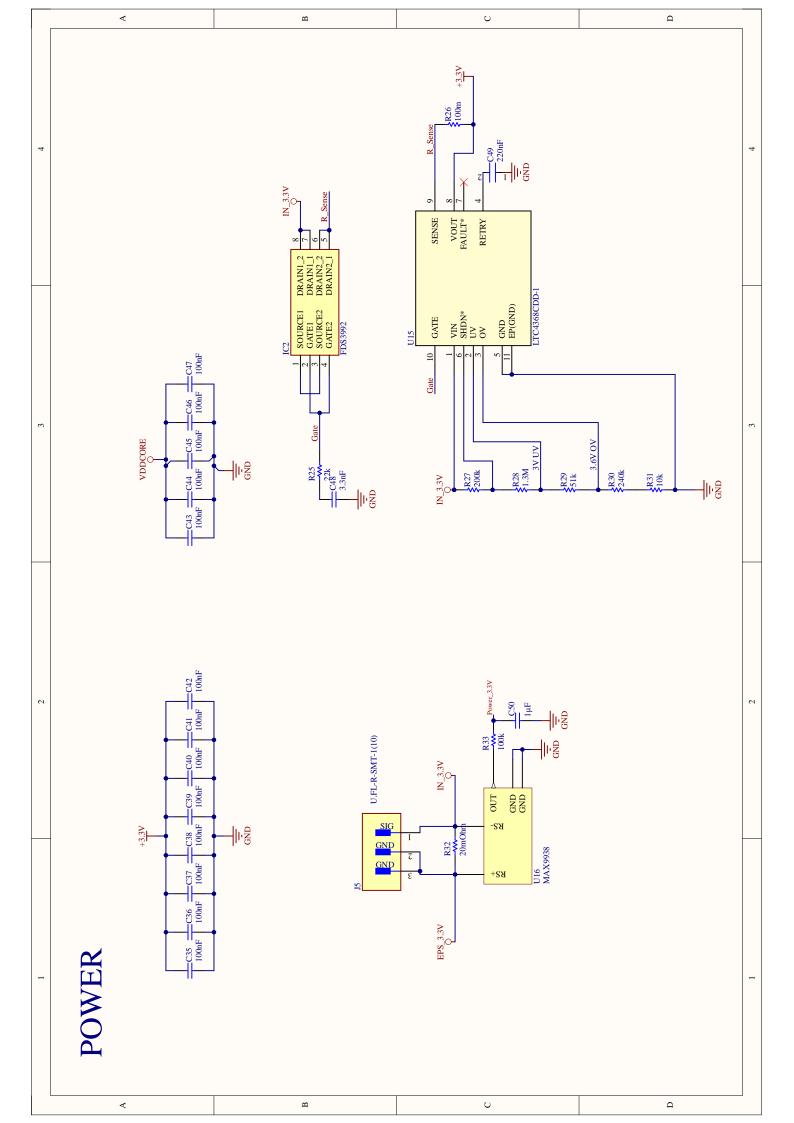

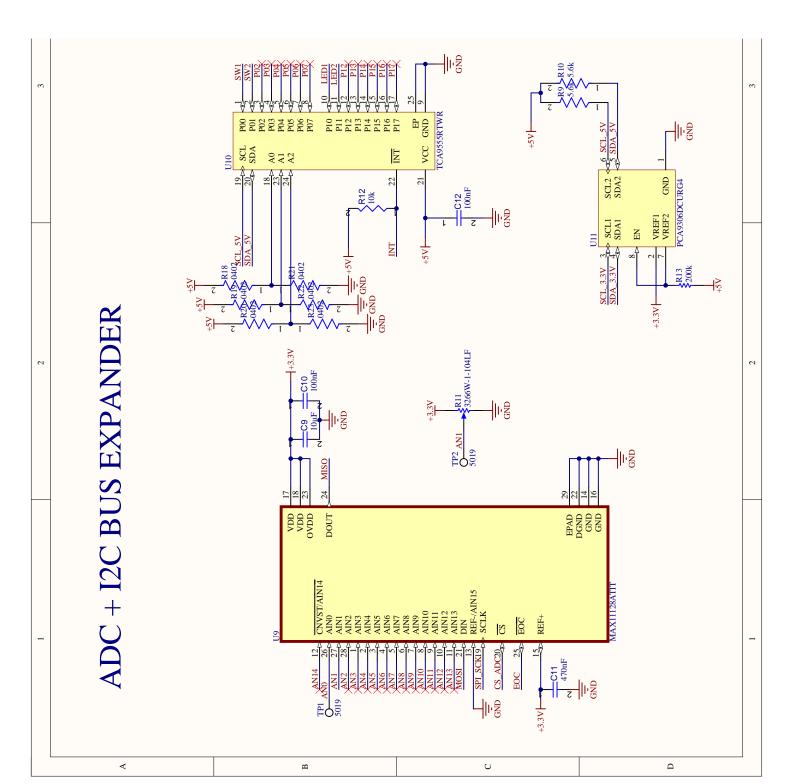

|          |                  | 2.2.4 Power monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33              |  |

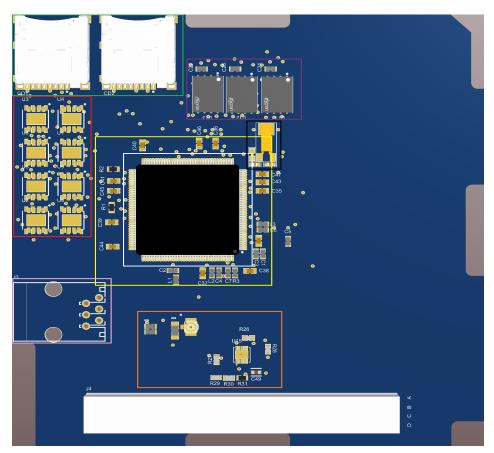

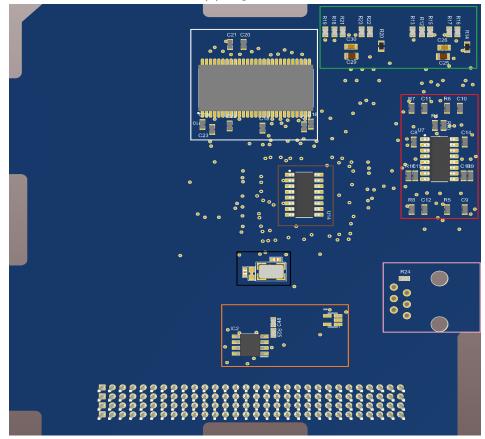

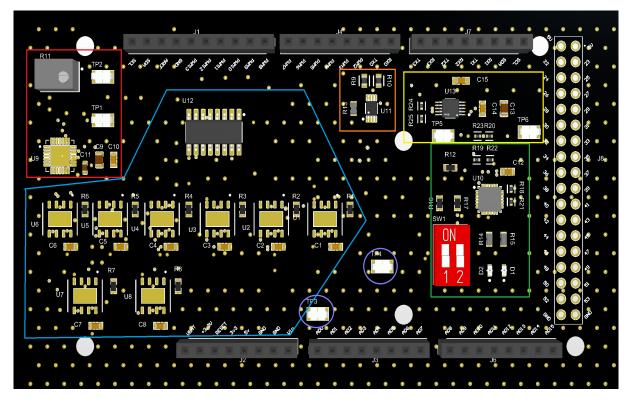

|          | 2.3              | Final PCB presentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 36              |  |

| 3        | Soft             | ware implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38              |  |

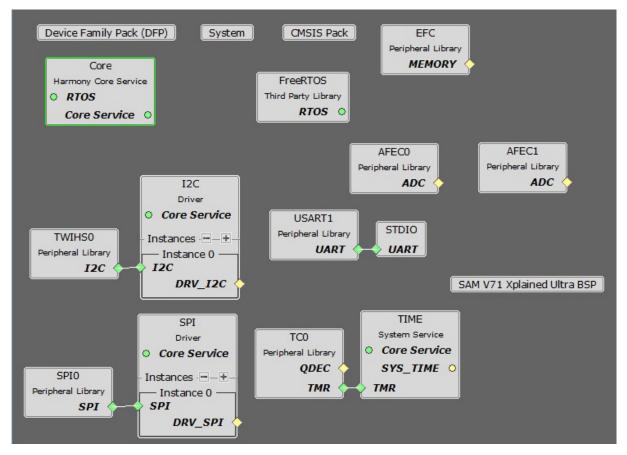

| J        | 3.1              | Software architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38              |  |

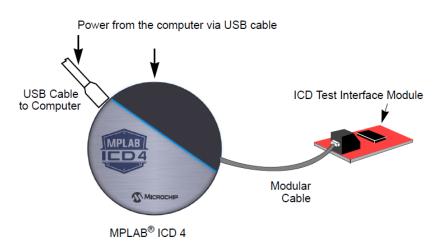

|          | 3.2              | MPLAB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39              |  |

|          | 0.2              | 3.2.1       Harmony v3       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 39<br>39        |  |

|          | 3.3              | Code implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39<br>41        |  |

|          | J.J              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41              |  |

|          |                  | 3.3.1       I2C       I2C       I2C         3.3.2       SPI       I2C       I2C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\frac{42}{43}$ |  |

|          |                  | 3.3.3       External I2C bus task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $43 \\ 45$      |  |

|          |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45<br>46        |  |

|          |                  | 3.3.4 External ADC (SPI) task $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |

|          |                  | 3.3.5 FRAM (SPI) task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47              |  |

|    | 3.3.6 User task                                                                                 | 49                    |

|----|-------------------------------------------------------------------------------------------------|-----------------------|

| 4  | Hardware and Software testing4.1 Development board4.2 PCB compatible with the development board | <b>52</b><br>52<br>54 |

| 5  | Conclusion                                                                                      | <b>58</b>             |

| Aŗ | Appendices 60                                                                                   |                       |

| Α  | Final PCB Schematics                                                                            | 61                    |

| В  | Test PCB Schematics                                                                             | 67                    |

| С  | Codes Git link                                                                                  | 71                    |

| Re | References 73                                                                                   |                       |

# Chapter 1 Introduction

# 1.1 Project's presentation

The University of Liège (ULiège) has a well known history with nanosatellites. It all started in September 2007 when ULiège and the Higher Education Institution of the Province of Liège (HEPL) decided to launch a project aimed at developing a nanosatellite. After several years of development, the nanosatellite named OUFTI-1 was launched and successfully reached its orbit on 25th April 2016. Unfortunately, the nanosatellite encountered a failure quickly after. Even if there is no proof of what caused the failure, radiation is thought to be responsible. In 2017, ULiège and HEPL decided to develop a second nanosatellite named OUFTI-2. However, mainly due to the high power consumption of its microcontroller (MCU), this one was never launched.

In 2020, ULiège and HEPL decided to start a new OUFTI project. This one is meant to be composed of four main sections: (i) an Electrical Power System (EPS), (ii) a telecommunication system, (iii) a scientific payload, and (iv) an On-Board Computer (OBC) controlling the entire nanosatellite. The purpose of this master thesis is to develop the OBC of this nanosatellite. The work is divided into two main tasks.

The first one concerns the hardware of the OBC. It consists in selecting the components and assembling them to produce the OBC schematics. Once the schematics are done, the conception of a Printed Circuit Board (PCB) is also needed. For this task, particular attention must be paid to the choice of components. Indeed, previous OUFTI experiments have shown that it is important to choose components that are (i) resistant to the harsh conditions encountered in space, (ii) efficient in terms of power consumption.

The second task consists in a series of tests to check the proper functioning of some components. Some tests only require the reading of some voltages through external components such as voltmeters but most of the tests require a software. For that reason, a complete software has also to be realized. It is important for this software to be easily readable and well documented as the development of the nanosatellite will continue in the coming years.

# 1.2 CubeSat history and architecture

Traditional satellites are huge, heavy, and expensive. Thanks to the invention of microcontrollers, which integrate multiple components, and the reduction of Printed Circuit Board size, engineers were able to develop a new class of satellites, with lower size and weight, and therefore, with lower power consumption: the nanosatellites.

# 1.2.1 History

CubeSats are nanosatellites with specific characteristics. They are the result of a collaborative work carried out by two university professors, Jordi Puig-Suari, a professor at California Polytechnic State University (Cal Poly), and Bob Twiggs, a professor at Stanford University's Space Systems Development Laboratory (SSDL) [1]. Their aim was to make it possible for engineering students within their universities to work on space programs and so improve their training. To reach their objective, it was necessary to reduce considerably the size and cost of satellites. In 1999, they succeeded with the conception of the first CubeSat. And in 2003, the first CubeSat was launched.

CubeSats were first used within universities as educational tools. But now they are more and more popular in the satellite industry. As they are much smaller and considerably less expensive than conventional satellites, they give affordable access to space and offer a perfect solution for several industrial applications. Therefore, CubeSats are now developed by Government organizations as well as private firms worldwide. What makes CubeSats so popular is their standard size and modularity, which not only reduces production costs but also makes the launch process very efficient, as will be detailed below. In addition to this, as the production time is also greatly reduced, if something goes wrong, a whole mission does not have to be stopped for years, as is the case with traditional satellites.

# 1.2.2 Architecture

In 1999, the CubeSat standard was defined. The basic unit, called 1U, is a 10 cm cube with a maximum mass of 1,33 kg [1]. Thanks to its modularity, different units, based on the standard CubeSat unit (1U), can be combined and so form a larger structure (2U, 3U,...).

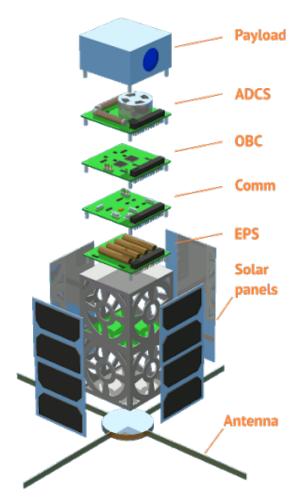

Standard dimensions make mass production possible. The use of commercial offthe-shelf (COTS) components for the structure and electronics of CubeSats considerably reduces both costs and production time. The launch of Cubesats is also greatly facilitated by their reduced volume, light weight, and standard dimensions. As a result, they can be installed in a specific container and launched from commercial space flights, which enables more frequent launches and at reduced costs since they can be shared. As it can be seen in Figure 1.2.1, the main components of a CubeSat are the following:

- **Payload**: it is the reason why the satellite is designed.

- Attitude Determination and Control System (ADCS): it controls the orientation of the satellite.

- **On-Board Computer (OBC)**: it is the central part of the CubeSat allowing the control of all the other subsystems.

- Communication system: it handles the external communications of the CubeSat.

- Electrical Power System (EPS): it is responsible for the adequate distribution of power to all the subsystems.

- Solar panels: they generate power and reload the EPS batteries.

- Antenna: it is used to send and receive CubeSat's communications.

Figure 1.2.1: Representation of the different parts of a CubeSat.

SOURCE: http://spacebillboard.com/mission/

# 1.2.3 On-Board Computer

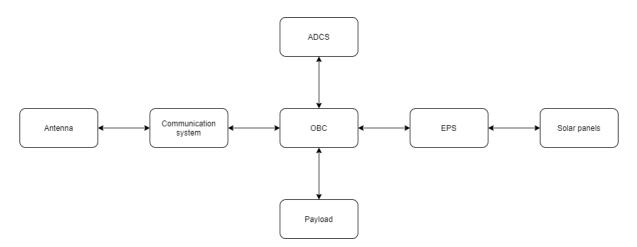

This thesis aims at developing the on-board computer of a CubeSat. The characteristics and role of the OBC will therefore be detailed in this section. During the mission, data will be collected through sensors and be processed. Communication with the ground station will also happen. Although they usually involve other sub-systems, all these operations are linked at some point to the OBC. An example is the voltage of the batteries which is frequently monitored by the EPS board and whose values are then stored in the OBC memory. The OBC can thus be represented at the center of a CubeSat diagram. This can be seen in Figure 1.2.2 with the subsystems introduced in the previous section.

Figure 1.2.2: Block diagram representing the interconnection between the main CubeSat subsystems.

Based on what has been explained above the main components required by an OBC will now be explored. First, a microcontroller is needed. The MCU can be viewed as the brain of the OBC and more generally of the CubeSat. It will handle the different communications happening inside the CubeSat and will process the data. The communications and data processing will be managed through a software that needs to be implemented. Then, connectors are needed to allow communication between the different subsystems and the OBC. It is also important to ensure that the power signals coming from the EPS board are well regulated in order to avoid a system failure. A monitoring of the power consumed by the OBC is also required as power is limited inside the CubeSat. Finally, the OBC will need to have memories in order to store data and the software. Different memory types will be required. Indeed, some information needs to be stored for a long time while other information will need to be processed quickly using volatile memory.

The components selected for the realization of the OBC of this project will be described in the next Chapter. Then, Chapter 3 will detail the software implemented in order to ensure that the OBC performs its operating tasks. Finally, Chapter 4 will present the tests that have been performed to ensure the good working of the OBC. But before that, a presentation of the space conditions that the CubeSat and thus the OBC will encounter is required in order to justify some of the choices made later.

# **1.3** Space conditions

CubeSats operate in Low Earth Orbit (LEO), which means at an altitude comprised between 160 km and 2.000 km. It is therefore important to take into account the particular space environment in LEO while choosing the components used in the OBC. Indeed, the temperature extremes and radiation that electronic systems will be subjected to may cause serious disturbances and failures [2].

In Low Earth Orbit, CubeSats will be exposed to temperature extremes, ranging from  $-55^{\circ}$  to  $+125^{\circ}$ C in a short period of time, putting a strain on all materials. This could affect the operational functionality of electronic components and limit their lifetime. It is thus essential to use components specially designed to withstand such a range of temperature extremes. Moreover, satellites in LEO are particularly affected by space radiation that can pass through a satellite and consequently damage electronic devices. Shielding can help to protect the components from radiation but it adds weight. Another solution is the use of radiation hardened or radiation tolerant components.

Space conditions in LEO will now be explained in more detail.

### 1.3.1 Temperature

Satellites orbiting the Earth move in and out of the sunlight. Therefore, they are submitted to extreme swings of temperature depending on whether they are facing the Sun or in the shadow. When they are in view of the Sun, as they are not protected by the Earth's atmosphere, they are subjected to solar radiation, and thus to very high temperatures. Thermal effects are also enhanced by the lack of convection in space. On the reverse, when satellites pass into the shadow of the Earth, the absence of atmosphere leads to rapid cooling as a result of the lack of energy being absorbed and of the thermal energy released by the satellites. It is therefore important to use electronic equipment that can withstand these temperature cycles.

## 1.3.2 Radiation

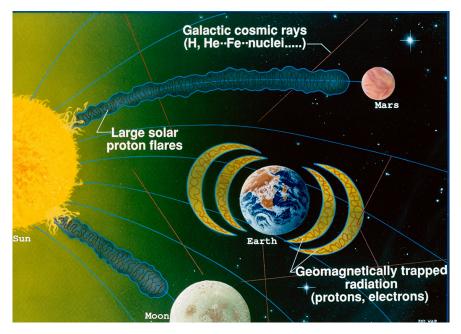

There are three main sources of ionizing radiation that can affect CubeSats and their electronic components. They are depicted in Figure 1.3.1.

Galactic Cosmic Rays (GCR) are high energy protons and heavy ions which are constantly bombarding the Earth. These particles originate outside the solar system. They are made up of atomic nuclei that have been stripped of their surrounding electrons and that are moving almost at the speed of light. These high-energy particles can alter components in electronic integrated circuits.

Energetic solar particles emanate from solar flares and coronal mass ejections. These events occur from time to time on the surface of the Sun. They are unpredictable. During these giant explosions, a large number of particles (protons, electrons, X-rays, and gamma rays) are released into space and can cause light to severe damage to electrical components. These are known as Solar Particle Events (SPE).

Trapped particles are highly charged particles, emanating mainly from the Solar Wind. They are trapped by the Earth's magnetic field in the Van Allen belts. Over the South Atlantic Ocean, there is a magnetic field anomaly. This region of weaker magnetism is called the South Atlantic Anomaly (SAA). Because the axis of the magnetic field is slightly offset from the one of the Earth, the inner belt is closer to the Earth's surface in this area. This weak point allows charged particles, mainly protons and electrons, to fall closer to the ground and reach satellites operating in LEO. As a result, when they pass through this zone, as CubeSats often do, they are exposed to particularly intense radiation.

Figure 1.3.1: Main sources of space radiation in LEO.

#### SOURCE : https://www.nasa.gov/audience/foreducators/stem-on-station/ learning\_launchers\_radiation

Electronic devices are impacted by space radiation in two different ways. Indeed, radiation effects can be either cumulative or due to a single event. That will now be described.

Total Ionizing Dose (TID): Electronic devices are subject to the long-term effects of radiation and are being deteriorated by the charges they have accumulated.

Single-Event Effects (SEE): A single charged particle hits and ionizes the material, causing a current pulse that can damage the component. The effects can be reversible (soft errors, which can be mitigated by a reset or an erase operation, for instance) or non-reversible (hard error).

There are different types of SEEs, depending on the location of the hit and its intensity.

The two more common are:

- Single-Event Upset (SEU): In this case an ionizing particle from the radiation reaches a sensitive area of the circuit such as the memory and creates a change of state (bitflips).

- Single-Event Latchup (SEL): An ionizing particle from the radiation creates an overcurrent within the device which can cause irreparable damage if not directly addressed.

# 1.4 Power management

Satellites get all their power from solar panels. When exposed to the Sun, the solar arrays transfer energy to the EPS. Part of this energy is used for operations and part for recharging the batteries. The batteries are required to operate during eclipses, when the CubeSat is in the shadow of the Earth, or to deal with power peaks that are beyond what the solar cells can provide. Due to their small size, CubeSats have a reduced surface area for solar arrays and strict constraints on the subsystem components, including the EPS, that can be installed. As CubeSats are increasingly used for more sophisticated applications, the power needs are constantly growing. Even with the advent of deployable solar panels and more efficient batteries, moderate use and correct management of power are thus crucial. A negative power budget could lead to the failure of a CubeSat mission. In short, energy is precious on a Cubesat. Particular attention must therefore be paid to the choice of low-power components.

# Chapter 2 Hardware design

The development of the on-board computer starts with the creation of its PCB. To this end, the components constituting the OBC have to be selected and the schematics have to be realized. This chapter will present this hardware part of the OBC's conception. It will start with an explanation about the thinking that was made in order to choose the microcontroller. Then, the chosen MCU will be investigated and some of its characteristics will be detailed. After having presented the MCU, the other components constituting the OBC will be explored. This exploration will start with a review of all the different memory components that have been placed on the OBC. Then, the connectors and oscillators that have been used will be detailed. The last components that will be presented in this chapter are those used to monitor the power of the OBC. Finally, the chapter will end with a presentation of the final OBC's PCB.

## 2.1 Choice of the microcontroller

The microcontroller is the central part of the OBC. It is therefore important to choose it with particular attention. Indeed, a malfunction of the MCU will lead to the failure of the OBC, and thus, of the whole nanosatellite. The previous chapter introduced the main difficulties encountered in space. Research has been conducted in order to find a MCU consuming relatively low power and being able to survive in the harsh space environment. Two main challenges were encountered during this procedure. First, radiation-resistant MCUs generally consume much more power than more basic MCUs. Second, the price of MCUs capable of surviving in space is much higher than that of MCUs designed for use on Earth. The second point is particularly problematic for the development of a university CubeSat. Indeed, the budget is not unlimited and some tests must be done this year while the OBC will still evolve before being launched one day. It is thus impossible to spend hundreds of euros in order to get a MCU to test the OBC's PCB this year and to have to buy a new one next year for the updated PCB.

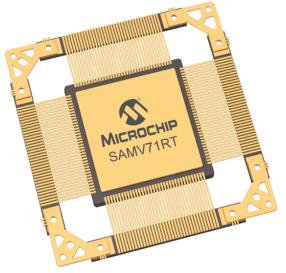

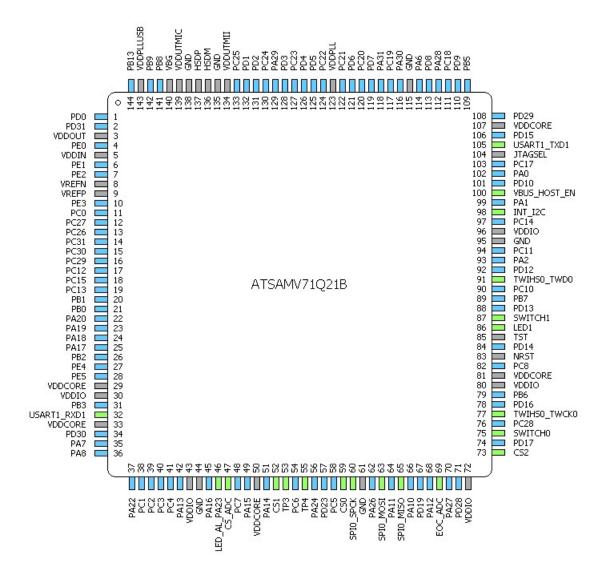

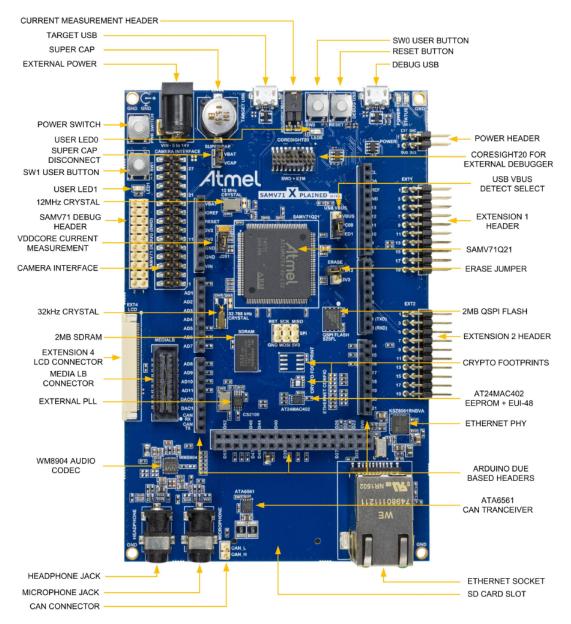

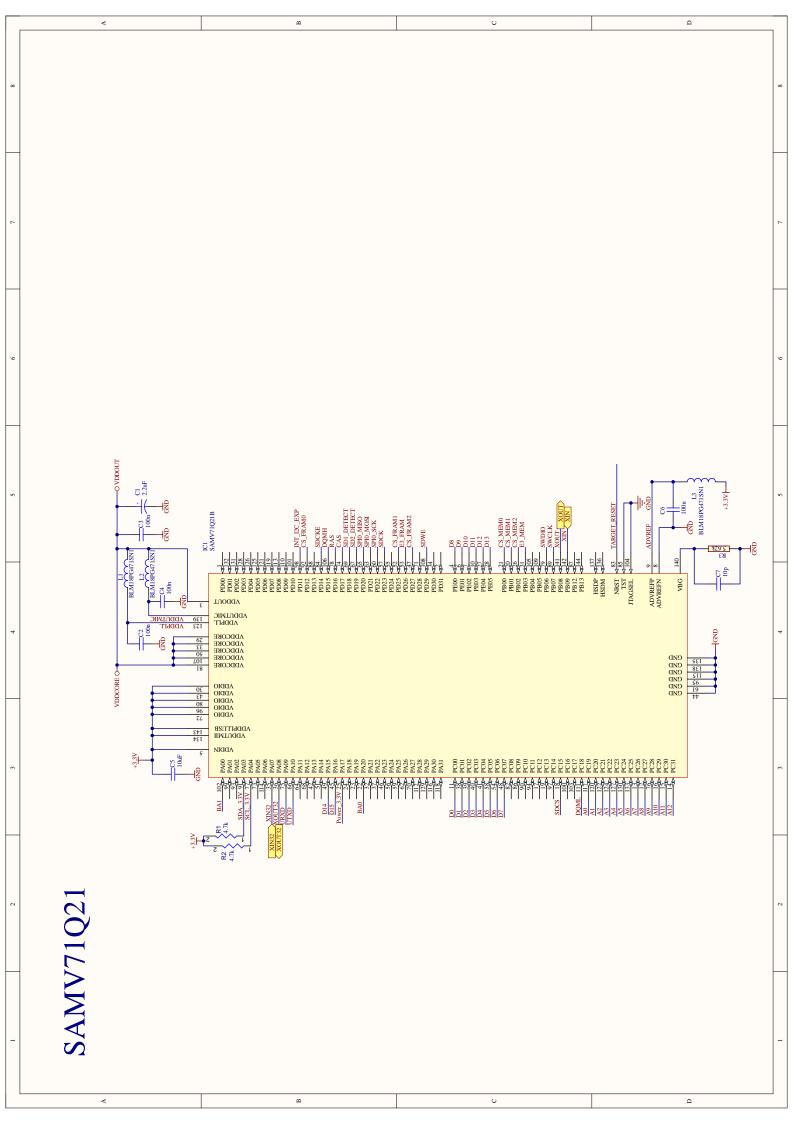

For the reasons mentioned above, the choice has been made to develop the OBC around the SAMV71 MCUs. This choice is motivated by the fact that three different versions of this MCU exist [3]. They are shown in Figure 2.1.1. *Microchip* has developed the SAMV71 to be Arm<sup>®</sup>-based MCUs able to operate properly in space. The standard version, the ATSAMV71Q21, is a COTS device and costs only a few dozen euros. The second one, the SAMV71Q21RT, is the radiation-tolerant version of the ATSAMV71Q21. The third one, the SAMRH71, is the radiation-hardened MCU based on the standard

one. It is also worth noting that a development board made around the standard MCU version is available.

(a) ATSAMV71Q21, the standard version of the SAMV71

(b) ATSAMV71Q21RT, the radiation-tolerant version of the SAMV71

(c) SAMRH71, the radiation-hardened version of the SAMV71

Figure 2.1.1: The three versions of the Arm<sup>®</sup>-based SAMV71 developed by *Microchip*.

## SOURCES:

- (a) https://www.microchip.com/wwwproducts/en/ATSAMV71Q21

- $(b)\ https://www.microchip.com/wwwproducts/en/SAMV71Q21RT$

- (c) https://www.microchip.com/wwwproducts/en/SAMRH71

The development board has been used to implement the software and to realize the tests performed during this thesis. For the future tests, the standard version will be placed in the designed OBC's PCB. Finally, the radiation-tolerant version will replace the standard version before the launch of the nanosatellite. The transition from the standard version to the radiation-tolerant version is straightforward since the masks of the latter are the same as those of the former. Some little modifications should be made

to adapt the software to the radiation-hardened version. However, they are negligible compared to the gain obtained from developing the software on the standard version. Moreover, the radiation-tolerant MCU will be the one used when the nanosatellite will be launched. Firstly, because it is well adapted to operate in LEO, which is precisely where the CubeSats operate. Secondly, because it is way cheaper than the radiation-hardened version. The characteristics of the three versions will now be detailed in the next section.

## 2.1.1 SAMV71

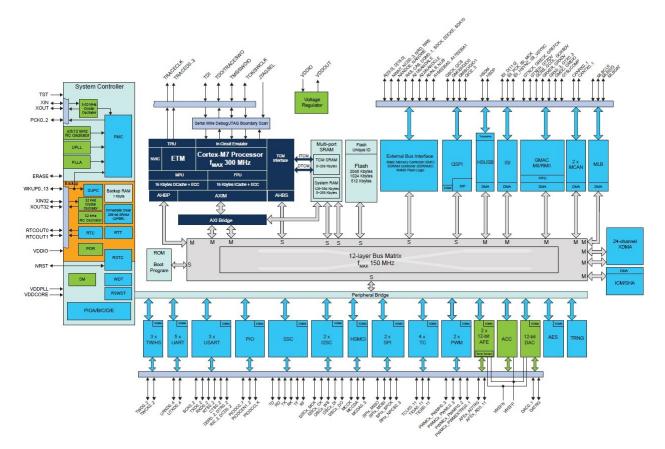

As already stated, one of the reasons for which the SAMV71 has been chosen is because it exists in three different versions. Before presenting the space characteristics of the radiation-tolerant and radiation-hardened versions, the main characteristics of the standard version will be described. Figure 2.1.2 represents the block diagram of the ATSAMV71Q21 microcontroller [4]. This gives an overview of the main functions of the MCU in one picture.

Figure 2.1.2: Block diagram of the ATSAMV71Q21 [4].

#### 2.1.1.1 Core

The main component of a microcontroller is its core. The ATSAMV71Q21 contains an ARM<sup>®</sup> Cortex<sup>®</sup>-M7 core processor running at up to 300 MHz [4]. In addition to being very powerful, this processor offers great flexibility and consumes relatively low power, which makes it ideal for this application. Moreover, it supports Real Time Operating System (RTOS) and there exists a lot of third party tools working with it. One of the main

properties of the Cortex-M7 is the presence of a six-stage, in-order super-scalar pipeline that enables dual-issue processing of instructions. This feature allows the processor to run two instructions in parallel. Another interesting point is that the latency of the Cortex-M7 processor is reduced thanks to the fact that memory accesses are interleaved with computation.

#### 2.1.1.2 Memories

The ATSAMV71Q21 has different memories. They will now be detailed in turn [4].

#### Internal SRAM

The MCU contains 384 Kbytes of high speed Static Random Access Memory (SRAM). Four priority levels are available to improve processor efficiency without compromising the high-priority latency-critical requests. Some features make possible to optimize the SRAM performances. First, it is equipped with a Multi-Port SRAM with four ports to ensure optimal bandwidth and latency. Then, the MCU is equipped with an SRAM controller. This one allows the minimization of latency by giving priority to the most urgent requests without neglecting the less urgent ones. Indeed, the latter are executed at the latest during the next cycle.

#### Tightly Coupled Memory (TCM) Interface

A tightly coupled memory (TCM) is integrated into the MCU. Unlike other memories that are accessed at bus speed, TCM operates at processor speed. TCM is therefore used to store critical parts of the code that require the fastest possible processing. It is divided into two parts. The instruction tightly coupled memory (ITCM) is a single 64-bit interface that allows the processor to fetch two 32-bit instructions in a single access and thus use the dual issue property of the pipeline. The data tightly coupled memory (DTCM) consists of two interleaved 32-bit interfaces that makes possible the optimization of concurrent accesses. Finally, the software allows both the configuration of the TCM in 4 different modes and the activation or deactivation of the ITCM and DTCM.

#### Internal ROM

The SAMV71Q21 embeds an internal Read Only Memory (ROM). It is used for the SAM Boot Assistant, In-Application Programming and Fast Flash Programming Interface functions.

#### Backup SRAM

The MCU embeds 1 Kbytes of backup SRAM. This one is only accessible in 32-bit words. A power switch ensures that the contents of the backup SRAM are retained. Indeed, in normal mode, it is powered by VDDCORE. However, in backup mode, when VDDCORE is turned off, the power switch allows the backup SRAM to be powered by VDDIO. To save power, the power switch can be turned off.

#### Flash Memories

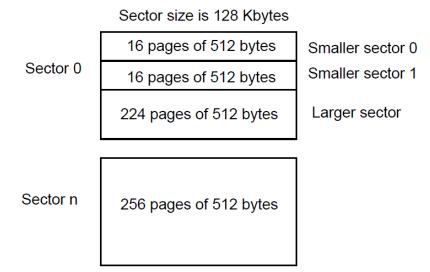

The SAMV71 embeds 2084 Kbytes of internal Flash. It is organized in sectors of 128 Kbytes in size. Each sector is organized in pages of 512 bytes. Figure 2.1.3 represents the general organization of the internal Flash. It is interesting to note that the first sector is divided into three smaller sectors, two 8 Kbyte sectors, and one 112 Kbyte sector.

Figure 2.1.3: Flash Sector Organization [4].

The MCU has an Enhanced Embedded Flash Controller that manages the Flash memory. Thanks to it, it is possible to read the Flash and to write the write buffer. It also provides the interface of the Flash block. It uses a complete set of commands to manage the programming, erasing, locking and unlocking sequences of the Flash.

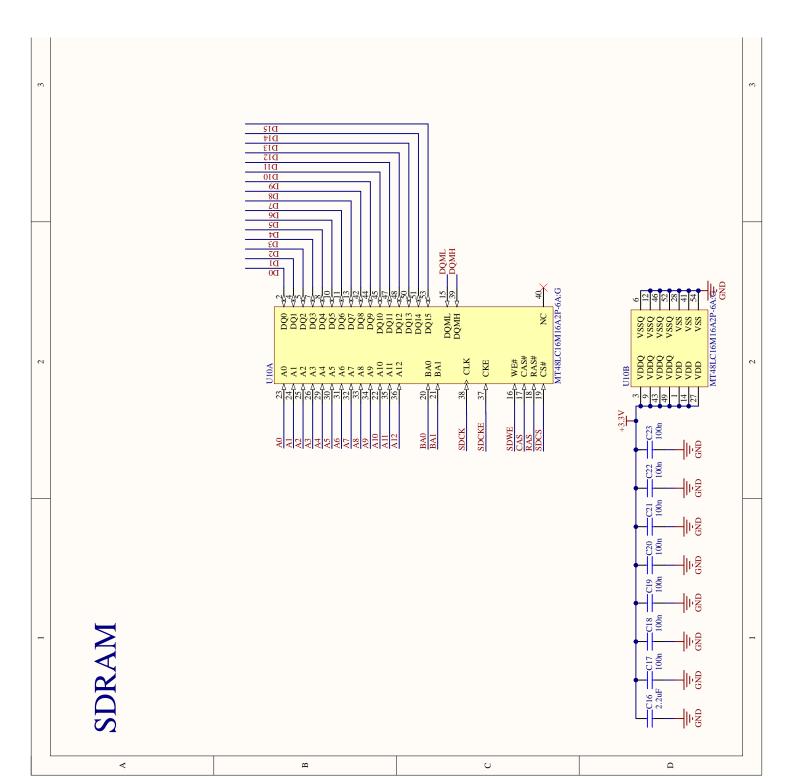

#### External Memories

Finally, the MCU includes an Synchronous Dynamic Random Access Memory Controller (SDRAMC). This controller increases the memory capacity by allowing an external 16-bit DRAM device to be connected. The MCU also has an external bus interface giving the possibility to use external memories. All external memories that have been used will be presented in the next section.

#### 2.1.1.3 Peripherals

The ATSAMV71Q21 has many peripherals. Therefore, only the most useful ones are detailed below [4].

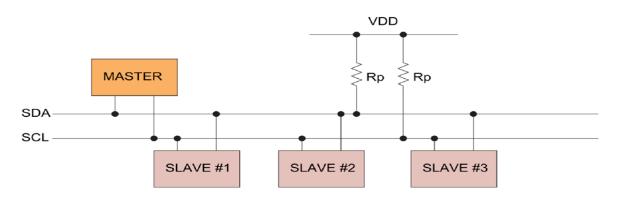

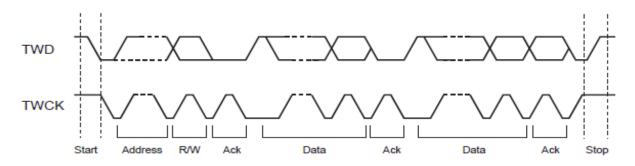

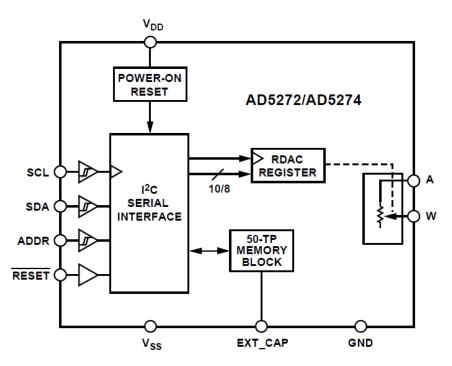

#### The Two-wire Interface

There are three different two-wire interfaces (TWI) on the SAMV71Q21. The TWI is a two-wire bus used for data transfer that is based on a byte-oriented format. The two wires correspond to a clock line and a data line. TWI is I2C compatible and works with two-wire serial Electrically Erasable Programmable Read-Only Memory (EEPROM). An I2C bus has been implemented in the software, its operation will thus be explained in more detail in the following Chapter. TWI can operate at speeds up to 400 kbit/s in fast mode and up to 3.4 Mbit/s in high-speed slave mode only. It uses a configurable baud rate generator to match the clock rates of a wide range of external components.

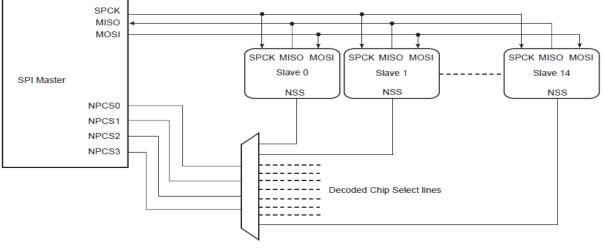

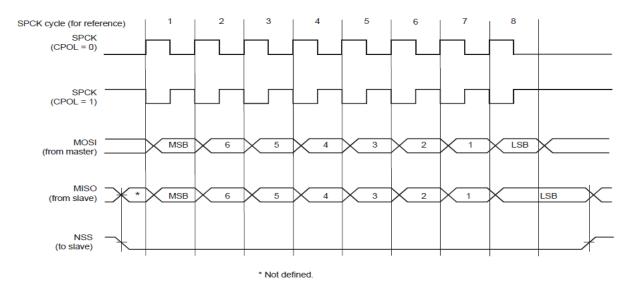

#### Serial Peripheral Interfaces

Two Serial Peripheral Interfaces (SPI) bus are present on the MCU. It is a synchronous communication system requiring only 4 wires to perform data transfers with external devices. The SPI operating speed is generally way higher than the TWI one. As for the I2C bus, a complete description of the functioning of the SPI bus is presented in the next Chapter.

#### **Analog Front-End Controllers**

The MCU contains two Analog Front-End Controllers (AFEC) that rely on an Analog Front-End cell containing various modules. It can be used to perform different types of data conversion either in differential or single-ended mode and it has a programmable gain stage. The conversion results range from 0V to VREFP which is the positive voltage reference. It has a standard resolution of 12-bit which can be extended up to 16-bit. A digital error correction circuit offers the possibility to reduce integral non-linearity and differential non-linearity errors. This circuit is based on the multi-bit redundant signed digit (RSD) algorithm. The Analog-to-Digital Converter (ADC) of the AFEC has been used in the software of the OBC and some clarifications about it will be given in the next Chapter.

#### $\mathbf{USART}/\mathbf{UART}$

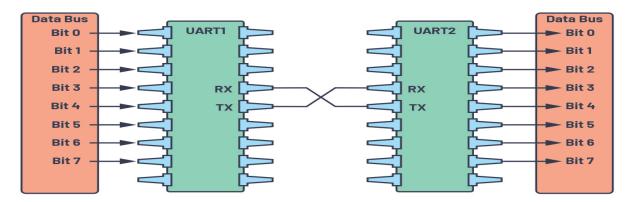

Three Universal Synchronous Asynchronous Receiver Transceiver (USART) and five Universal Asynchronous Receiver Transmitter (UART) are available on the MCU. The UART enables asynchronous serial communications while the USART enables synchronous and asynchronous serial communications. The remaining part of this explanation will focus on the UART since it is a more widespread system. UART is a serial device-to-device hardware communication protocol. Data is transferred bit by bit using only two wires for its transmitting and receiving ends. Those two wires are Transmitter (Tx) and Receiver (Rx). The data bus on the transmitter and receiver side transfers the data in parallel. However, as in the UART data is sent and received serially, bit by bit, on a single line, it must be converted at the beginning and end of the transfer. This is shown in Figure 2.1.4.

Figure 2.1.4: Representation of UART with data bus [5].

During the development of this thesis, this communication system has only been used as a debugging tool to print messages on the terminal. However, as it is a very useful communication system it will be used in future works based on this one, for example, to communicate with the communication board.

#### **Controller Area Network**

Two Master Controller Area Networks (MCAN) can be used on the MCU. CAN is a communication bus standard that allows communication between multiple devices without a host computer. It is a message-based protocol that transmits data sequentially. When multiple devices attempt to transmit at the same time, only the device with the highest priority continues to transmit. Eventually, all devices connected to the bus receive the data, even the sending device.

#### Real-Time Clock

The Real-Time Clock (RTC) device is developed for very low power consumption. A crystal oscillator provides an accurate 32.768 kHz external clock that allows the RTC to operate perfectly. The oscillator works when the power consumption is critical and the MCU is in power saving mode. The choice of the crystal must therefore be made taking into account its power consumption as well as the effects of temperature on its oscillation frequency. An interesting feature of the RTC is the possibility it offers to program a periodic interrupt. Finally, it also has a complete clock with an alarm and a Gregorian or Persian calendar.

#### **Real-Time Timer**

The Real-Time Timer (RTT) is built around a 32-bit counter. It is used to generate a periodic interrupt when the user-programmed value in the counter is reached. In its standard configuration, the RTT uses the 16-bit programmable prescaler from the 32 kHz slow clock. However, it can also be configured to operate with the 1Hz RTC signal to take advantage of the 1Hz calibrated clock. Finally, when it is only necessary to count elapsed seconds, it is possible to disable the slow clock source to reduce power consumption.

#### Power Management Controller

As explained in the Introduction, power is limited within the CubeSat. The Power Management Controller (PMC) optimizes power consumption by monitoring all system and user peripheral clocks. The PMC can actually enable and disable the clock inputs of both the devices connected to the MCU and the Cortex-M7 processor. The MCU is equipped with two oscillators that can act as clock signals, a slow RC oscillator, and a 32.768 kHz crystal oscillator. To optimize power consumption only one of the two oscillators is used while the other is disabled. By default, at startup, the main RC oscillator operating at 12 MHz is enabled. Finally, one of the main interesting features of the PMC is that it can detect failures of the main crystal oscillator.

#### 2.1.1.4 Other characteristics

The ATSAMV71Q21 possesses some very interesting characteristics that haven't been detailed yet. First, it has an embedded voltage regulator for single-supply operation [4]. In other terms, that means that the microcontroller only needs a single supply voltage of 3.3V. The embedded voltage regulator will convert this 3.3 V tension to a 1.23V tension for the parts of the microcontroller needing it.

As far as reliability is concerned, the MCU features a Power-on-Reset, a Brown-out Detector, a Watchdog Timer (WDT) as well as a Reinforced Safety Watchdog Timer (RSWDT) working independently from the WDT for increased safety. The last two mentioned were used in this project and more details about them will be given in the next chapter.

Finally, it is worth noting that the ATSAMV71Q21 is composed of 114 I/O lines with external interrupt capability.

#### 2.1.1.5 Space characteristics

The second version of the microcontroller, the SAMV71Q21RT [6] is the radiationtolerant version of the SAMV71. This version is perfectly suited for CubeSats as they operate in LEO. It should therefore be the version of the MCU used in the final design of the OBC that will be sent to space. The first improvement achieved by this device is that it can work in temperatures ranging from -55 to 125°C while the operating temperatures of the ATSAMV71Q21 goe from -40 to 105°C. Besides being able to operate in a wider temperature range than the standard version, the radiation-tolerant version has the following characteristics in terms of radiation tolerance:

- It ensures an accumulated TID of 30Krad (Si) with latch-up immunity;

- It is nondestructive against heavy ions;

- $\bullet$  It is completely immune to SEL below a Linear Energy Transfer (LET) Threshold of 60 MeV.cm2 /mg at 125°C.

Finally, the third version, the SAMRH71 [7] is the radiation hardened version of the SAMV71. Even if this version is more suited for deep space applications, its main characteristics will be given. It operates in the same temperature range as the radiation-tolerant version and has the following radiation performances:

- It ensures an accumulated TID of more than 100 Krad (Si);

- It ensures no SEU below an LET Threshold of 62.5 MeV.cm2/mg at 125°C;

- It includes SpaceWire interface with two SpaceWire ports with Integrated RMAP support and embedded SpaceWire router.

# 2.2 Selection of the other components

Now that the microcontroller of the OBC has been presented, the other components required by the OBC will be explored. These include the external components required