https://matheo.uliege.be

## Master thesis : Performance evaluation and optimization of a GPU-enabled Discontinuous Galerkin code

Auteur: D'Antonio, Marco

https://lib.uliege.be

Promoteur(s): Geuzaine, Christophe

Faculté : Faculté des Sciences appliquées

Diplôme: Cours supplémentaires destinés aux étudiants d'échange (Erasmus, ...)

Année académique : 2021-2022

URI/URL: http://hdl.handle.net/2268.2/15924

#### Avertissement à l'attention des usagers :

Tous les documents placés en accès ouvert sur le site le site MatheO sont protégés par le droit d'auteur. Conformément aux principes énoncés par la "Budapest Open Access Initiative" (BOAI, 2002), l'utilisateur du site peut lire, télécharger, copier, transmettre, imprimer, chercher ou faire un lien vers le texte intégral de ces documents, les disséquer pour les indexer, s'en servir de données pour un logiciel, ou s'en servir à toute autre fin légale (ou prévue par la réglementation relative au droit d'auteur). Toute utilisation du document à des fins commerciales est strictement interdite.

Par ailleurs, l'utilisateur s'engage à respecter les droits moraux de l'auteur, principalement le droit à l'intégrité de l'oeuvre et le droit de paternité et ce dans toute utilisation que l'utilisateur entreprend. Ainsi, à titre d'exemple, lorsqu'il reproduira un document par extrait ou dans son intégralité, l'utilisateur citera de manière complète les sources telles que mentionnées ci-dessus. Toute utilisation non explicitement autorisée ci-avant (telle que par exemple, la modification du document ou son résumé) nécessite l'autorisation préalable et expresse des auteurs ou de leurs ayants droit.

### University of Salerno - Department of Computer Science University of Liège - School of Engineering and Computer Science

Master's Degree in Computer Science

# Performance analysis and optimization of a GPU-enabled Discontinuous Galerkin solver

Master's thesis carried out to obtain the degree of Master of Science in Computer Science by Marco D'Antonio

Supervisors Candidate

Prof. Filomena Ferrucci Prof. Christophe Geuzaine Matteo Cicuttin, Ph.D.

Marco D'Antonio - 0522500958

Academic Year 2021-2022

## Contents

| In | Introduction 4                    |        |                                                     |    |  |  |  |

|----|-----------------------------------|--------|-----------------------------------------------------|----|--|--|--|

| 1  | Physical and mathematical context |        |                                                     |    |  |  |  |

|    | 1.1                               | Vector | r calculus                                          | 6  |  |  |  |

|    | 1.2                               | Maxw   | rell's equations                                    | 7  |  |  |  |

|    | 1.3                               | Nume   | rical solution of PDEs                              | 10 |  |  |  |

|    |                                   | 1.3.1  | Computational domain and meshes                     | 10 |  |  |  |

|    |                                   | 1.3.2  | Conservation laws in one dimension                  | 11 |  |  |  |

|    |                                   | 1.3.3  | The Finite Volume Method                            | 12 |  |  |  |

|    |                                   | 1.3.4  | The Discontinuous Galerkin method                   | 14 |  |  |  |

|    |                                   |        | Computational properties of DG                      | 17 |  |  |  |

|    | 1.4                               | The D  | Discontinuous Galerkin method for Maxwell equations | 19 |  |  |  |

|    |                                   |        | Time integration                                    | 23 |  |  |  |

| 2  | Gra                               | phics  | Processing Units                                    | 24 |  |  |  |

|    | 2.1                               | Archit | tecture fundamentals                                | 25 |  |  |  |

|    |                                   | 2.1.1  | CUDA Compute Capability                             | 26 |  |  |  |

|    |                                   | 2.1.2  | Thread execution model                              | 27 |  |  |  |

|    |                                   | 2.1.3  | GPU memories                                        | 29 |  |  |  |

|    | 2.2                               | Perfor | mance optimization                                  | 31 |  |  |  |

|    |                                   | 2.2.1  | Maximize utilization                                | 32 |  |  |  |

|    |                                   | 2.2.2  | Maximize memory throughput                          | 32 |  |  |  |

|    |                                   | 2.2.3  | Maximize instruction throughput                     | 35 |  |  |  |

| 3  | Dis                               | contin | uous Galerkin solver                                | 37 |  |  |  |

|    | 3.1                               | Solver | rs on GPU: state of art                             | 37 |  |  |  |

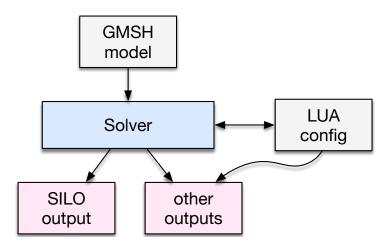

|    | 3.2                               | The G  | Gmsh DG solver                                      | 39 |  |  |  |

|    |                                   | 3.2.1  | The libgmshdg layer                                 | 41 |  |  |  |

|    |                                   | 3.2.2  | The Maxwell solver module                           | 43 |  |  |  |

|    |                                   |        | Data layout                                         | 43 |  |  |  |

|    |                                   |        | Volumetric path                                     | 44 |  |  |  |

|    |                                   |        | Flux path                                           | 44 |  |  |  |

|    |                                   | 3.2.3  | Computational bounds                                | 45 |  |  |  |

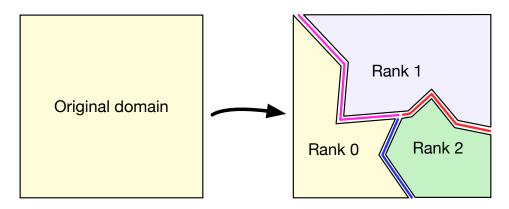

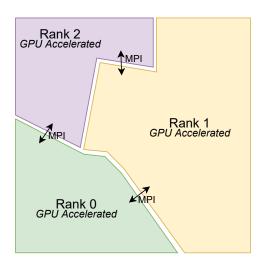

|    | 3 3                               | Coare  | e- and fine-grained parallelization                 | 17 |  |  |  |

| 4            | Pro                        | $\mathbf{posed}$ | optimizations                      | 50  |  |  |  |  |  |

|--------------|----------------------------|------------------|------------------------------------|-----|--|--|--|--|--|

|              | 4.1                        | Curls            | optimization                       | 50  |  |  |  |  |  |

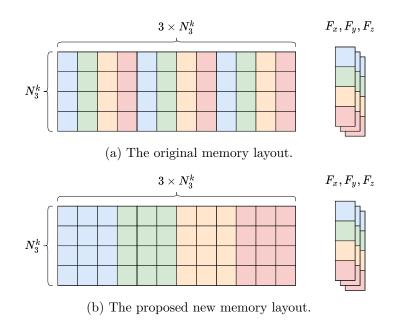

|              | 4.2                        | Propo            | sal: differentiation matrix layout | 52  |  |  |  |  |  |

|              | 4.3                        | Propo            | sal: fluxes lifting optimization   | 54  |  |  |  |  |  |

|              | 4.4                        | One-sl           | hot lifting and jumps              | 55  |  |  |  |  |  |

| 5            | Gm                         | sh DG            | performance analysis               | 56  |  |  |  |  |  |

|              | 5.1                        | Profili          | ng infrastructure                  | 56  |  |  |  |  |  |

|              | 5.2                        | Kerne            | ls analysis                        | 58  |  |  |  |  |  |

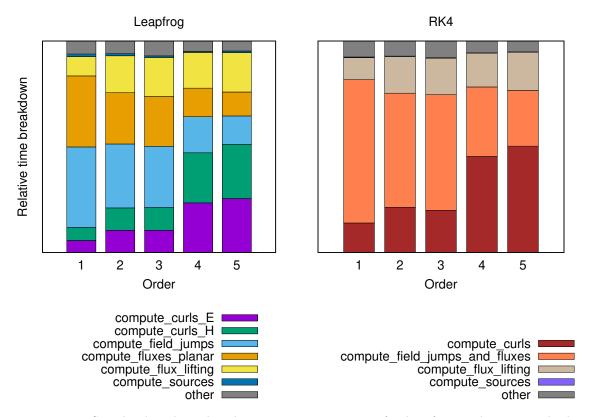

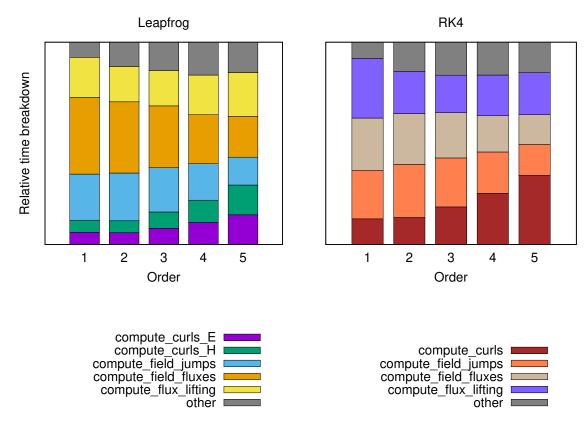

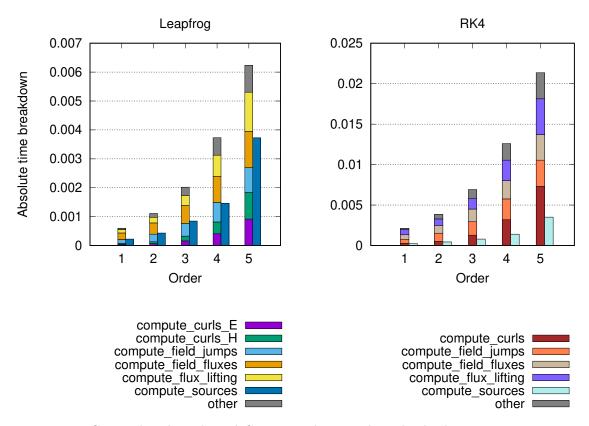

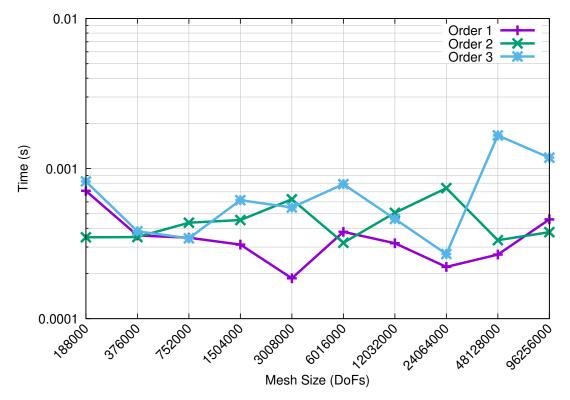

|              |                            | 5.2.1            | Time comparison                    | 58  |  |  |  |  |  |

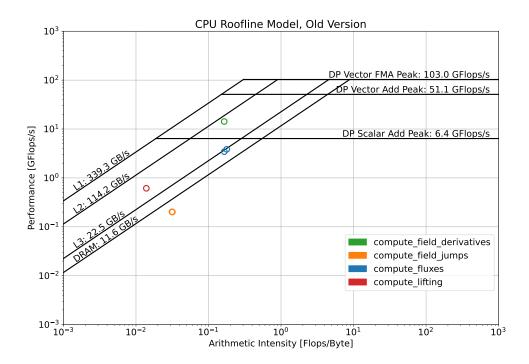

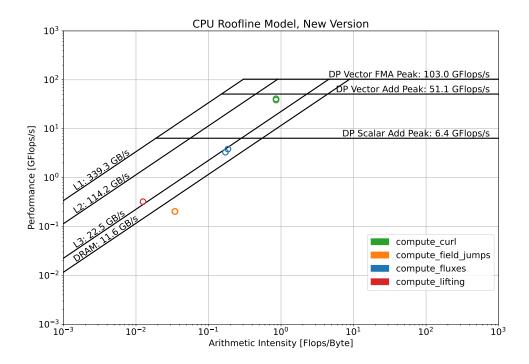

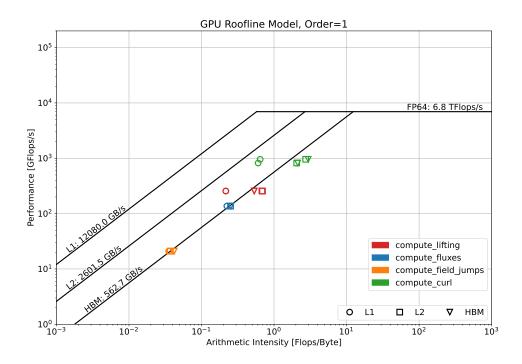

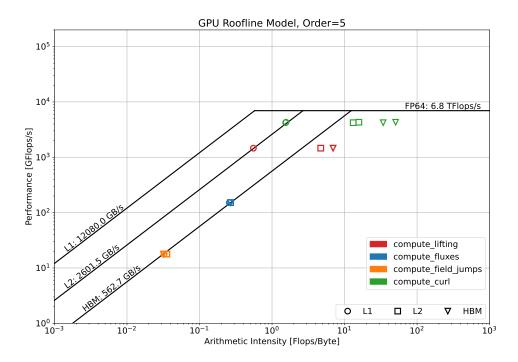

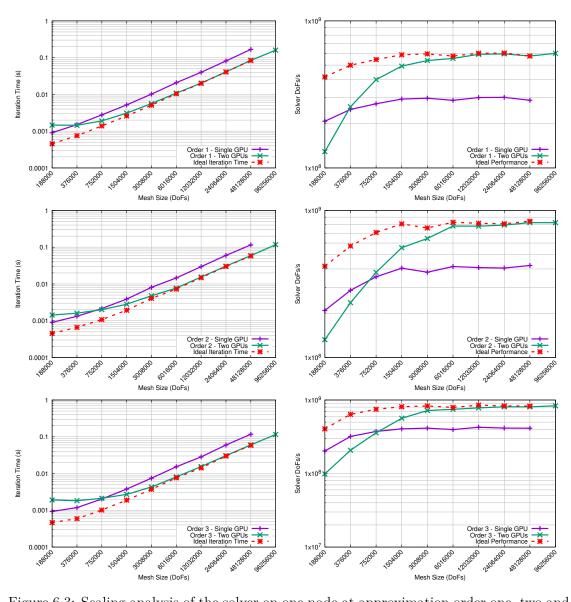

|              |                            | 5.2.2            | Roofline analysis                  | 61  |  |  |  |  |  |

|              | 5.3                        | Solver           | scaling                            | 66  |  |  |  |  |  |

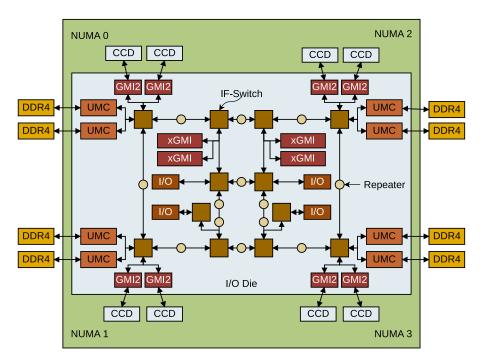

|              |                            | 5.3.1            | Platform details                   | 69  |  |  |  |  |  |

|              |                            | 5.3.2            | Execution configuration            | 72  |  |  |  |  |  |

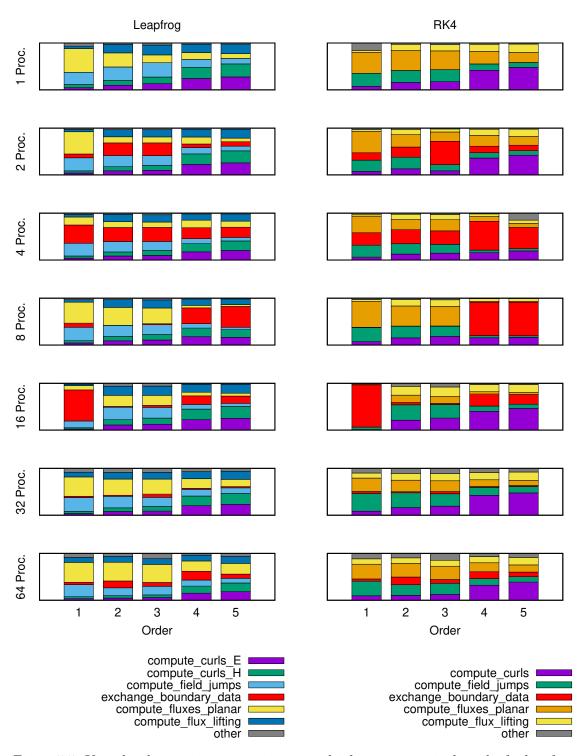

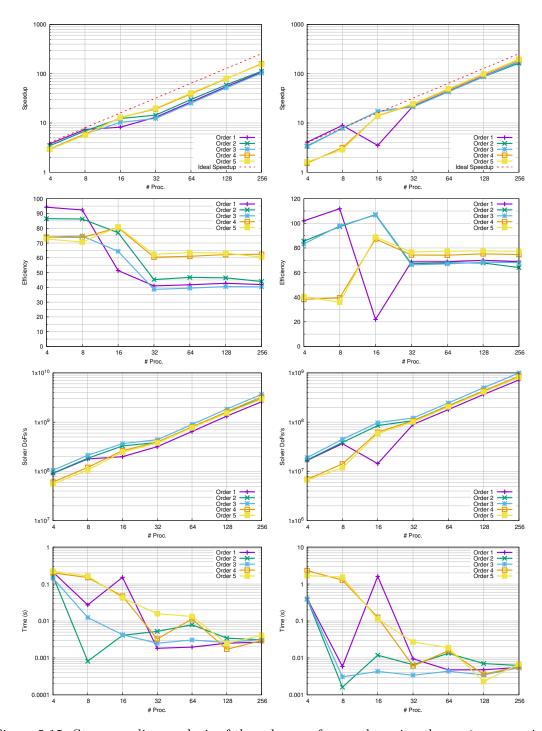

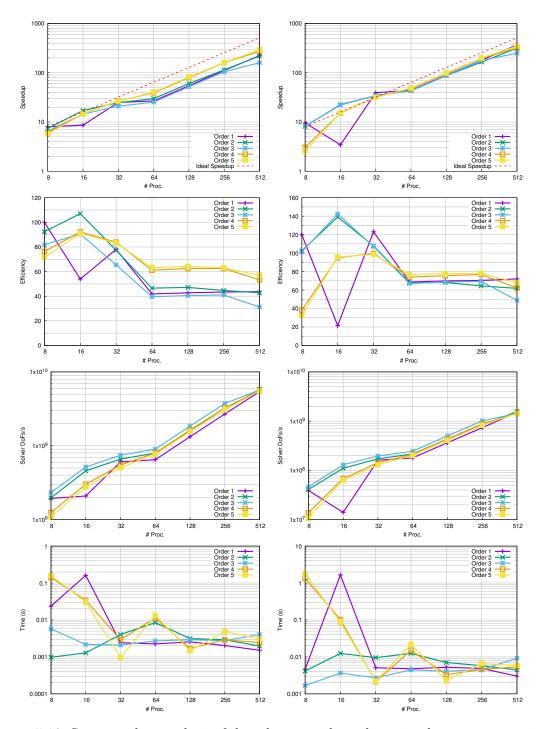

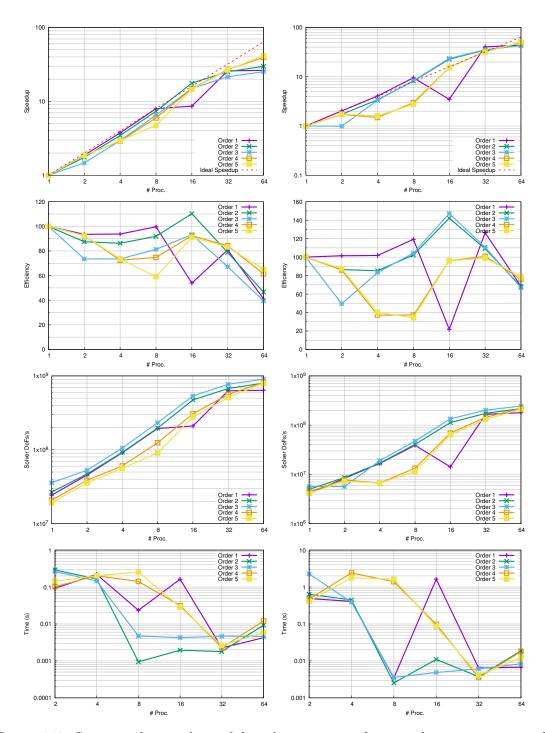

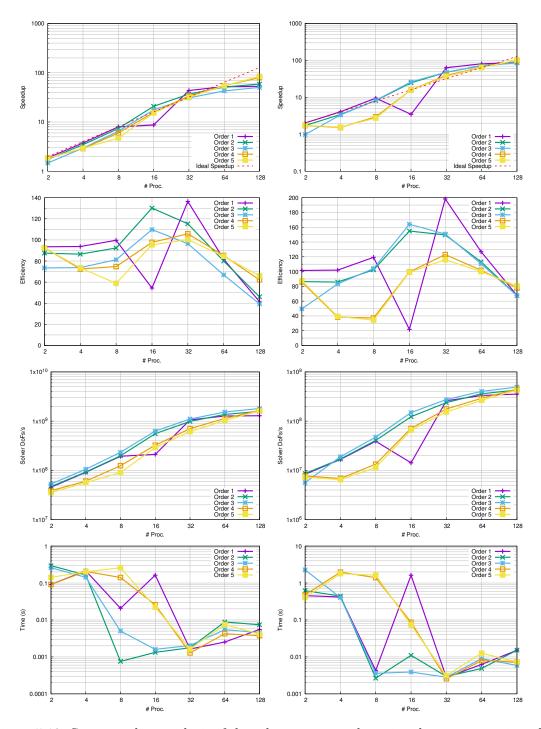

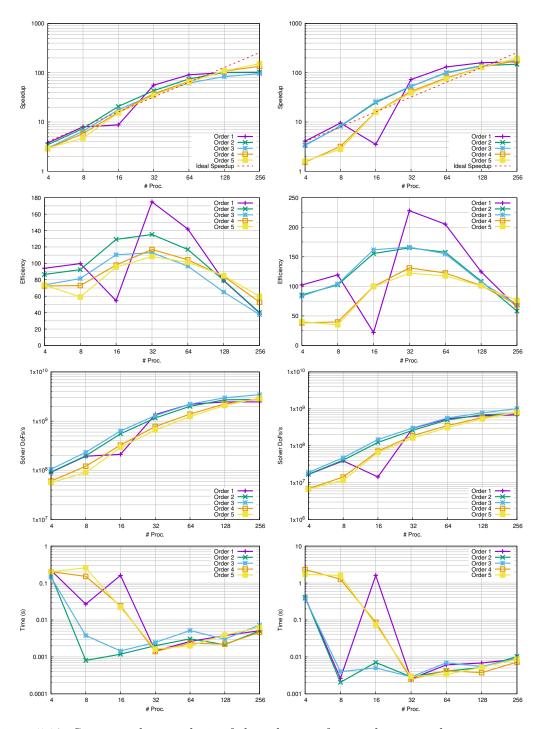

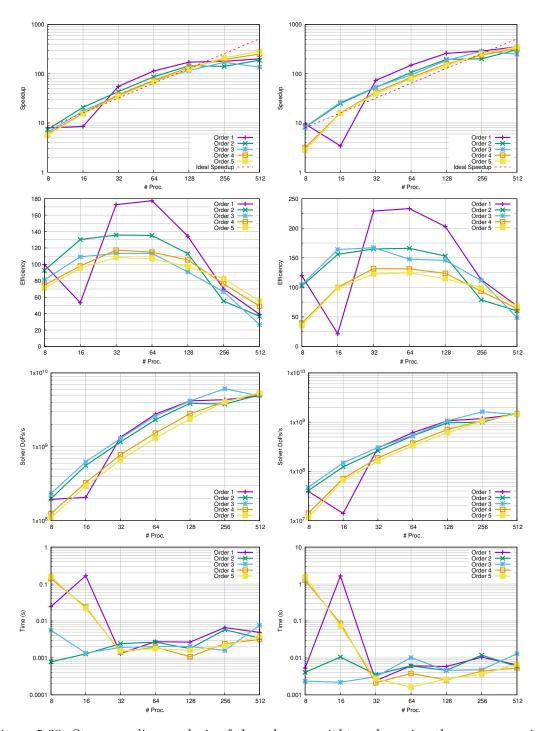

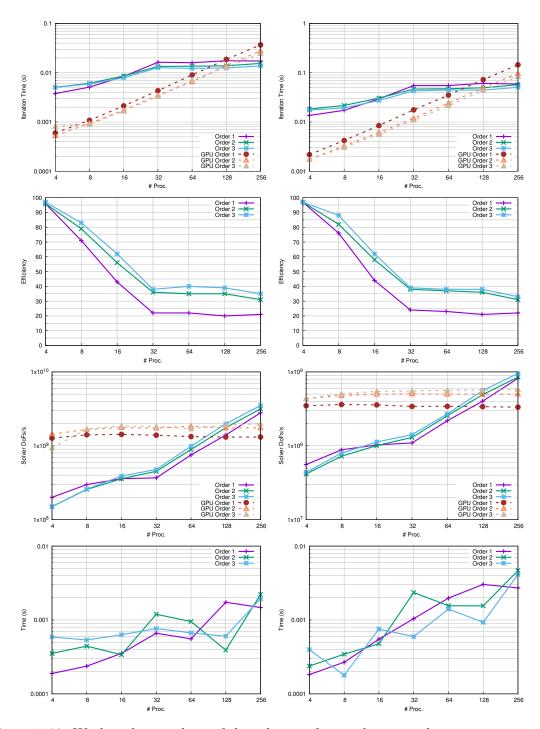

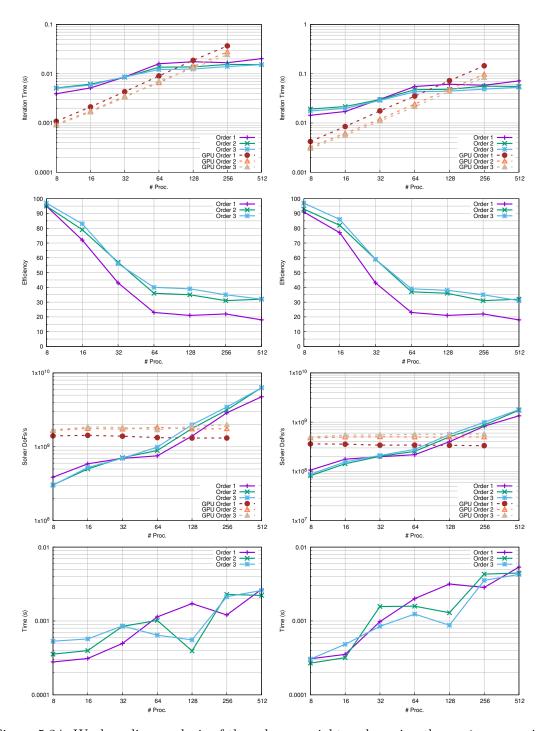

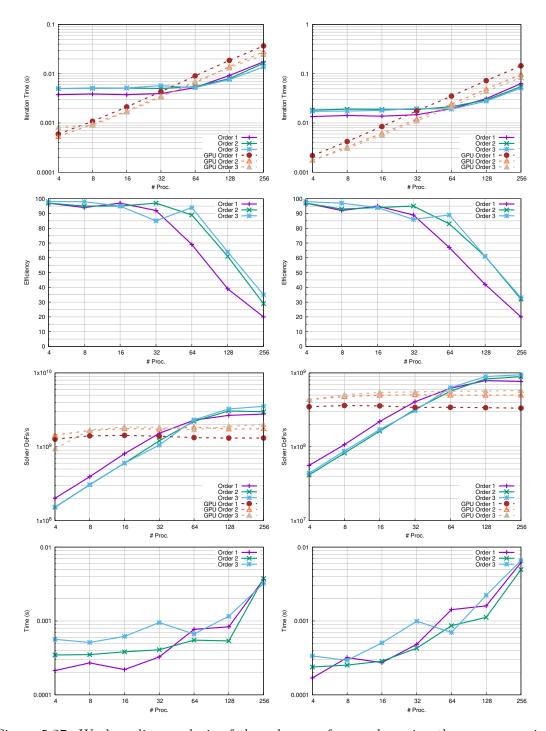

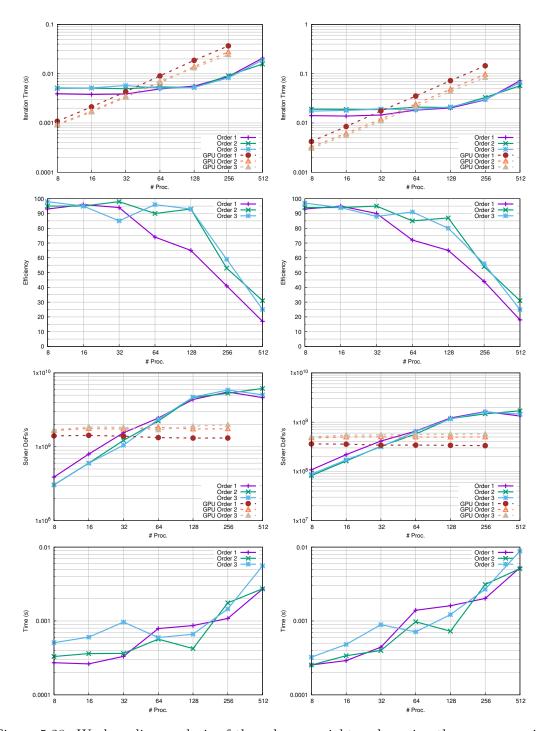

|              |                            | 5.3.3            | Strong scaling                     | 73  |  |  |  |  |  |

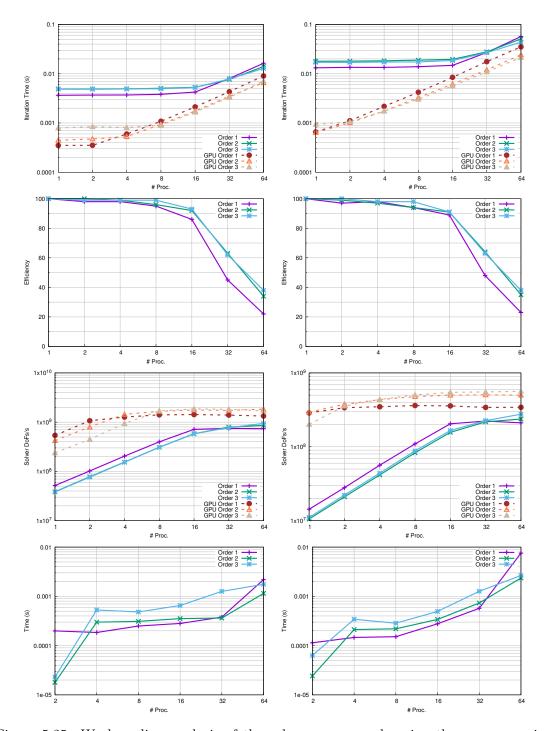

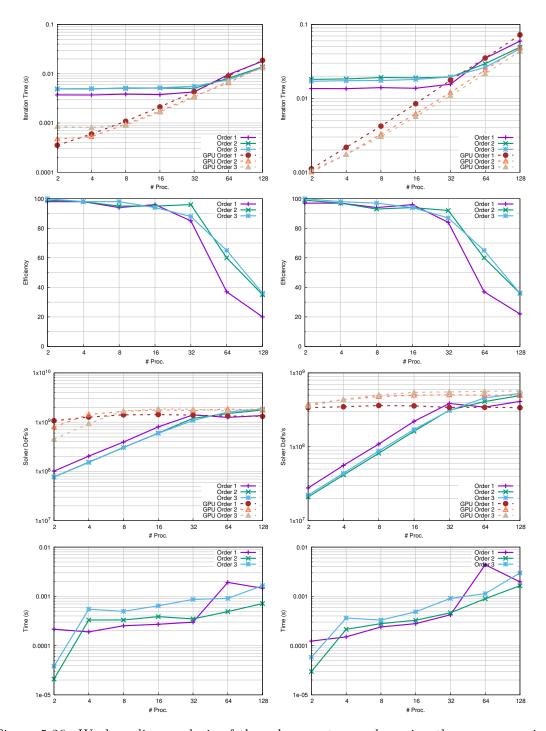

|              |                            | 5.3.4            | Weak scaling                       | 76  |  |  |  |  |  |

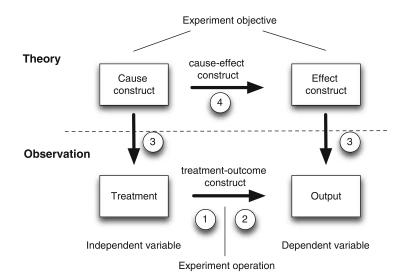

|              | 5.4                        | Validi           | ty Evaluation                      | 93  |  |  |  |  |  |

|              |                            | 5.4.1            | Threat classification              | 93  |  |  |  |  |  |

|              |                            | 5.4.2            | Threats mitigation                 | 94  |  |  |  |  |  |

|              |                            |                  | Conclusion validity                | 95  |  |  |  |  |  |

|              |                            |                  | Internal validity                  | 95  |  |  |  |  |  |

|              |                            |                  | External validity                  | 96  |  |  |  |  |  |

| 6            | Multi-GPU implementation 9 |                  |                                    |     |  |  |  |  |  |

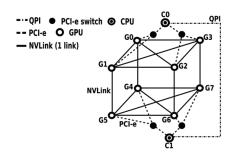

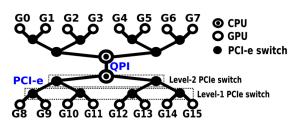

|              | 6.1                        | Multi-           | GPU architectures                  | 97  |  |  |  |  |  |

|              |                            | 6.1.1            | GPU interconnects                  | 98  |  |  |  |  |  |

|              |                            | 6.1.2            | Communication middleware           | 99  |  |  |  |  |  |

|              |                            | 6.1.3            | Challenges                         | 99  |  |  |  |  |  |

|              | 6.2                        | Multi-           | GPU on Gmsh DG                     | 101 |  |  |  |  |  |

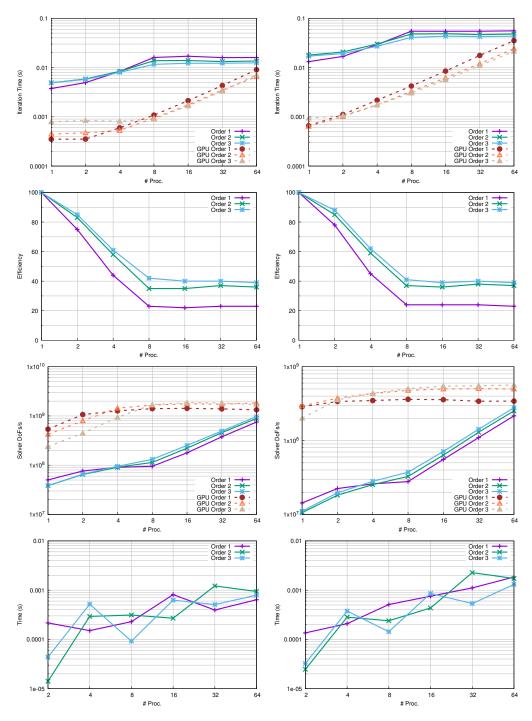

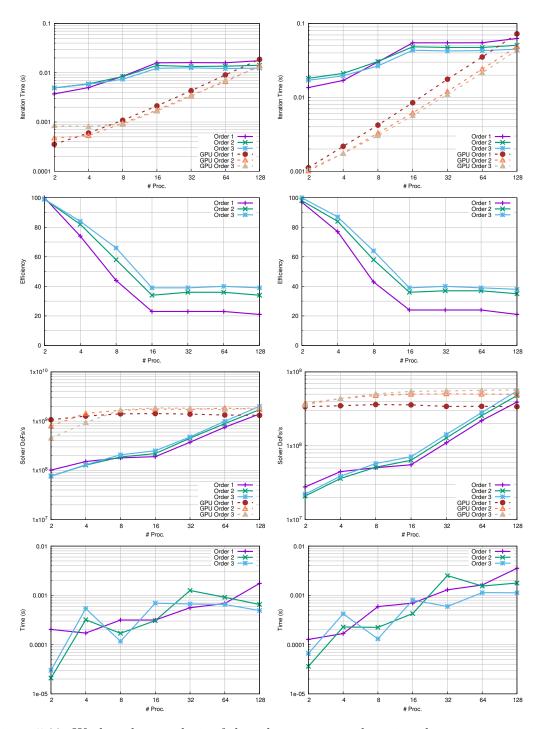

|              |                            | 6.2.1            | Solver scaling                     | 102 |  |  |  |  |  |

| Co           | onclu                      | sions            |                                    | 106 |  |  |  |  |  |

| Li           | ${ m st}$ of               | Figure           | es                                 | 108 |  |  |  |  |  |

| Li           | $\operatorname{st}$ of     | Tables           | S                                  | 112 |  |  |  |  |  |

| Bibliography |                            |                  |                                    |     |  |  |  |  |  |

### Introduction

The use of GPUs for general-purpose computing is a trend that has gradually established itself over the years, gaining more and more momentum with the development of modern programming models. Over the past decade, the use of GPUs for high performance computing has enabled better performance on a variety of problem types, and it is no coincidence that seven of the top ten supercomputers in the world feature graphics accelerators. Much like parallel software development on CPUs however, development on GPUs hides pitfalls and can become complex, especially in modern supercomputers where the use of multiple GPUs opens up even greater challenges.

To build parallel applications with optimal performance, it is therefore necessary to be aware of the issues of both the platforms for development and the hardware on which the applications are developed. The developer going to implement solutions that aim for high performance must not only use the abstractions made available by the programming model, but must be aware of the impact that each instruction has with respect to performance.

This thesis focuses in particular on analyzing the performance and possible optimizations achievable on a solver based on the Discontinuous Galerkin method for Maxwell's equations, Gmsh DG<sup>1</sup>, developed at the Applied and Computational Electromagnetics research group of the University of Liège. Applications of this type perform simulations that deal with the computation of millions of floating-point values per second, and which require appropriate optimization to be completed in a reasonable time. Thus, the main research question that we are trying to answer is:

How well can a reasonably simple DG solver exploit modern hardware?

In order to get an answer to this question, we structured the work in the following objectives

- 1. propose new optimizations to be implemented to improve the current limits of the application;

- 2. evaluate the performance of the application on real problems, perform scaling analysis and specific analysis related to the stages of computation;

- 3. help in the implementation of support for the use of multiple GPUs and performance analysis of the results obtained.

The solver has already been tested on real problems, for example, to simulate an electrostatic discharge on a device, and some performance results have been shown [1]. However,

<sup>1</sup>https://gitlab.onelab.info/gmsh/dg

a comprehensive analysis that can direct future developments and provide further insights had not yet been carried out. The starting point for performing these analyses is a thorough study of the existing code and the numerical concepts behind it. Then, starting with known bottlenecks, implementation of optimization strategies can be considered, followed by an analysis of these strategies to validate improvements. Finally, performance analysis must be performed both at the overall application level and at the level of individual computational kernels. Scaling analysis deals with overall performance on a real-world problem, investigating how the application adapts as computational and memory resources increase. The analysis of the kernels must be done through the use of specialized tools to derive accurate data, particularly with regard to analyzing the number of floating-point operations performed and memory traffic.

The first three chapters will be in a certain sense introductory to the work of this thesis. Chapter 1 will explain the physical and mathematical foundations related to the problem and the Discontinuous Galerkin method used to solve it, along with providing insights regarding how the method can be parallelized on multiprocessor systems. Chapter 2 will introduce the reader to GPU architecture and programming for general-purpose computing, with a special focus on the cautions needed to achieve good performance during GPU development. Chapter 3 describes the implementation of the Discontinuous Galerkin solver, starting by performing a review of the existing literature on solvers using graphics accelerators and then moving to the details of the code, along with the strategy used for parallelization.

The next three chapters are the heart of this work, showing the results obtained for each of the set goals. Chapter 4 discusses the optimizations implemented in the code and some of the optimization proposals that were considered for implementation. Chapter 5 focuses on analyzing the code from an application performance point of view through the scaling analysis on a multiprocessor system, and from a kernel perspective through the use of roofline analysis. Finally, Chapter 6 covers the multi-GPU implementation, describing how systems composed by multiple GPUs can be built and interconnected, the difficulties regarding the implementation, and showing the performance obtained on the platform at our disposal.

This thesis has been carried out under the Erasmus+ program with the collaboration between the University of Salerno and the University of Liège.

## Chapter 1

# Physical and mathematical context

Electricity and magnetism are two phenomena that, at least qualitatively, are known to humanity since the ancient times. Their systematic study however started only in the late 17th century, and since then countless scientist contributed to the improvement of our knowledge about these subjects.

Once thought as separate phenomena, it was only in 1820 that the first hints of a possible connection between electricity and magnetism were discovered by Hans Christian Øersted. By observing that the needle of a compass was deflected by a wire carrying an electric current, we can confidently say that he started the journey to the unification of electricity and magnetism. The subsequent studies carried out by Faraday, Ampère and Maxwell provided new insights, that finally led to the Maxwell's equations. Such equations represent perhaps the major scientific achievement of the 19th century: electricity, magnetism and optics unified in a single theory.

Maxwell's equations are central in electrical engineering, as they allow to model and predict the behaviour of the most disparate devices and systems. Their manual solution is however impossible in almost every practical setting, therefore accurate, reliable and fast numerical methods are needed. In this chapter we introduce the basics of the Discontinuous Galerkin method, which is at the core of the code that was analyzed and optimized in this thesis.

#### 1.1 Vector calculus

We recall here the main vector calculus notions that are used in the electromagnetic theory. For conciseness, we limit ourselves to  $\mathbb{R}^3$ .

A vector of  $\mathbb{R}^3$  is denoted with boldface font, as in  $\boldsymbol{u}$ ; its x,y,z components are denoted as  $u_x, u_y$  and  $u_z$  respectively. Similarly, a vector-valued function is denoted with boldface font, as in  $\boldsymbol{f}(\cdot)$  and its components as  $f_x(\cdot), f_y(\cdot), f_z(\cdot)$ .

The nabla operator  $\nabla$  is defined as the column vector of the partial derivatives

$$\nabla = \left[ \frac{\partial}{\partial x} \, \frac{\partial}{\partial y} \, \frac{\partial}{\partial z} \right]^T.$$

The nabla operator can be applied to sufficiently smooth scalar functions  $f: \mathbb{R}^3 \to \mathbb{R}$  or to sufficiently smooth vector functions  $\mathbf{f}: \mathbb{R}^3 \to \mathbb{R}^3$  yielding different quantities of interest:

$$\nabla f = \begin{bmatrix} \frac{\partial f}{\partial x} \\ \frac{\partial f}{\partial y} \\ \frac{\partial f}{\partial z} \end{bmatrix}, \qquad \nabla \times \mathbf{f} = \begin{bmatrix} \frac{\partial f_z}{\partial y} - \frac{\partial f_y}{\partial z} \\ \frac{\partial f_x}{\partial z} - \frac{\partial f_z}{\partial x} \\ \frac{\partial f_y}{\partial x} - \frac{\partial f_x}{\partial y} \end{bmatrix}, \qquad \nabla \cdot \mathbf{f} = \sum_{w \in \{x, y, z\}} \frac{\partial f_w}{\partial w}. \tag{1.1}$$

The three expressions appearing in (1.1) are the *gradient* of f, the *curl* of f and the *divergence* of f respectively. We recall also that the following identities hold:

$$\nabla \times (\nabla f) = \mathbf{0} \quad \forall f, \qquad \nabla \cdot (\nabla \times \mathbf{f}) = 0 \quad \forall \mathbf{f}. \tag{1.2}$$

A central ingredient for the discussion of the numerical methods employed in this thesis is the divergence theorem. For sufficiently smooth functions  $f: \mathbb{R}^3 \to \mathbb{R}^3$ , it holds that

$$\int_{V} (\nabla \cdot \boldsymbol{f}) \, dv = \int_{\partial V} \boldsymbol{f} \cdot \, d\boldsymbol{s}. \tag{1.3}$$

By applying the substitution  $\mathbf{f} \to \mathbf{f}g$  to (1.3) and using the vector calculus identity  $\nabla \cdot (\mathbf{f}g) = (\nabla \cdot \mathbf{f})g + \mathbf{f} \cdot (\nabla g)$  we obtain an important corollary that will be used in the following:

$$\int_{V} \mathbf{f} \cdot (\nabla g) \, dV + \int_{V} (\nabla \cdot \mathbf{f}) g \, dV = \int_{\partial V} (\mathbf{f} \cdot \hat{\mathbf{n}}) g \, dS. \tag{1.4}$$

#### 1.2 Maxwell's equations

Let  $\boldsymbol{x} \in \mathbb{R}^3$  denote a position vector and  $t \in \mathbb{R}^+$  the time, where  $\mathbb{R}^+ = \{x : x \in \mathbb{R}, x \geq 0\}$ . The time-domain Maxwell's equations are written in differential form as

$$\nabla \times \boldsymbol{e}(\boldsymbol{x},t) = -\frac{\partial \boldsymbol{b}(\boldsymbol{x},t)}{\partial t},\tag{1.5}$$

$$\nabla \times \boldsymbol{h}(\boldsymbol{x},t) = \frac{\partial \boldsymbol{d}(\boldsymbol{x},t)}{\partial t} + \boldsymbol{j}(\boldsymbol{x},t) + \boldsymbol{j}_s(\boldsymbol{x},t)$$

(1.6)

$$\nabla \cdot \boldsymbol{b}(\boldsymbol{x}, t) = 0, \tag{1.7}$$

$$\nabla \cdot \boldsymbol{d}(\boldsymbol{x}, t) = \rho(\boldsymbol{x}, t), \tag{1.8}$$

where the following quantities are involved:

- $e: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the *electric field*, which has units of V/m (Volts per meter),

- $b: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the magnetic flux density, which has units of T (Tesla),

- $h: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the magnetic field, which has units of A/m (Ampère per meter),

- $d: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the *electric displacement field*, which has units of C/m<sup>2</sup> (Coulomb per square meter)

- $j: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the *current density* in conductive media, whereas  $j_s: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}^3$  is the *current density* due to the sources. Both fields have units of A/m<sup>3</sup> (Ampère per cubic meter)

- $\rho: (\mathbb{R}^3 \times \mathbb{R}^+) \to \mathbb{R}$  is the *charge density*, which has units of C/m<sup>3</sup> (Coulomb per cubic meter)

From now on, the spatial and temporal dependence of all the fields will be considered implicit, therefore we will omit to indicate it in the equations. The four equations (1.5)-(1.8) were devised by different scientists, in particular:

- Equation (1.5) is the Faraday-Neumann law, and states that a time-varying magnetic flux density **b** induces a circulation of the electric field **e**. It formalizes the concept of electromagnetic induction, discovered by Michael Faraday in 1831. The equation in this form is due to Franz Ernest Neumann, who introduced it in 1845.

- Equation (1.6) is the Ampère-Maxwell law, and describes the magnetic fields that form around electric currents. More in detail, a circulation of the magnetic field  $\boldsymbol{h}$  is given by the sum of  $\boldsymbol{j}$ , which collects the current densities due to electrical conduction in the materials and  $\boldsymbol{j}_s$ , which collects the current density sources.

The third term, the temporal variation of the displacement field d, is named displacement current and was introduced by James Clerk Maxwell in 1865. This led to the unification of the magnetic and electric fields and to the formalization of the propagation of electromagnetic waves.

- Equation (1.7) is the magnetic Gauss' law. It states the non-existence of magnetic monopoles, as in a zero-divergence field all the field lines are closed.

- The electric Gauss' law (1.8) finally allows to state (by integrating on the considered domain) that the electric flux through a closed surface equals the charge enclosed by the same surface.

Normally, Maxwell's equations are solved in a domain  $\Omega \subset \mathbb{R}^3$  and subject to specific initial and boundary conditions. The most common boundary conditions are:

- $\hat{\boldsymbol{n}} \times \boldsymbol{e} = \boldsymbol{0}$ , known as Perfect Electric Conductor (PEC),

- $\hat{\boldsymbol{n}} \times \boldsymbol{h} = \boldsymbol{0}$ , known as Perfect Magnetic Conductor (PMC),

•  $Z\hat{\boldsymbol{n}} \times \boldsymbol{h} = \hat{\boldsymbol{n}} \times (\boldsymbol{e} \times \hat{\boldsymbol{n}})$ , known as Impedance Boundary Condition (IBC).

Materials are taken into account by the three constitutive relations

$$d = \epsilon e, \qquad b = \mu h, \qquad j = \sigma e,$$

(1.9)

which are called electric constitutive relation, magnetic constitutive relation and Ohm's law respectively. The quantities  $\epsilon$ ,  $\mu$  and  $\sigma$  are the electric permittivity, the magnetic permeability and the conductivity, and depend on the considered material; we will refer to these quantities with the general designation of material parameters. In the most general setting all the three quantities are tensors belonging to  $\mathbb{R}^{3\times3}$  and can be position- and time-dependent. In the context of this thesis however, we will only consider materials which are linear, locally homogeneous, isotropic and nondispersive, leading to piecewise constant, scalar material parameters: this setting, despite not being fully general, covers a huge class of practical engineering problems.

Electric permittivity and magnetic permeability are commonly further decomposed as  $\epsilon = \epsilon_r \epsilon_0$  and  $\mu = \mu_r \mu_0$  respectively, where the terms with the subscript 0 are the *free space* parameters, whereas the terms subscripted with r are the *relative* parameters. In SI units, the values of the free space parameters are  $\epsilon_0 = 8.8541878128 \times 10^{-12}$  F/m and  $\mu_0 = 4\pi \times 10^{-7}$  H/m.

In order to show that the electromagnetic field propagates in waves, we consider the source-free setting where  $j_s = 0$ ,  $\rho = 0$  and that there is no conductive media, therefore  $\sigma = 0$ . By substituting the constitutive relations (1.9) in (1.5)-(1.6) and rearranging, one obtains

$$\mu \frac{\partial \boldsymbol{h}(\boldsymbol{x},t)}{\partial t} = -\nabla \times \boldsymbol{e}(\boldsymbol{x},t), \tag{1.10}$$

$$\epsilon \frac{\partial \boldsymbol{e}(\boldsymbol{x},t)}{\partial t} = \nabla \times \boldsymbol{h}(\boldsymbol{x},t). \tag{1.11}$$

By taking the divergence of (1.10) and using the second identity in (1.2), we deduce that (1.7) is automatically satisfied by (1.10). In addition, by taking the divergence of (1.10), using the same identity as before and recalling that we are in a source-free setting, we deduce that (1.8) is automatically satisfied by (1.11). Therefore, we do not need to enforce explicitly (1.7) and (1.8) during the solution process.

Now, by taking the curl of (1.10) and substituting (1.11) in the result, one obtains

$$\nabla \times \mu^{-1}(\nabla \times \boldsymbol{e}) + \epsilon \frac{\partial^2 \boldsymbol{e}}{\partial t^2} = \boldsymbol{0}, \tag{1.12}$$

confirming that the electromagnetic field propagates as waves with speed  $c = 1/\sqrt{\mu\epsilon}$ .

In the following, the system of equations (1.10)-(1.11) will be called *first order formulation* of the Maxwell's equations, wheareas (1.12) will be called *second order formulation*

of the Maxwell's equations. In the context of this thesis, we will be interested in solving the first order formulation using appropriate numerical methods.

#### 1.3 Numerical solution of PDEs

Partial differential equations (PDEs) like Maxwell's equations are rarely solvable analitically, therefore appropriate numerical methods must be used to approximate their solution. In addition, it must be noted that differential equations are statements involving all the points of a domain, which are clearly in infinite number and therefore intractable on a computer. It is thus necessary to appropriately discretize the computational domain and the differential equation at hand.

In order to gently introduce the subject of spatial discretizations for PDEs, we start by describing the Finite Volume method in 1D before moving to the more complex Discontinuous Galerkin method, also in 1D. Once all the basics are in place, we will finall move to the Discontinuous Galerkin method for the Maxwell's equations. We limit the level of detail to what is needed for this thesis, we refer the interested reader to [2, 3, 4] for a more in-depth discussion.

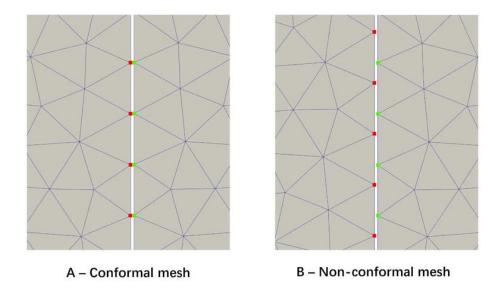

#### 1.3.1 Computational domain and meshes

In this section, some general definitions about meshes will be recalled, see [5, Chapter1] for more details.

**Definition 1** (Mesh). Let  $\Omega$  be a polyhedral domain. A discretization of  $\Omega$  is a collection of polyhedral elements  $\mathcal{T} := \{T_1, \ldots, T_n\}$  such that

$$T_i \cap T_j = \emptyset, \quad \forall i \neq j \in \{1, \dots, |\mathcal{T}|\}; \qquad \bigcup_i \overline{T_i} = \overline{\Omega}, \quad i \in \{1, \dots, |\mathcal{T}|\}$$

**Definition 2** (Mesh size). Let  $\mathcal{T}$  be a mesh of  $\Omega$ . The quantity  $h_T$  denotes the diameter of an element T. The mesh size is denoted as the real number

$$h := \max_{T \in \mathcal{T}} h_T.$$

In the following, the notation  $\mathcal{T}_h$  will be used to denote a mesh whose size is h.

**Definition 3** (Mesh skeleton). Let  $\mathcal{T}_h$  be a mesh covering  $\Omega$ . The skeleton  $\Gamma$ , the internal skeleton  $\Gamma_{int}$  and the boundary skeleton  $\Gamma_{bnd}$  are the sets

$$\Gamma := \bigcup_{T \in \mathcal{T}} \partial T, \qquad \Gamma_{int} := \Gamma \setminus \partial \Omega, \qquad \Gamma_{bnd} = \Gamma \setminus \Gamma_{int}.$$

**Definition 4** (Mesh faces). Let  $\mathcal{T}_h$  be a mesh covering  $\Omega$ . A subset  $F \subset \overline{\Omega}$  is defined to be a face if one of the following two conditions hold:

- Given two distinct elements  $T_1$  and  $T_2$ , the set  $F = T_1 \cap T_2 \subset \Gamma_{int}$  is nonempty, and in this case F is called internal face.

- Given an element T, the set  $F = T \cap \partial\Omega \subset \Gamma_{bnd}$  is nonempty, and in this case F is called boundary face.

The faces of an element T are the elements  $F_i \subset \Gamma$  such that  $F_i \in \partial T$ . We denote  $\mathcal{F}_T$  the set of the faces of T.

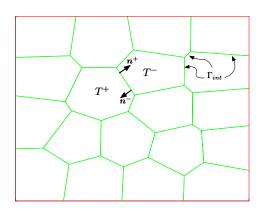

**Definition 5** (Normals on faces). Let  $\mathcal{T}_h$  be a mesh covering  $\Omega$ . For each T and for each  $F_i \in \mathcal{F}_T$ , we denote with  $\hat{\boldsymbol{n}}$  the outward normal on  $F_i$ . Given two adjacent elements  $T^+$  and  $T^-$  sharing the face F,  $\hat{\boldsymbol{n}}^+$  denotes the normal on F pointing from  $T^+$  to  $T^-$ . The normal  $\hat{\boldsymbol{n}}^-$  is similarly defined to be the normal on F pointing from  $T^-$  to  $T^+$ .

- $\Gamma := \bigcup_{T \in \mathcal{T}_b} \partial T$  (skeleton)

- $\Gamma_{int} = \Gamma \setminus \partial \Omega$

- $T^+$  and  $T^-$  generic elements sharing a face

- $F := T^+ \cap T^- \subset \Gamma_{int}$

- $\hat{\boldsymbol{n}}^+$  and  $\hat{\boldsymbol{n}}^-$  normals of  $T^+$  and  $T^-$  on F

Figure 1.1: Visual summary of the symbols introduced to denote mesh elements.

#### 1.3.2 Conservation laws in one dimension

Let  $u(x,t): \mathbb{R} \times \mathbb{R}^+ \to \mathbb{R}$ , f(u) a flux function and  $g(x,t): \mathbb{R} \times \mathbb{R}^+ \to \mathbb{R}$ . We consider the conservation law

$$\frac{\partial u}{\partial t} + \frac{\partial f}{\partial x} = g,\tag{1.13}$$

posed on a certain domain  $\Omega$  and subject to the appropriate boundary conditions. In addition, we consider only linear fluxes of the form f(u) = au. The equation (1.13) is solved by some numerical method on a discretization of  $\Omega$ , obtaining a numerical solution  $u_h$  which is clearly different from the true solution u. The solutions u and  $u_h$  are sought in

some spaces V and  $V_h$  respectively, which will be made more precise further ahead. Once a solution  $u_h$  is obtained, by plugging  $u_h$  in (1.13) it is possible to define the *residual*

$$\mathcal{R}(x,t) := \frac{\partial u_h}{\partial t} + \frac{\partial f_h}{\partial x} - g, \tag{1.14}$$

which clearly can not be zero, otherwise we would have obtained the exact solution u to the equation. Our goal is to obtain a numerical method that solves (1.13) yielding a discrete solution  $u_h$  such that the residual  $\mathcal{R}$  has some properties. Such properties depend on the chosen numerical method.

To fix the ideas, let the computational domain be  $\Omega = [0,1]$ ; we are thus considering a 1D setting. In order to obtain a spatial discretization of  $\Omega$  we can divide the interval [0,1] in N segments. The segments so obtained are the elements  $T_1, \ldots, T_N$  of the mesh. Each segment  $T_n$  has a start point  $x_{n-1/2}$  and an end point  $x_{n+1/2}$ , therefore  $h_{T_n} = x_{n+1/2} - x_{n-1/2}$ .

#### 1.3.3 The Finite Volume Method

A possible strategy to approximate the solution of (1.13) in our discrete domain, is to consider its cell-by-cell average

$$\bar{u}_n = \frac{1}{h_{T_n}} \int_{T_n} u \, dV, \qquad \frac{d\bar{u}_n}{dt} = \frac{1}{h_{T_n}} \int_{T_n} \frac{\partial u}{\partial t} \, dV.$$

In this way, the discrete approximation is a piecewise constant function whose value in each element is the average of the solution in the considered element. In order to obtain a numerical method from such strategy, we proceed as follows:

• Step 1: once the domain is discretized and the elements  $T_n$  are identified, take the average of (1.13) elementwise obtaining

$$\frac{1}{h_{T_n}} \int_{T_n} \frac{\partial u}{\partial t} dV + \frac{1}{h_{T_n}} \int_{T_n} \frac{\partial f}{\partial x} dV = \frac{1}{h_{T_n}} \int_{T_n} g \ dV, \quad \forall T_n \in \mathcal{T}$$

(1.15)

• Step 2: Apply the divergence theorem (1.3) to the spatial term of (1.15)

$$\int_{T_n} \nabla \cdot \boldsymbol{f} dV = \int_{\partial T_n} \boldsymbol{f} \cdot \boldsymbol{\hat{n}} dS \quad \xrightarrow{\text{or, in 1D}} \quad \int_{T_n} \frac{\partial f}{\partial x} dl = f^{n+1/2} - f^{n-1/2},$$

where  $f^{n-1/2}$  and  $f^{n+1/2}$  are the values of the flux at the boundaries of  $T_n$ . We can then obtain the element-local statement

$$\frac{d\bar{u}_n}{dt} + \frac{f^{n+1/2} - f^{n-1/2}}{h_{T_n}} = \bar{g}_n \tag{1.16}$$

With the two steps above we obtained a semi-discrete scheme that provides N equations, one for each element  $T_n$ . The scheme however is still incomplete and does not allow to approximate our original equation (1.13). Indeed, recalling that we consider only fluxes of the type f(u) = au and that we chose a piecewise constant approximation for  $u_h$ , one immediately realizes that  $u_h$  at the interfaces between elements is not single-valued.

In order to complete the scheme then, one needs to provide a way to specify the values of the numerical fluxes  $f^{n-1/2}$  and  $f^{n+1/2}$ . It turns out that the choice of the numerical fluxes is a major topic in the study of the discontinuous methods, therefore no attempt will be made to discuss the subject further. We refer the reader to [4, 6] for the details, here we limit to mention the two most simple and common possibilities:

• Centered fluxes: The centered fluxes are the simplest and most intuitive possibility. In this case the value at the interfaces is fixed by taking the average between the solution in the two adjacent cells. More formally:

$$f^{n+1/2} := \frac{a}{2}(\bar{u}_n + \bar{u}_{n+1}). \tag{1.17}$$

• Upwind fluxes: The upwind fluxes have a slightly more complex expression:

$$f^{n+1/2} := \frac{a}{2}(\bar{u}_n + \bar{u}_{n+1}) + \frac{a}{2}(\bar{u}_n - \bar{u}_{n+1}) \cdot \hat{\boldsymbol{n}}. \tag{1.18}$$

The precise definition of the fluxes now allows us to obtain a usable numerical scheme. Let us consider, only for illustration purposes, a forward finite difference discretization of the time derivative. Let  $\Delta x = h_{T_n}$ , the finite volumes discrete update equations are

$$\bar{u}_n^{i+1} = \bar{u}_n^i - \frac{\Delta t}{\Delta x} (f^{n+1/2} - f^{n-1/2}). \tag{1.19}$$

If we consider centered fluxes we have

$$f_i^{n+1/2} = \frac{a}{2}(\bar{u}_n^i + \bar{u}_{n+1}^i), \qquad f^{k-1/2} = \frac{a}{2}(\bar{u}_{n-1}^i + \bar{u}_n^i).$$

(1.20)

By replacing (1.20) in (1.19) we obtain

$$\bar{u}_n^{i+1} = \bar{u}_n^i - \frac{a\Delta t}{2\Delta x}(\bar{u}_{n+1}^i - \bar{u}_{n-1}^i),$$

which is directly implementable in software. In order to have stability, the scheme is subject to the Courant–Friedrichs–Lewy (CFL) condition

$$\frac{a\Delta t}{2\Delta x} \le 1.$$

On the other hand, if we use upwind fluxes we have

$$f^{n+1/2} = \frac{a}{2}(\bar{u}_n^i + \bar{u}_{n+1}^i) + \frac{a}{2}(\bar{u}_n^i - \bar{u}_{n+1}^i), \quad f^{n-1/2} = \frac{a}{2}(\bar{u}_{n-1}^i + \bar{u}_n^i) - \frac{a}{2}(\bar{u}_{n-1}^i - \bar{u}_n^i),$$

$$(1.21)$$

therefore, by replacing (1.21) in (1.19) we obtain

$$\bar{u}_n^{i+1} = \bar{u}_n^i - \frac{a\Delta t}{\Delta x}(\bar{u}_n^i - \bar{u}_{n-1}^i),$$

which again is easily implementable in software. In the upwind case the CFL is

$$\frac{a\Delta t}{\Delta x} \le 1.$$

We remark that the centered fluxes result in a method which is essentially equivalent to a central finite difference, whereas the upwind fluxes result in a backward finite difference. This has important implications, the most significant being that the upwind fluxes introduce numerical diffusion. More in detail, we recall that

$$\frac{d^2v}{dx^2} \approx \frac{v_{n+1} - 2v_n + v_{n-1}}{\Delta x^2}.$$

Arranging appropriately the terms when replacing (1.21) in (1.19), it is possible to obtain

$$\bar{u}_n^{i+1} = \bar{u}_n^i - \frac{a\Delta t}{2\Delta x}(\bar{u}_{n+1}^i - \bar{u}_{n-1}^i) + \frac{a\Delta t\Delta x}{2} \frac{(\bar{u}_{n+1}^i - 2\bar{u}_n^i + \bar{u}_{n-1}^i)}{\Delta x^2},$$

where we remark the appearance of a diffusion term of purely numerical origin and whose influence is reduced by either reducing the mesh size or the timestep. It is therefore of considerable importance to be aware of the influence of upwind effects in the computation results.

The method just described goes under the name of *Finite Volume Method* (FVM) and is widely used in computational fluid dynamics. The FVM however is a low order method, as the resulting approximation is only first order. In order to obtain increased accuracy, it would be desirable to have high order approximation, and this is what brings us to the Discontinuous Galerkin method discussed in the next section.

#### 1.3.4 The Discontinuous Galerkin method

The ideas behind the Discontinuous Galerkin (DG) method are not dissimilar from those behind the FVM. Indeed, DG can be seen as a FVM where instead of simply averaging the solution, we use a more sophisticated technique.

Before going any further, we must define the discrete space used in the Discontinuous Galerkin method (for a rigorous treatment see [5, 7]).

Let  $L^2(\Omega)$  be the standard Lebesgue space of square integrable functions. The discrete DG solution lives in the space

$$V_h := \left\{ v \in L^2(\Omega) : v_{|T_i} \in \mathbb{P}_d^k(T_i) \right\}, \qquad i \in \{1, \dots, |\mathcal{T}|\}.$$

(1.22)

Intuitively, this definition asserts that the functions of  $V_h$  are piecewise polynomial functions that can jump on the mesh interfaces.

We also recall that a d-variate polynomial p of degree k can be written as a linear combination of basis functions

$$p(\boldsymbol{x}) = \sum_{j=1}^{N_d^k} p_j \phi_j(\boldsymbol{x}) = \boldsymbol{p}^T \boldsymbol{\phi}(\boldsymbol{x}), \qquad \boldsymbol{x} \in T$$

(1.23)

where the linear combination weights are denoted as  $p_j$ , the basis functions as  $\phi_j(\boldsymbol{x})$ ; in addition  $\boldsymbol{p}$  is the column vector  $\{p_j\}_{j\in\{1,\dots,N_d^k\}}$  and  $\boldsymbol{\phi}(\boldsymbol{x})$  is the column vector  $\{\phi_j(\boldsymbol{x})\}_{j\in\{1,\dots,N_d^k\}}$ . Clearly, once a base is chosen and fixed, only the coefficient vector  $\boldsymbol{p}$  needs to be stored to fully represent the original polynomial. A function of  $V_h$  can therefore be represented as a column vector  $[\boldsymbol{p}_1 \mid \dots \mid \boldsymbol{p}_N]$  which is the juxtaposition of all the coefficients of the polynomials attached to the mesh elements.

In addition, we recall that polynomials can be integrated numerically exactly using quadrature rules. Given a polynomial  $p(\mathbf{x})$  and a reference element  $T_{\text{ref}}$ , the integral of p in  $T_{\text{ref}}$  can be computed as a sum of evaluations of p in the points  $\mathbf{q}_w$  weighted by the coefficients  $\omega_w$  specified by a quadrature rule Q:

$$\int_{T_{\text{ref}}} p(\boldsymbol{x}) dV = \sum_{(\boldsymbol{q}_w, \omega_w) \in Q} \omega_w p(\boldsymbol{q}_w).$$

In order to integrate on a generic element T different from  $T_{\text{ref}}$  using a quadrature, an appropriate change of variable has to be made.

A possible choice for the basis functions  $\phi_j$  are the Lagrange polynomials: for example, if a 1-variate polynomial of degree k in the interval  $[x_0, x_k]$  needs to be interpolated, we consider the k+1 points  $\{x_0, \ldots, x_k\}$  and define the functions

$$\ell_j(x) = \frac{(x - x_0)}{(x_j - x_0)} \cdots \frac{(x - x_{j-1})}{(x_j - x_{j-1})} \frac{(x - x_{j+1})}{(x_j - x_{j+1})} \cdots \frac{(x - x_k)}{(x_j - x_k)} = \prod_{\substack{0 \le m \le k \\ m \ne j}} \frac{x - x_m}{x_j - x_m}, \quad (1.24)$$

where we remark that  $\ell_j(x_m) = \delta_{jm}$ , being  $\delta$  the Kroneker symbol. Clearly, if  $x_0$  and  $x_k$  are the endpoints of the element  $T_n$ , the Lagrange functions form a polynomial basis on that element; we use the notation  $\ell_j^{T_n}$  in that case. The Lagrange functions can be defined also in 2D or in 3D, we refer the reader to the standard finite element literature for the details [8]. Using the Lagrange basis functions, we can define the approximation space as

$$V_h := \bigoplus_{n=1}^N \left\{ \ell_j^{T_n} \right\}_{j \in \{1, \dots, N_d^k\}} = \bigoplus_{n=1}^N \left\{ \boldsymbol{\ell}^{T_n} \right\}.$$

With all the preliminaries now in place, we can start to discuss the construction of the Discontinuous Galerkin (DG) method. Let  $v \in V_h$  be a test function. In order to devise the

DG method, we start by requiring that the residual is orthogonal to all the test functions in  $V_h$ , or that the expression

$$\int_{\Omega} \left( \frac{\partial u_h}{\partial t} + \frac{\partial f(u_h)}{\partial x} - g \right) v \, dV = 0, \qquad \forall v \in V_h, \tag{1.25}$$

holds. In particular, as the approximation space is discontinuous and piecewise polynomial, (1.25) is equivalent to requiring for all  $T_n \in \mathcal{T}$  that the local statement

$$\int_{T_n} \left( \frac{\partial u_h^{T_n}}{\partial t} + \frac{\partial f(u_h^{T_n})}{\partial x} - g \right) \ell_j^{T_n} dV = 0, \qquad \forall j \in \{1, \dots, N_d^k\},$$

(1.26)

holds. This generates  $N_d^k$  equations per element however, in an entirely similar manner to the FVM case, the procedure would not yield a solvable discrete problem: we therefore need to introduce the numerical fluxes  $f^*$  in order to fix the values at the mesh interfaces. Before, however, we need to slightly refine their definition. To this aim, we introduce the

**Definition 6** (Average and Jump operators). Let  $v : \Omega \to \mathbb{R}$  and let  $F \in \Gamma_{int}$  be the face shared by elements  $T^+, T^-$ . We define the verage and ump operators as follows:

Average:

$$\{v\}_F(x) := \frac{1}{2} [v|_{T^+}(x) + v|_{T^-}(x)]$$

$Jump: [v]|_F(x) := v|_{T^+}(x) - v|_{T^-}(x)$

If F belongs to the boundary of the domain (i.e.  $e \subset \partial T \cap \partial \Omega$ ):

$$\{v\}_F(x) := v|_T(x), \qquad \llbracket v \rrbracket|_F(x) := v|_T(x).$$

If v is vector-valued, the average and jump operators act component-wise.

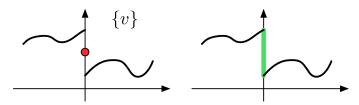

Figure 1.2: Graphical representation of the average (left) and jump (right).

If clear from the context, the subscript specifying the face on which operators act will be omitted.

Using the notation just introduced, the centered fluxes are written as

$$f^* = a\{u_h\},\,$$

whereas the upwind fluxes take the form

$$f^* = a\{u_h\} + \frac{a}{2} \llbracket u_h \rrbracket \cdot \hat{\boldsymbol{n}}.$$

With the new notation in place we proceed locally element-by-element, integrating by parts two times the spatial term of (1.26). With the first integration by parts we obtain

$$\int_{T_n} \frac{\partial u_h^{T_n}}{\partial t} \boldsymbol{\ell}^{T_n} dV - \int_{T_n} f(u_h^{T_n}) \frac{\partial \boldsymbol{\ell}^{T_n}}{\partial x} dV = \int_{T_n} g \boldsymbol{\ell}^{T_n} dV - \int_{\partial T_n} (\hat{\boldsymbol{n}} \cdot f^*) \boldsymbol{\ell}^{T_n} dS,$$

and we remark that by replacing  $\ell^{T_n}$  with the constant function, the expression collapses back to the FVM. Subsequently, we proceed with a second integration by parts on the spatial term, obtaining

$$\int_{T_n} \frac{\partial u_h^{T_n}}{\partial t} \boldsymbol{\ell}^{T_n} dV + \int_{T_n} \frac{\partial f(u_h^{T_n})}{\partial x} \boldsymbol{\ell}^{T_n} dV = \int_{T_n} g \boldsymbol{\ell}^{T_n} dV + \int_{\partial T_n} \hat{\boldsymbol{n}} \cdot (f - f^*) \boldsymbol{\ell}^{T_n} dS.$$

Recalling that locally we approximate a polynomial and we use the Lagrange basis, we have that

$$u_h^{T_n}(x) = \sum_{i=1}^{N_d^k} \mathbf{u}_j \, \ell_j^{T_n}(x),$$

where  $\{\mathbf{u}_j\}_{j\in\{1,...N_d^k\}} = \mathbf{u}^{T_n}$  are the unknown coefficients of the local polynomial approximating the solution. We can now introduce the element mass matrix  $\mathsf{M}_{ij}^{T_n}$  and the element stiffness matrix  $\mathsf{S}_{ij}^{T_n}$  as

$$\mathsf{M}_{ij}^{T_n} = \int_{T_n} \ell_j^{T_n}(x) \ell_i^{T_n}(x) dx, \qquad \mathsf{S}_{ij}^{T_n} = \int_{T_n} \frac{\partial \ell_j^{T_n}(x)}{\partial x} \ell_i^{T_n}(x) dx,$$

where the integrals are computed with appropriate quadratures, to finally obtain the semidiscrete scheme

$$\mathsf{M}^{T_n} \frac{d\mathbf{u}_h^{T_n}}{dt} + \mathsf{S}^{T_n} \mathbf{f}_h^{T_n} - \mathsf{M}^{T_n} \mathbf{g}_h^{T_n} = \left( f_h^{T_n}(x^{k+1}) - f^*(x^{k+1}) \right) \boldsymbol{\ell}^{T_n}(x^{k+1}) - \left( f_h^{T_n}(x^k) - f^*(x^k) \right) \boldsymbol{\ell}^{T_n}(x^k).$$

(1.27)

Once a time integration algorithm and the appropriate numerical fluxes are chosen, the scheme is directly implementable.

#### Computational properties of DG

For the aims of this work, it is of primary importance to realize which are the computational properties of (1.27). Indeed, all the volumetric terms are element-local and can be computed independently and in parallel. The only communication between adjacent elements takes place in the computation of the fluxes.

In addition to the element-level parallelism the matrix-vector products offer another level of parallelism, as they can be parallelized by row. Indeed, if we consider the matrix-vector product  $\mathbf{y} = M\mathbf{x}$ , all its entries

$$\mathsf{y}_i = \sum_j \mathsf{M}_{ij} \mathsf{x}_j$$

can be computed in parallel. Taking into account the way in which GPUs work, this enables DG to be extremely efficient on such architectures (See Chapter 2).

Another point that must be noted about (1.27) is that  $M^{T_n}$  and  $S^{T_n}$  depend on the element  $T_n$  and they are potentially all different across the mesh. In order to reduce the computational and memory costs it is possible however to introduce a reference element and have a single mass matrix and a single stiffness matrix: we give the intuition in 2D, the technique is easily extended to 3D. Let  $T_n$  be a triangle whose vertices are  $\mathbf{p}_1^{T_n} = (x_1, y_1)$ ,  $\mathbf{p}_2^{T_n} = (x_2, y_2)$  and  $\mathbf{p}_3^{T_n} = (x_3, y_3)$ . In addition, let  $T_{ref}$  be the reference triangle whose vertices are  $\hat{\mathbf{p}}_1 = (0,0)$ ,  $\hat{\mathbf{p}}_2 = (1,0)$  and  $\hat{\mathbf{p}}_3 = (0,1)$ . Finally, let (x,y) be a pair of coordinates on  $T_n$  and  $(\xi, \eta)$  be a pair of coordinates in  $T_{ref}$ . An affine transformation T from  $T_{ref}$  to  $T_n$  is obtained as follows:

1. Define a set of linear basis functions  $\hat{N}_i(\xi, \eta)$  on the reference triangle such that  $\hat{N}_i(\hat{p}_j) = \delta_{ij}$ , where  $\delta$  is the Kroneker symbol. Such basis functions are

$$\hat{N}_1(\xi, \eta) = 1 - \xi - \eta, \qquad \hat{N}_2(\xi, \eta) = \xi, \qquad \hat{N}_3(\xi, \eta) = \eta.$$

2. Form the linear combination

$$\mathsf{T}(\hat{oldsymbol{p}}) = \mathsf{T}(\xi, \eta) = \sum_{i=1}^{3} \hat{N}_i(\xi, \eta) \, oldsymbol{p}_i^{T_n},$$

which can be expanded as

$$\begin{bmatrix} x \\ y \end{bmatrix} = \begin{bmatrix} x_1 \\ y_1 \end{bmatrix} (1 - \xi - \eta) + \begin{bmatrix} x_2 \\ y_2 \end{bmatrix} \xi + \begin{bmatrix} x_3 \\ y_3 \end{bmatrix} \eta$$

$$= \begin{bmatrix} x_2 - x_1 & x_3 - x_1 \\ y_2 - y_1 & y_3 - y_1 \end{bmatrix} \begin{bmatrix} \xi \\ \eta \end{bmatrix} + \begin{bmatrix} x_1 \\ y_1 \end{bmatrix} = \mathbf{T}\hat{\mathbf{x}} + \mathbf{b}.$$

It is easy to see that the last expression establishes a bijection between  $T_{ref}$  and  $T_n$ .

It turns out that the functions  $\hat{N}_i$  are the first order Lagrange functions on a triangle, and  $N^{T_n}(\boldsymbol{x}) = N^{T_n}(\mathsf{T}(\hat{\boldsymbol{x}})) = \hat{N}_i(\hat{\boldsymbol{x}})$ . Therefore, by the change of variable rule for the integrals

$$\mathsf{M}_{ij}^{T_n} = \int_{T_n} N_j^{T_n}(\boldsymbol{x}) N_i^{T_n}(\boldsymbol{x}) dx = \left| \det \boldsymbol{T} \right| \int_{T_{ref}} \hat{N}_j(\hat{\boldsymbol{x}}) \hat{N}_i(\hat{\boldsymbol{x}}) d\hat{\boldsymbol{x}} = \left| \det \boldsymbol{T} \right| \mathsf{M}_{ij},$$

where the integral is computed using a quadrature rule, or even manually for the lowest-order cases. It is thus possible to compute the reference mass matrix only once, store it, and obtain the physical mass matrix by a simple rescaling. Even if this procedure requires some computation, especially at high order it enables huge memory savings and data reuse, which are central for a GPU implementation of DG. The same idea can be applied to the stiffness matrix too, however in multiple dimensions the procedure is a bit more involved. In the following we will use the term differentiation matrix instead of stiffness matrix; the reason for this will be clear in the next section. Let

$$\nabla = \begin{bmatrix} \frac{\partial}{\partial x} \\ \frac{\partial}{\partial y} \end{bmatrix}, \qquad \hat{\nabla} = \begin{bmatrix} \frac{\partial}{\partial \xi} \\ \frac{\partial}{\partial \eta} \end{bmatrix}.$$

By the chain rule we have that

$$\boldsymbol{T}^{\top} \left( \nabla N_i^{T_n} \circ \mathsf{T} \right) = \hat{\nabla} (N_i^{T_n} \circ \mathsf{T}) \quad \implies \quad \nabla N_i^{T_n} = \boldsymbol{T}^{-\top} \left( (\hat{\nabla} \hat{N}_i) \circ \mathsf{T}^{-1} \right),$$

which allows us to write the differentiation matrix in the direction  $w \in \{x, y\}$  as

$$\mathsf{D}_{ij,w}^{T_n} = \int_{T_n} \frac{\partial N_j^{T_n}(\boldsymbol{x})}{\partial w} N_i^{T_n}(\boldsymbol{x}) d\boldsymbol{x} = |\det \boldsymbol{T}| \sum_{\hat{w} \in \{\xi, \eta\}} \boldsymbol{T}_{w\hat{w}}^{-\top} \int_{T_{ref}} \frac{\partial \hat{N}_j(\hat{\boldsymbol{x}})}{\partial \hat{w}} \hat{N}_i(\hat{\boldsymbol{x}}) d\hat{\boldsymbol{x}}$$

(1.28)

$$= |\det \mathbf{T}| \sum_{\hat{w} \in \{\xi, \eta\}} \mathbf{T}_{w\hat{w}}^{-\top} \mathsf{D}_{ij,\hat{w}}. \tag{1.29}$$

The last formula in particular is telling us that the differentiation matrix in the physical direction w is computed as a linear combination of the differentiation matrices in the reference directions  $\hat{w}$ . The linear combination is weighted by the coefficients of  $T^{-\top}$ , which turns out to be the inverse transpose of the Jacobian of T.

Finally, also the integral appearing in the boundary term can be pre-calculated, and gives rise to the *lifting matrix*. In the 1D case shown above, the lifting matrix reduces to a  $2 \times 2$  identity matrix, however in the multi-dimensional case the structure depends on the type of element. We postpone the discussion of the lifting matrix to the next section.

## 1.4 The Discontinuous Galerkin method for Maxwell equations

The 1D conservation law (1.13) is generalized to multiple dimensions as

$$Q \frac{\partial \boldsymbol{q}}{\partial t} + \nabla \cdot \boldsymbol{F}(\boldsymbol{q}) = \boldsymbol{g},$$

where  $q \in \mathbb{R}^n, n \in \mathbb{N}$  is the vector of the *n* state variables, or state vector,  $Q \in \mathbb{R}^{n \times n}$  is the matrix of the material parameters, g are the sources and F is the flux function. In particular

$$\nabla \cdot \mathbf{F} = \sum_{w} \frac{\partial F_w(\mathbf{q})}{\partial w}, \quad w \in \{x, y, z\},$$

if we assume to be working in  $\mathbb{R}^3$ . The Maxwell's equations (1.10)-(1.11) can be written in form of a conservation law [2] by setting

$$\mathcal{Q} = \begin{bmatrix} \epsilon & 0 \\ 0 & \mu \end{bmatrix}, \quad \boldsymbol{q} = \begin{bmatrix} \boldsymbol{e} \\ \boldsymbol{h} \end{bmatrix}, \quad \boldsymbol{F} = \begin{bmatrix} -\boldsymbol{F_h} \\ \boldsymbol{F_e} \end{bmatrix}, \quad \boldsymbol{g} = \boldsymbol{0},$$

where, by letting  $\hat{\boldsymbol{e}}_i$  be the *i*-th vector of the canonical basis of  $\mathbb{R}^3$ ,

$$m{F}_A = egin{bmatrix} (\hat{m{e}}_0 imes m{A})^T \ (\hat{m{e}}_1 imes m{A})^T \ (\hat{m{e}}_2 imes m{A})^T \end{bmatrix} = egin{bmatrix} 0 & A_z & -A_y \ -A_z & 0 & A_x \ A_y & -A_x & 0 \end{bmatrix}.$$

Notice that  $\nabla \cdot \mathbf{F}_A = \nabla \times \mathbf{A}$ ; in addition we consider a piecewise constant flux function. We proceed as usual by testing the differential equation with a test function  $\mathbf{v}$  and integrating on  $\Omega$

$$Q \frac{\partial}{\partial t} \int_{\Omega} \boldsymbol{q} \cdot \boldsymbol{v} \, dV, + \int_{\Omega} (\nabla \cdot \boldsymbol{F}) \cdot \boldsymbol{v} \, dV = \int_{\Omega} \boldsymbol{g} \cdot \boldsymbol{v} \, dS.$$

As in the 1D case we proceed elementwise integrating by parts twice and introducing the numerical flux  $F^*$ :

$$Q \frac{\partial}{\partial t} \int_{T} \boldsymbol{q} \cdot \boldsymbol{v} \, dV + \int_{T} (\nabla \cdot \boldsymbol{F}(\boldsymbol{q})) \cdot \boldsymbol{v} \, dV = \int_{T} \boldsymbol{g} \cdot \boldsymbol{v} dV + \int_{\partial T} (\boldsymbol{\hat{n}} \cdot (\boldsymbol{F}(\boldsymbol{q}) - \boldsymbol{F}^*) \cdot \boldsymbol{v} \, dS.$$

Also for the Maxwell's equations it is possible to define the centered and the upwind fluxes [2, 3]. In this case however, the fluxes are not as simple as in the 1D case. The expression for the centered fluxes is

$$oldsymbol{\hat{n}}\cdotoldsymbol{F}^* = egin{bmatrix} -oldsymbol{\hat{n}} imes\{oldsymbol{h}\}\ oldsymbol{\hat{n}} imes\{oldsymbol{e}\} \end{bmatrix},$$

whereas the expression for the upwind fluxes is

$$oldsymbol{\hat{n}}\cdotoldsymbol{F}^* = egin{bmatrix} -oldsymbol{\hat{n}} imes\{oldsymbol{h}\} - rac{Y}{2}oldsymbol{\hat{n}} imes(\llbracketoldsymbol{e}\rrbracket imesoldsymbol{\hat{n}}) \ oldsymbol{\hat{n}} imes\{oldsymbol{e}\} - rac{Z}{2}oldsymbol{\hat{n}} imes(\llbracketoldsymbol{h}\rrbracket imesoldsymbol{\hat{n}}) \end{pmatrix},$$

where  $Z = Y^{-1} = \sqrt{\mu/\epsilon}$  [2, 3]. In addition, on the boundary it holds

$$\hat{\boldsymbol{n}} \cdot \boldsymbol{F} = \begin{bmatrix} -\hat{\boldsymbol{n}} \times \boldsymbol{h} \\ \hat{\boldsymbol{n}} \times \boldsymbol{e} \end{bmatrix},$$

therefore it is now possible to compute the expression of the whole surface term on the right-hand side in the two cases. For the centered fluxes we have

$$\hat{m{n}}\cdot(m{F}-m{F}^*)=rac{1}{2}egin{bmatrix} \hat{m{n}} imes[\![m{h}]\!] \ -\hat{m{n}} imes[\![m{e}]\!] \end{bmatrix},$$

whereas for the upwind fluxes we have

$$\hat{\boldsymbol{n}} \cdot (\boldsymbol{F} - \boldsymbol{F}^*) = \frac{1}{2} \begin{bmatrix} \hat{\boldsymbol{n}} \times [\![\boldsymbol{h}]\!] - Y \hat{\boldsymbol{n}} \times ([\![\boldsymbol{e}]\!] \times \hat{\boldsymbol{n}}) \\ -\hat{\boldsymbol{n}} \times [\![\boldsymbol{e}]\!] - Z \hat{\boldsymbol{n}} \times ([\![\boldsymbol{h}]\!] \times \hat{\boldsymbol{n}}) \end{bmatrix}.$$

We remark that in both cases the surface terms are functions of only the jumps of the fields, fact that must be taken into account in the implementation.

The compact form of the equation can now be expanded in the three electric and the three magnetic components. In the case of the centered fluxes for example, we obtain the element-local electric equations

$$\epsilon \frac{\partial}{\partial t} \int_{T} e_{x} v \, dT - \int_{T} \frac{\partial h_{z}}{\partial y} v \, dT + \int_{T} \frac{\partial h_{y}}{\partial z} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{y} \llbracket h_{z} \rrbracket - \hat{n}_{z} \llbracket h_{y} \rrbracket) v \, dS - \int_{T} j_{x} v \, dT,$$

$$\epsilon \frac{\partial}{\partial t} \int_{T} e_{y} v \, dT + \int_{T} \frac{\partial h_{z}}{\partial x} v \, dT - \int_{T} \frac{\partial h_{x}}{\partial z} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{z} \llbracket h_{x} \rrbracket - \hat{n}_{x} \llbracket h_{z} \rrbracket) v \, dS - \int_{T} j_{y} v \, dT,$$

$$\epsilon \frac{\partial}{\partial t} \int_{T} e_{z} v \, dT - \int_{T} \frac{\partial h_{y}}{\partial x} v \, dT + \int_{T} \frac{\partial h_{x}}{\partial y} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{x} \llbracket h_{y} \rrbracket - \hat{n}_{y} \llbracket h_{x} \rrbracket) v \, dS - \int_{T} j_{z} v \, dT,$$

$$(1.30)$$

where  $j_x, j_y$  and  $j_z$  are the volumetric sources, and the element-local magnetic equations

$$\mu \frac{\partial}{\partial t} \int_{T} h_{x} v \, dT + \int_{T} \frac{\partial e_{z}}{\partial y} v \, dT - \int_{T} \frac{\partial e_{y}}{\partial z} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{z} \llbracket e_{y} \rrbracket - \hat{n}_{y} \llbracket e_{z} \rrbracket) v \, dS,$$

$$\mu \frac{\partial}{\partial t} \int_{T} h_{y} v \, dT - \int_{T} \frac{\partial e_{z}}{\partial x} v \, dT + \int_{T} \frac{\partial e_{x}}{\partial z} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{x} \llbracket e_{z} \rrbracket - \hat{n}_{z} \llbracket e_{x} \rrbracket) v \, dS, \qquad (1.31)$$

$$\mu \frac{\partial}{\partial t} \int_{T} h_{z} v \, dT + \int_{T} \frac{\partial e_{y}}{\partial x} v \, dT - \int_{T} \frac{\partial e_{x}}{\partial y} v \, dT = \frac{1}{2} \int_{\partial T} (\hat{n}_{y} \llbracket e_{x} \rrbracket - \hat{n}_{x} \llbracket e_{y} \rrbracket) v \, dS.$$

The surface sources (for example a plane wave source) do not appear in the above equations and can be implemented simply by modifying the jumps [3].

The equations so obtained resemble closely what we obtained in the 1D case. In particular, we remark that for each equation there is a mass term and two differentiation terms, in addition to the flux term that we are going to discuss.

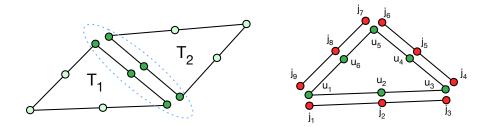

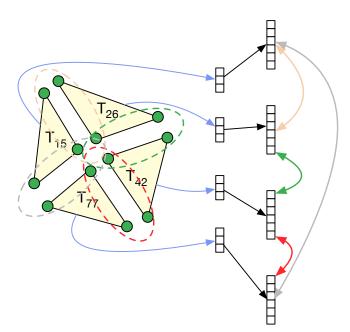

In a setting where a nodal basis (like the Lagrange basis) is used, the jumps are computed simply by subtracting the degrees of freedom on the face shared by two adjacent triangles  $T_1$  and  $T_2$  (Figure 1.3 left). The process is done between each pair of adjacent

Figure 1.3: Degrees of freedom involved in the computation of the fluxes between two triangles  $T_1$  and  $T_2$  (left) and association between flux DoFs and element DoFs (right). Both pictures are in the case where Lagrange basis functions are used.

elements, obtaining a new vector of jumps for each face (Figure 1.3 left). The jumps so obtained are subsequently used, as we remarked before, to compute the flux in the boundary of the element with an expression comparable to

$$\int_{\partial T} \alpha \llbracket u \rrbracket v \, dS = \sum_{F \in \partial T} \int_{F} \alpha \llbracket u \rrbracket_{|F} v \, dS, \tag{1.32}$$

where we split the integral on the boundary in a sum of integrals on the single faces. We recognize that the integral on the face F is actually the mass matrix  $\mathsf{M}^F$  of F whose entries we denote as  $m_{ij}^F$ . For second order elements for example, such a mass matrix has dimension  $3\times 3$ . In that case, if we denote with  $\mathsf{j}=\{j_i\}_{i\in\{1,\dots,9\}}$  the vector collecting all the jumps on the faces of a triangle T (Figure 1.3 left) and with  $\mathsf{u}=\{u_i\}_{i\in\{1,\dots,6\}}$  the local DoFs of T, we realize that a term like (1.32) is computed as the matrix-vector product  $\mathsf{u}=\mathsf{L}\mathsf{j}$  where

$$\mathsf{L} = \begin{bmatrix} m_{11}^{F_1} & m_{12}^{F_1} & m_{13}^{F_1} \\ m_{21}^{F_1} & m_{22}^{F_1} & m_{23}^{F_1} \\ m_{31}^{F_1} & m_{32}^{F_1} & m_{33}^{F_1} \\ \end{bmatrix} \begin{bmatrix} m_{11}^{F_2} & m_{12}^{F_2} & m_{13}^{F_2} \\ m_{21}^{F_2} & m_{22}^{F_2} & m_{23}^{F_2} \\ m_{31}^{F_2} & m_{32}^{F_2} & m_{33}^{F_2} \\ \end{bmatrix} \begin{bmatrix} m_{11}^{F_3} & m_{11}^{F_3} & m_{12}^{F_3} & m_{13}^{F_3} \\ m_{21}^{F_2} & m_{22}^{F_2} & m_{23}^{F_2} \\ \end{bmatrix}.$$

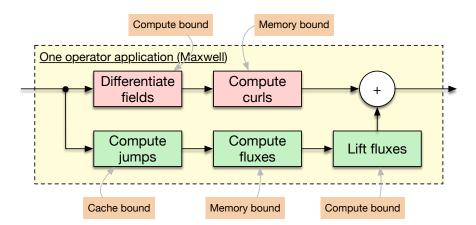

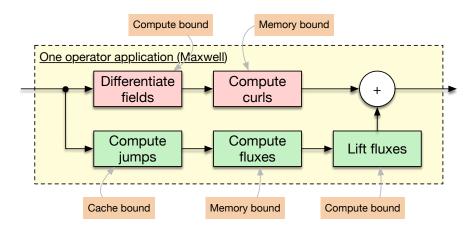

From the previous discussion we can deduce that, once implemented, the resulting computational structure will be that depicted in Figure 1.4. In particular, we recognize a volumetric path and a boundary path. The volumetric path consists of the following phases:

- Differentiate fields: the spatial derivatives of the six fields are computed,

- Compute curls: using the derivatives computed in the previous step, the curls are computed by subtracting the degrees of freedom of the corresponding fields.

Figure 1.4: Computational steps required in order to do one application of the Discontinuous Galerkin operator.

The boundary path, on the other hand, corresponds to the following phases:

- Compute jumps: compute all the quantities [[·]] appearing in the equations and store them,

- Compute fluxes: using the jumps computed in the previous step, compute the full expressions appearing inside the integrals on the right-hand sides of (1.30) and (1.31),

- Lift fluxes: bring the fluxes from the surfaces to the volumes using the matrix L.

#### Time integration

In the GMSH/DG code, the time integration of the equations is done via the Runge-Kutta 4 method or via the leapfrog method. Both methods are standard and we refer the reader to [1] and [3] for the details.

## Chapter 2

## **Graphics Processing Units**

GPUs were born as specialized electronic circuits designed to accelerate image manipulation and processing. However, their highly parallel structure can be used for general-purpose computing, especially when dealing with embarrassingly parallel problems, to reach better performance by mixing GPU and CPU execution.

GPUs must not be seen as a panacea though, instead they have to be seen as a useful resource that can be used when certain conditions are met. In fact, not all tasks can be parallelized in the expected way on GPUs: some of them are embarrassingly parallel and benefit a lot from GPU parallelization; others on the other hand may have many dependencies between data, which makes using GPUs pointless.

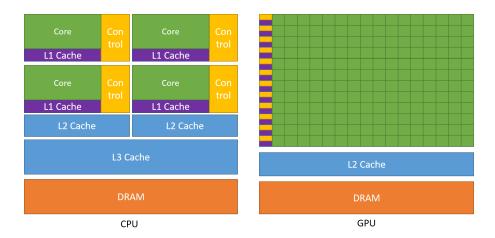

Another crucial difference between CPUs and GPUs is that the first can run tens of threads in parallel, are equipped with broad instruction sets and are more devoted to data caching and control flow; GPUs instead can run thousands of threads in parallel, which means that most transistors are devoted to data processing and very few are used for control flow and caching (an example of this can be seen in Figure 2.1). The computing power derived from the transistors is exploited using the SIMT (Single Instruction, Multiple Thread) execution model in which a bundle of thread (possibly) executes the same instruction on usually different data.

Finally, it has to be noted that the programming of parallel systems is not an easy task. In the early days of general-purpose computing on GPUs (GPGPU), solving a problem on a GPU required it to be reformulated to fit into the graphics pipeline, for example arrays would become textures, the processing to be done would be a shader and the computing was done during the rendering phase: this was the only interface to GPU hardware. Modern GPGPU makes developing solutions for GPUs easier, with the emergence of programming models and platforms like CUDA and OpenCL, which allow developers to ignore the underlying graphical concepts in favor of high-performance computing concepts. Some of these platforms are developed by graphics unit vendors, like CUDA for NVIDIA GPUs [9] and ROCm for AMD GPUs [10], while others are open standards for heterogeneous computing such as OpenCL [11] and SYCL [12], that also support other accelerators like FPGAs, DSPs and custom chipsets [12]. As CUDA is our platform of choice, the rest of this chapter will be heavily based on the CUDA Toolkit documentation [9].

Figure 2.1: GPUs devote more transistors to data processing (in green) and have much fewer transistors for control units (in yellow) and caches (in purple) (NVIDIA Corporation 2022).

#### 2.1 Architecture fundamentals

GPU cards are accelerators connected to the CPU via a bus (e.g. a PCIe bus) which is used for data exchange. The typical steps involved in using a GPU for GPGPU are the following:

- 1. Data is copied to the GPU memory

- 2. Computation is performed on the GPU

- 3. Results are copied back to the CPU

Different programming models have different terminology to refer to the components of GPUs, we will use CUDA terminology because it is the one used throughout the work of this thesis.

CUDA is a general purpose parallel computing platform and programming model introduced by NVIDIA in 2006 for their GPUs to truly expose their devices as a generic data-parallel computing device. Before CUDA, GPU could only be programmed using a graphics API, imposing a high learning curve to the novices and the overhead of an inadequate API to non-graphical applications.

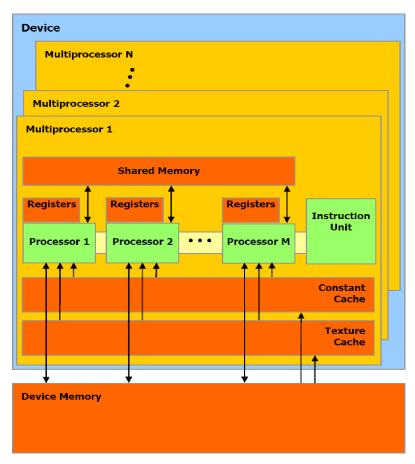

The major point of CUDA was thus having a completely dedicated programming model for developing general-purpose applications in a way that is familiar to specialists in parallel computing. Therefore, from that point on a GPU could be really used as a highly-parallel device and as such, organized in a set of processors, called *Streaming Multiprocessors*, made

of compute elements, called *CUDA Cores* that are hardware units that run computations. Figure 2.2 shows how a GPU device is organized. This type of organization is much more similar to a collection of CPUs, each with its own cores, rather than a "black-box" accessible through a graphics API.

Figure 2.2: The hardware model of an NVIDIA GPU, showing the array of streaming multiprocessors with their on-chip memories, cores and instruction schedulers and the off-chip device memory (NVIDIA Corporation 2007).

#### 2.1.1 CUDA Compute Capability

In CUDA terminology, the *Compute Capability* (CC) of a device is a version number that identifies the features supported by the GPU hardware. Knowing the hardware compute capability is crucial to fine tune the performance of applications; in fact, many strategies to improve performance are based on values that depend on the hardware version.

Compute capability version number is composed by a major revision number X and a minor revision number Y, and it is denoted by X.Y. Devices with the same revision

number share the same *core architecture* which is identified by a codename. Some of core architectures are consumer-oriented, while others are HPC-oriented. The latter have a much higher bandwidth thanks to the use of HBM memory instead of GDDR memory and have more double-precision floating-point core units than the consumer-oriented GPUs. In this work, when analyzing single GPU performance, we worked with compute capability 7.0, based on the *Volta* core architecture.

#### 2.1.2 Thread execution model

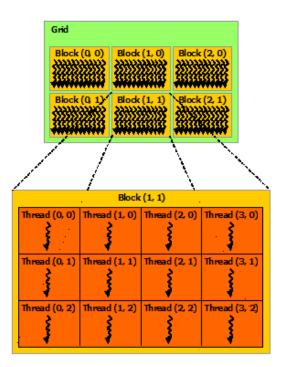

The programming model allows the developer to define C++ functions, called *kernels*, which are executed in parallel by N threads on N different CUDA cores. CUDA Threads are logically grouped in *thread blocks* that can be organized into a one-dimensional, two-dimensional or three-dimensional layout to provide a natural way to invoke a kernel on different data layouts. Blocks are then also organized into a one-dimensional, two-dimensional or three-dimensional *kernel grid* of thread blocks. An example of this organization can be seen in Figure 2.3, showing a bidimensional grid in which also blocks are also bidimensional. The dimensions of grids and blocks are independent of each other.

Figure 2.3: Example of a bidimensional grid with bidimensional blocks (NVIDIA Corporation 2022).

From a hardware point of view, when a kernel is launched, the thread blocks are distributed among the streaming multiprocessors of the GPU. When a multiprocessor is given a thread block, it partitions it into groups of 32 threads called warps and each of them is issued one instruction by the instruction scheduler, called warp scheduler. The way a block is partitioned into warps is always the same, in fact each thread has a thread ID with respect to the grid, and each warp contains threads of consecutive, increasing thread IDs with the first warp containing thread 0.

Virtually, each thread of a warp may need to run a different instruction, for instance the pseudocode in Algorithm 1 shows a situation in which half of the warp executes an instruction and the other half another one. After the branch instruction has been executed only one instruction can be issued by the scheduler to the whole warp, thus half of the warp will be inactive while the other half will work.

```

if threadId < 16 then

| do something;

else

| do something else;

end</pre>

```

**Algorithm 1:** Pseudocode showing a situation in which some threads of the warp will be inactive while the others work.

So, the idea of SIMT execution model that GPUs implement is to make an efficient use of the limited warp schedulers – these are usually four per streaming multiprocessor – by having all threads performing the same instruction.

To fully exploit the capabilities of the processing elements the GPU provides, the organization of computation is usually different from a multicore computation on CPU. For instance, let us consider the vector sum between two vectors  $v = (v_1, \ldots, v_n)$  and  $u = (u_1, \ldots, u_n)$ . In the usual "CPU approach" one would loop over the index of the vectors and put the result in a new vector w, and in a multicore context we would split the vector into chunks and give each chunk to a process. On GPU the approach is different, in the sense that we use a much finer granularity: we launch a grid of n threads in which each thread computes the sum  $w_i = v_i + u_i$ , for  $i \in \{1, \ldots, n\}$ . Thus, computation on GPU is usually organized so that one thread is responsible for computing one output value of the given problem.

The Discontinuous Galerkin method is more complex than a vector sum: as explained in Subsection 1.3.4 the method ultimately approximates the solution by using piecewise polynomial functions attached to the mesh elements. Thus, to approximate the solution, once a base function is fixed (e.g. Lagrange polynomials) the values that the method will compute are the coefficients of the polynomials, that are called *degrees of freedom*. As

before, even if the computation is divided in many phases as will be shown in Chapter 3, the code organization of each kernel is such that each thread is responsible to perform the computations related to a single degree of freedom. This means that in the heaviest computations we deal with millions of parallel threads, which may seem too much, but actually it is exactly what we want – to a certain degree – to obtain maximum occupancy and latency hiding, concepts that we will explain further in the upcoming section.

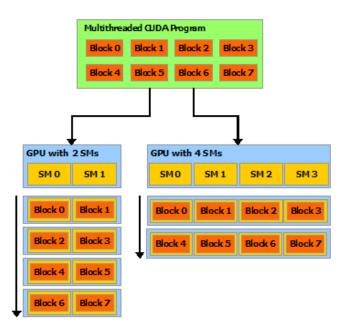

Having more threads also means more thread blocks, which are a very handy abstraction for dealing with scalability. As Figure 2.4 shows, GPUs with more streaming multiprocessors will automatically be more performant with respect to a GPU with fewer multiprocessors, because the thread blocks will be distributed among more multiprocessors allowing for a more efficient parallelization.

Figure 2.4: Example of how a kernel grid can automatically scale depending on the number of streaming multiprocessors on a GPU (NVIDIA Corporation 2022).

#### 2.1.3 GPU memories

From a hardware point of view, we can find two types of memories on a GPU board: device memory (SDRAM) and on-chip caches. High-performance graphics accelerators for general-purpose computing usually use High Bandwidth Memory (HBM) as SDRAM while consumer GPUs for gaming usually employ GDDR memories. On-chip memories include a L2 cache that is shared by all SMs and other caches for each SM that depend on the device compute capability. A generic view of this organization can be seen in Figure 2.2.

Hardware memories are organized in different ways from a software point of view based on what they memorize, how they exploit caches and what they are optimized for.

Global memory Global memory resides in device memory, is the same for all threads, and it is where data from the host CPU is transferred and from which is fetched by the CPU to get the results. Global memory accesses from the GPU are supported by the L2 cache. This memory is persistent across kernel launches by the same application.

**Registers** Each thread has access to a *private memory*, used for local variables in a kernel. These memory locations are called registers and there are a limited number of these which depends on the device compute capability.

**Local memory** Another read-write memory area is the local memory, which also resides in device memory and therefore has the same performance of global memory. Local memory accesses occur only for some type of variables, such as arrays indexed with non-constant quantities, large structures or arrays that would consume too much register space, and register spills meaning any variable if the kernel uses more registers than available. Register spills are cached in L1 cache. Normally, local memory accesses should be avoided to achieve good performance.

Texture and surface memory Texture and surface memory are two kinds of memories that reside on device memory. Accessing texture memory is done by using the texture object API, thus creating texture objects (a piece of texture memory) at runtime that cannot be subsequently modified. A texture can be addressed as a one-, two- or three-dimensional array, while elements of the texture are called *texels* and can store integers or single floating-point values. The texture width, height, and depth refer to the size of the array in each dimension. An interesting capability of textures fetching is that during fetching the value returned by specifying the coordinates can be interpolated with the neighboring values, thus performing linear interpolation for one-dimensional textures, bilinear interpolation for two-dimensional textures.

Surface memory is also accessed through its API, by creating surfaces objects, that differently from textures, can be modified through the API calls. Thus, surfaces are very similar to textures, except for being writable and not supporting interpolation during fetching.

Both texture and surface memory accesses are cached into an on-chip texture cache, that depending on the compute capability of the device could be dedicated or unified with other memories.

Shared memory Each thread has access to a shared memory visible to all threads of the block, this memory resides on-chip and because of that, it has higher bandwidth and lower latency than global memory. Threads within a block can cooperate by sharing data through this memory as a kind of communication between threads, however one has to enforce synchronization across threads in the same block to make use of data among different warps. This is due to the fact that the scheduler operates on warps, so for instance a warp that need to read from shared memory some data written by another warp could read incorrect data if synchronization had not been enforced. In order to obtain the best performance, the access to shared memory must follow some conditions that will be explained in Section 2.2.2.

**Constant memory** Finally, constant memory is a read-only memory which resides on device memory and that is cached in constant cache.

Constant, texture, L1 caches and shared memory organization on the streaming multiprocessor change for each compute capability, therefore to get a clearer picture we summarize caches and their uses in Table 2.1.

|        | Dedicated read-only constant cache                     |

|--------|--------------------------------------------------------|

| CC 3.x | Unified L1 cache for local memory and shared memory    |

|        | Dedicated read-only data cache for texture memory      |

|        | Dedicated read-only constant cache                     |

| CC 5.x | Unified L1/texture cache for global and texture memory |

|        | Dedicated shared memory                                |

|        | Dedicated read-only constant cache                     |

| CC 6.x | Unified L1/texture cache for global and texture memory |

|        | Dedicated shared memory                                |

| CC 7.x | Dedicated read-only constant cache                     |

| CC 1.x | Unified L1/texture cache and shared memory             |

| CC 8.x | Dedicated read-only constant cache                     |

| CC 8.x | Unified L1/texture cache and shared memory             |

Table 2.1: How memories organization on the streaming multiprocessor change per each compute capability.

#### 2.2 Performance optimization

To achieve the best performance on GPU one has to have a deep knowledge of the platform on which a solution is being implemented and of the problem itself. The CUDA programming guide asserts that performance optimization revolves around some basic strategies:

- Maximize parallel execution to achieve maximum utilization;

- Optimize memory usage to achieve maximum memory throughput;

- Optimize instruction usage to achieve maximum instruction throughput;

A software using a GPU as an accelerator, may be composed by different parts that require different kinds of optimization. The usual performance limiters are the floating-point operation throughput and the memory throughput, depending on the kernel.

#### 2.2.1 Maximize utilization

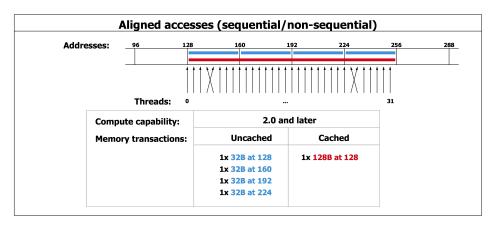

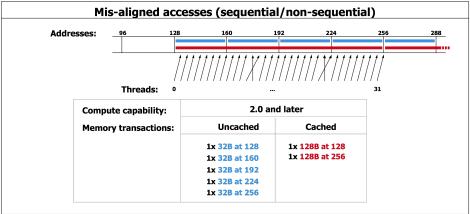

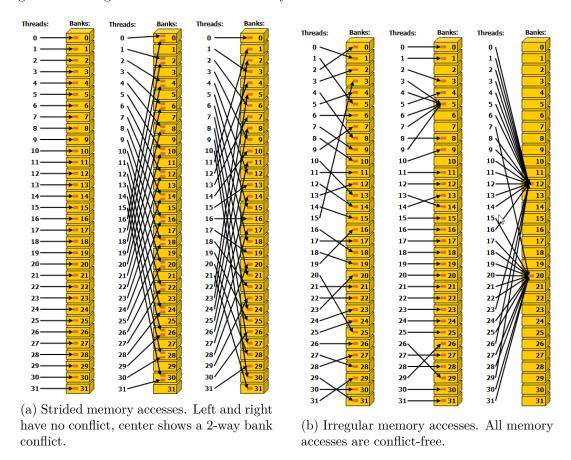

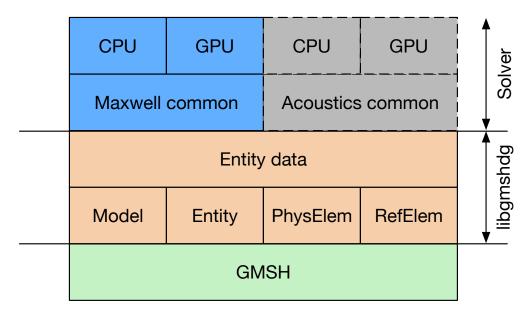

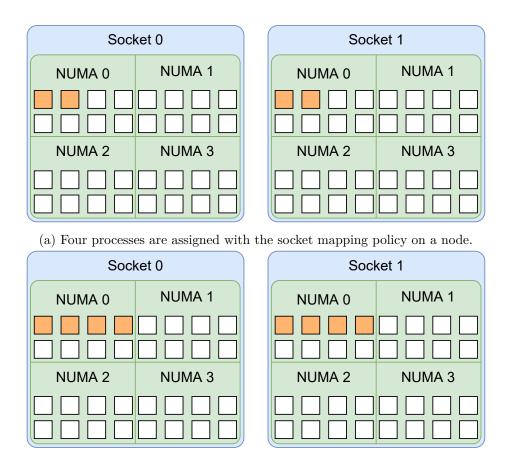

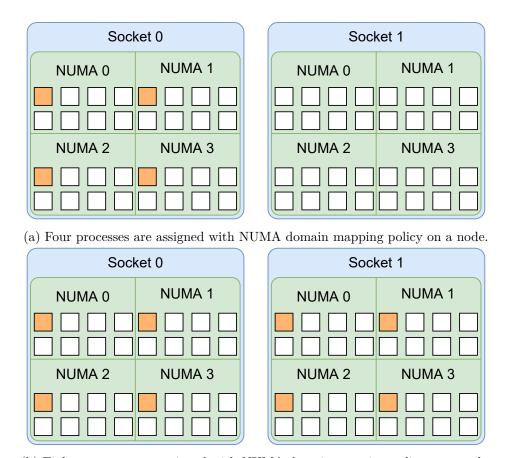

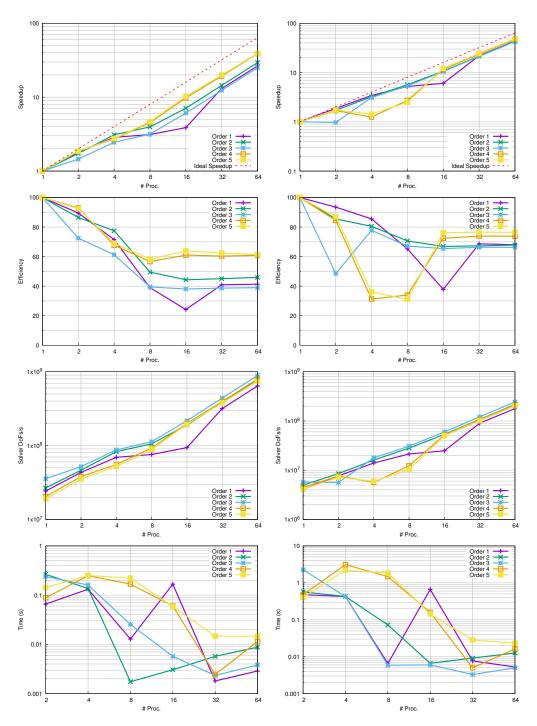

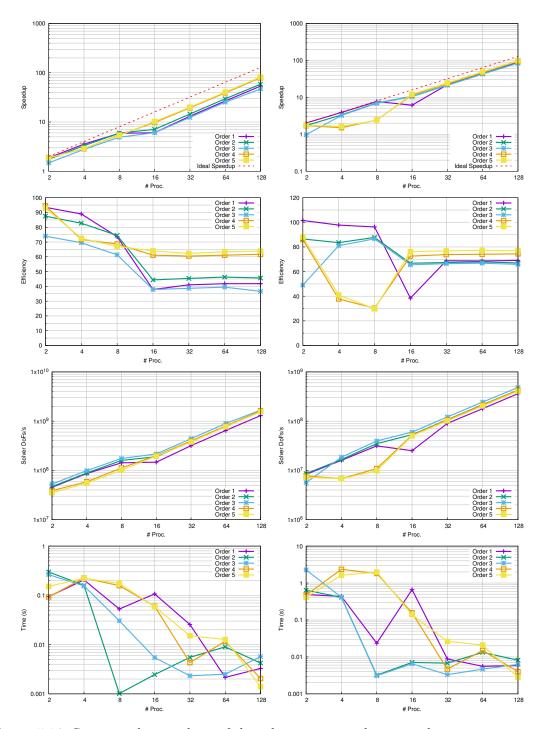

To make the most of the GPU resources, applications must be developed so that it is possible to exploit as much as possible parallelism over the components of the system. The first kind of parallelism to be exploited is the one between host (CPU) and devices (GPU): one has to design their application to have all components working at the same time.