# Implementation of video streaming via USB on a microcontroller

#### Alex ROUSSEAU

Thesis presented to obtain the degree of :

Master of Science in Electrical Engineering

Thesis supervisor : Bernard **BOIGELOT**

Internship supervisor : Alex **ROSCA** at *Get Your Way*

Academic year: 2024 - 2025

# **Abstract**

# Implementation of video streaming via USB on a microcontroller

#### Alex Rousseau

Master of Science in Electrical Engineering University of Liége - Academic year: 2024 - 2025

Thesis supervisor : Bernard **BOIGELOT**Internship supervisor : Alex **ROSCA** at Get Your Way

The company *Get Your Way* has developed a lightweight Head Mounted Display (HMD) device that is able to display a graphical interface. The goal of this Master's thesis is to develop a firmware that implements the reception of a video stream through USB-C, and the display of said video stream on the HMD screen.

The main task is the implementation of a USB Video Class (UVC) driver for the RZ/A2M microcontroller present inside the HMD. A USB 2.0 host driver library was already implemented but had to be modified extensively to support the UVC driver. To that end, the USB 2.0, UVC 1.0 and EHCl standards were studied and are detailed in depth in this thesis.

The decoding and display of video frames was implemented by integrating relevant sections of sample codes provided by the company which designed the microcontroller, Renesas. The description of these modules are thus less detailed than for the UVC driver.

The firmware was first implemented on a a development board, for easier debugging. It was then supposed to be ported to the HMD board, but a hardware limitation was found. As the new board was not ready at the time of writing this thesis, the porting process was only described and not carried out.

A state of the art of the physical interfaces which allow video streaming was also performed, with a focus on those commonly found in cameras. The intent was to determine the best interface for a possible new version of the HMD, as well as broaden personal knowledge.

# Declaration on the use of automatic tools for writing the manuscript

I hereby certify that I have not used any generative intelligence tool in the writing of text, graphics, images, or data reproduced in this manuscript.

The only automatic tool used to write this document is a spelling checker integrated in the text editor.

# **Contents**

| 1 | Intro | duction  | 1                       |

|---|-------|----------|-------------------------|

|   | 1.1   | Get Yo   | ur Way                  |

|   |       | 1.1.1    | The Company             |

|   |       | 1.1.2    | arDent Display          |

|   | 1.2   | Objecti  | ve                      |

|   | 1.3   | Thesis   | Organization            |

| 2 | Stat  | e of the | Art                     |

|   | 2.1   | Physica  | I Interfaces            |

|   |       | 2.1.1    | DVI                     |

|   |       | 2.1.2    | HDMI                    |

|   |       | 2.1.3    | FireWire                |

|   |       | 2.1.4    | PCle                    |

|   |       | 2.1.5    | MIPI CSI                |

|   |       | 2.1.6    | DVP                     |

|   |       | 2.1.7    | SDI                     |

|   |       | 2.1.8    | Camera Link             |

|   |       | 2.1.9    | CoaXPress               |

|   |       | 2.1.10   | GMSL                    |

|   |       | 2.1.11   | FPD Link                |

|   |       | 2.1.12   | Ethernet                |

|   |       | 2.1.13   | Thunderbolt             |

|   |       | 2.1.14   | USB                     |

|   |       |          | 2.1.14.1 USB Protocols  |

|   |       |          | 2.1.14.2 USB Classes    |

|   |       |          | 2.1.14.3 USB Connectors |

|   | 2.2   | Video (  | Compression Formats     |

|   |       | 2.2.1    | DSC                     |

|   |       | 2.2.2    | MJPEG                   |

|   |       | 2.2.3    | MJPEG 2000              |

|   |       | 2.2.4    | MPEG 4                  |

|   |       | 2.2.5    | H.264                   |

|   |       | 2.2.6    | H.265                   |

|   | 2.3   | Case St  | tudy                    |

|   |       | 221      | Scope Statement         |

#### TABLE OF CONTENTS

|   |     | 2.3.2 Technology Comparison              | 13 |

|---|-----|------------------------------------------|----|

|   |     | 2.3.3 Summary                            | 14 |

| 3 | USB | 2.0 Standard                             | 15 |

|   | 3.1 | General Architecture                     | 15 |

|   | 3.2 | USB Devices                              | 16 |

|   | 3.3 | USB Communications                       | 17 |

|   |     | 3.3.1 Pipes                              | 17 |

|   |     | 3.3.2 Transfers                          | 18 |

|   |     | 3.3.3 Asynchronous Transfers             | 19 |

|   |     | 3.3.3.1 Control transfers                | 19 |

|   |     | 3.3.3.2 Bulk transfers                   | 20 |

|   |     | 3.3.4 Periodic Transfers                 | 20 |

|   |     | 3.3.4.1 Isochronous transfers            | 21 |

|   |     | 3.3.4.2 Interrupt transfers              | 21 |

|   | 3.4 | Device Attachment                        | 21 |

|   |     | 3.4.1 Dynamic detection                  | 21 |

|   |     | 3.4.2 Enumeration                        | 22 |

|   |     | 3.4.3 Configuration                      | 22 |

| 4 | UVC | Standard                                 | 23 |

| - | 4.1 | UVC Operational Architecture             |    |

|   |     | 4.1.1 VideoControl interface             |    |

|   |     | 4.1.2 VideoStreaming interface           |    |

|   | 4.2 | UVC Descriptors                          |    |

|   | 4.3 | UVC-Specific Requests                    |    |

|   |     | 4.3.1 Set request                        |    |

|   |     | 4.3.2 Get request                        |    |

|   |     | 4.3.3 Summary of VideoStreaming requests |    |

|   | 4.4 | VS Parameter Negotiation                 |    |

|   | 4.5 | UVC Video Stream                         |    |

| 5 | ЕЦζ | I Standard                               | 31 |

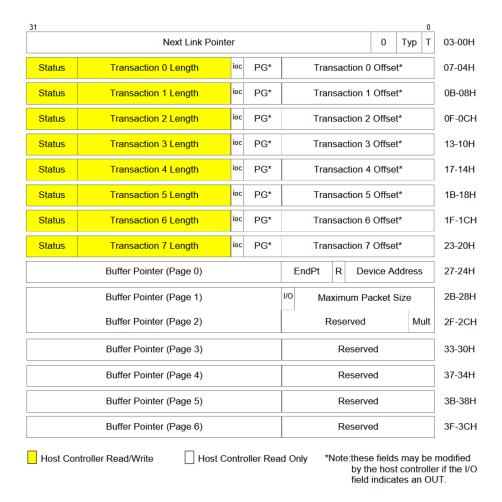

| J | 5.1 | iTD                                      |    |

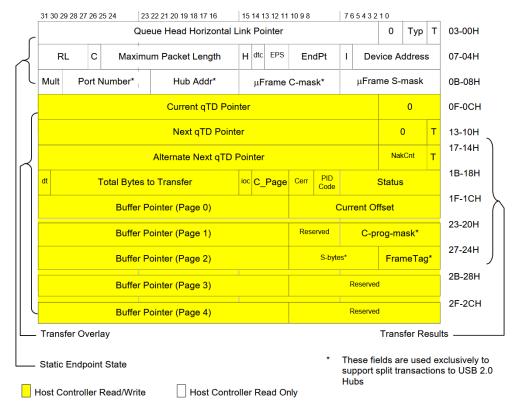

|   | 5.2 | qTD                                      |    |

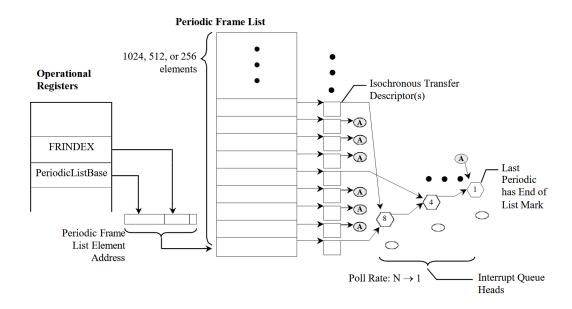

|   | 5.3 | Periodic Schedule                        |    |

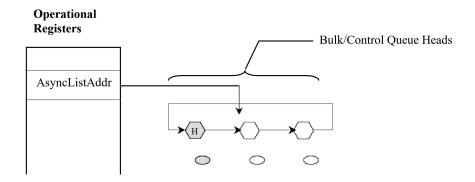

|   | 5.4 | Asynchronous Schedule                    |    |

| _ |     |                                          |    |

| 6 | •   | ementation on Development Board          | 37 |

|   | 6.1 | Board Characteristics                    |    |

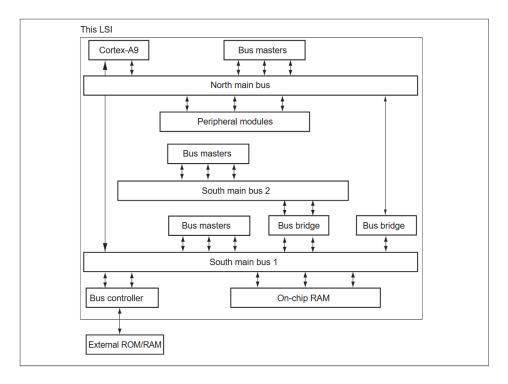

|   |     | 6.1.1 RZ/A2M Architecture                |    |

|   | 6.2 | On-chip Peripheral Connectivity          |    |

|   |     | 6.2.1 On-chip Peripheral Register Access |    |

|   |     | 6.2.2 Direct Memory Access               |    |

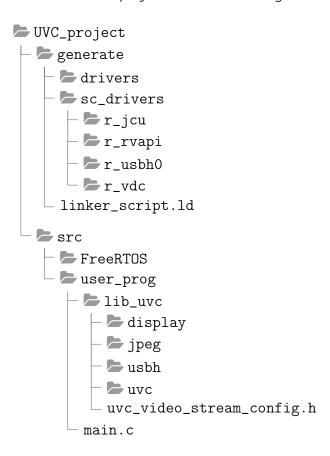

|   | 6.3 | UVC Application Architecture             |    |

|   | 6 1 | LISP Host Driver                         | 12 |

#### TABLE OF CONTENTS

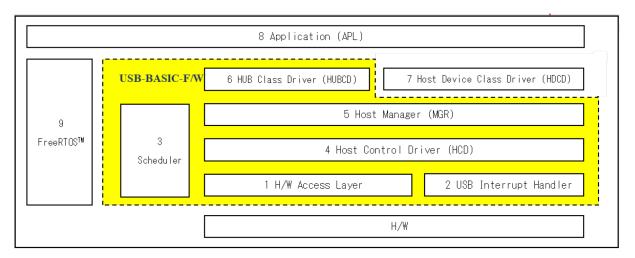

|   |     | 6.4.1  | USB Host Driver                         | Architecture       | <br> | <br> | <br> | <br> |  |  | 42 |

|---|-----|--------|-----------------------------------------|--------------------|------|------|------|------|--|--|----|

|   |     |        | 6.4.1.1 Applica                         | ntion              | <br> | <br> | <br> | <br> |  |  | 42 |

|   |     |        | 6.4.1.2 HDCD                            |                    | <br> | <br> | <br> | <br> |  |  | 43 |

|   |     |        | 6.4.1.3 HUBCI                           | O                  | <br> | <br> | <br> | <br> |  |  | 43 |

|   |     |        | 6.4.1.4 MGR                             |                    | <br> | <br> | <br> | <br> |  |  | 43 |

|   |     |        | 6.4.1.5 HCD                             |                    | <br> | <br> | <br> | <br> |  |  | 44 |

|   |     |        | 6.4.1.6 Schedu                          | ler                | <br> | <br> | <br> | <br> |  |  | 44 |

|   |     |        | 6.4.1.7 USB Ir                          | terrupt Handler .  | <br> | <br> | <br> | <br> |  |  | 44 |

|   |     |        | 6.4.1.8 FreeRt                          | OS                 | <br> | <br> | <br> | <br> |  |  | 45 |

|   |     |        | 6.4.1.9 H/W A                           | Access Layer       | <br> | <br> | <br> | <br> |  |  | 45 |

|   |     |        | ,                                       |                    |      |      |      |      |  |  | 45 |

|   |     | 6.4.2  | ,                                       | the USB Host Dri   |      |      |      |      |  |  | 46 |

|   |     | 0      |                                         | uration Parameters |      |      |      |      |  |  | 46 |

|   |     |        | _                                       | ller               |      |      |      |      |  |  | 46 |

|   |     |        | • • • • • • • • • • • • • • • • • • • • |                    |      |      |      |      |  |  | 48 |

|   | 6.5 | IISR H |                                         |                    |      |      |      |      |  |  | 50 |

|   | 0.5 | 6.5.1  | J                                       | on                 |      |      |      |      |  |  | 50 |

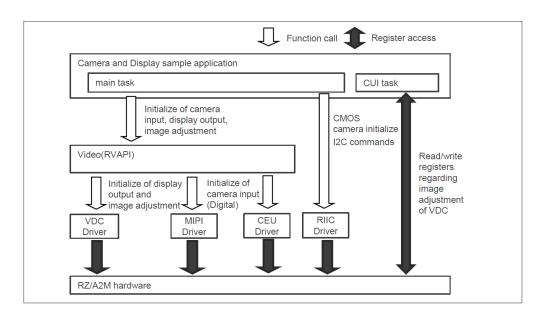

|   |     | 6.5.2  |                                         | egration           |      |      |      |      |  |  | 50 |

|   | 6.6 |        |                                         |                    |      |      |      |      |  |  | 50 |

|   | 0.0 | 6.6.1  | •                                       | on                 |      |      |      |      |  |  | 50 |

|   |     | 6.6.2  |                                         | egration           |      |      |      |      |  |  | 51 |

|   | 6.7 |        |                                         | =                  |      |      |      |      |  |  | 51 |

|   | 0.7 |        | =                                       |                    |      |      |      |      |  |  |    |

|   |     | 6.7.1  |                                         | on                 |      |      |      |      |  |  | 51 |

|   | 6.0 | 6.7.2  | ·                                       | egration           |      |      |      |      |  |  | 52 |

|   | 6.8 |        |                                         |                    |      |      |      |      |  |  | 53 |

|   |     | 6.8.1  | -                                       |                    |      |      |      |      |  |  | 53 |

|   |     | 6.8.2  |                                         | hine               |      |      |      |      |  |  | 54 |

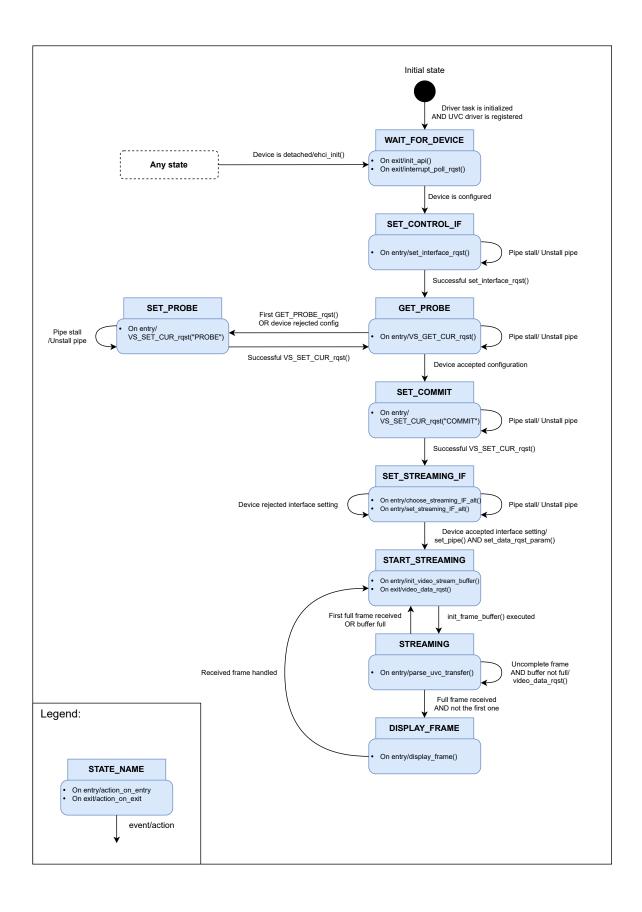

|   |     |        | -                                       | FOR_DEVICE         |      |      |      |      |  |  | 56 |

|   |     |        | _                                       | CONTROL_IF .       |      |      |      |      |  |  |    |

|   |     |        | 6.8.2.3 GET_                            | PROBE              | <br> | <br> | <br> | <br> |  |  | 57 |

|   |     |        |                                         | PROBE              |      |      |      |      |  |  | 57 |

|   |     |        | _                                       | COMMIT             |      |      |      |      |  |  | 57 |

|   |     |        | _                                       | STREAMING_IF       |      |      |      |      |  |  | 58 |

|   |     |        | 6.8.2.7 STAR                            | _STREAMING         | <br> | <br> | <br> | <br> |  |  | 58 |

|   |     |        |                                         | AMING              |      |      |      |      |  |  | 58 |

|   |     |        | 6.8.2.9 DISPL                           | AY_FRAME           | <br> | <br> | <br> | <br> |  |  | 59 |

|   |     |        | 6.8.2.10 Pipe S                         | TALL handling .    | <br> | <br> | <br> | <br> |  |  | 59 |

|   |     | 6.8.3  | Streaming Archit                        | ecture             | <br> | <br> | <br> | <br> |  |  | 60 |

|   |     |        |                                         |                    |      |      |      |      |  |  |    |

| 7 | -   |        | ing to the arDer                        |                    |      |      |      |      |  |  | 61 |

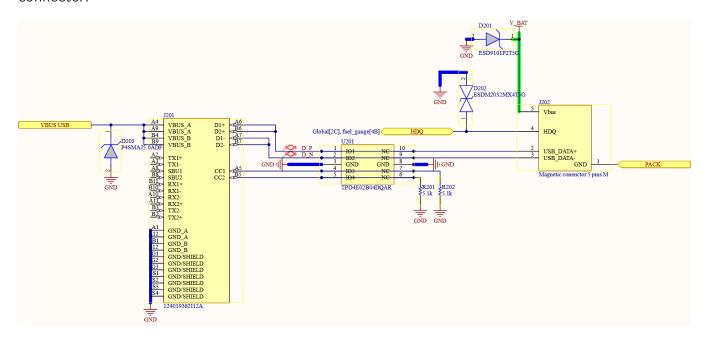

|   | 7.1 | arDent |                                         |                    |      |      |      |      |  |  | 61 |

|   |     | 7.1.1  |                                         |                    |      |      |      |      |  |  | 61 |

|   |     | 7.1.2  | Current Battery                         | Board              | <br> | <br> | <br> | <br> |  |  | 61 |

|   |     | 7.1.3  | New Battery Boa                         | nrd                | <br> | <br> | <br> | <br> |  |  | 63 |

|   | 7.2 | arDent | File Organization                       |                    | <br> | <br> | <br> | <br> |  |  | 63 |

|   |     |        |                                         |                    |      |      |      |      |  |  |    |

#### TABLE OF CONTENTS

|     | 7.3    | UVC Application Integration | 64              |

|-----|--------|-----------------------------|-----------------|

| 8   |        | clusion  Next Developments  | <b>66</b><br>67 |

| 9   | Anne   |                             | 68              |

|     | 9.1    | Get Your Way                | 68              |

|     |        | 9.1.1 Products              | 68              |

|     |        | 9.1.2 Target Markets        | 70              |

|     | 9.2    | Internship                  | 70              |

| Bil | oliogr | aphy                        | 71              |

# **List of Figures**

| 1.1                                    | arDent Display                           | 2              |

|----------------------------------------|------------------------------------------|----------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5        | USB bus topology                         |                |

| 4.1<br>4.2<br>4.3                      | UVC test camera configuration descriptor | 28             |

| 5.1<br>5.2<br>5.3<br>5.4               | iTD organization                         | 35             |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | LSI bus diagram                          |                |

| 7.1<br>7.2<br>7.3                      | Current arDent Battery Board             | 62<br>63<br>64 |

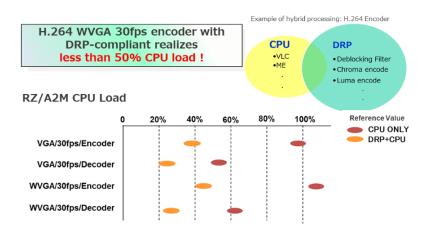

| 8.1                                    | Performance of H.264 codec on RZ/A2M DRP | 67             |

| 9.1<br>9.2                             | Get Your Way's logo                      |                |

# **List of Tables**

| 2.1 | Physical interfaces comparison | 14 |

|-----|--------------------------------|----|

| 3.1 | Format of Set-up data packet   | 20 |

| 4.2 | VideoStreaming request fields  | 27 |

| 6.1 | Modified USB driver parameters | 46 |

# Listings

| 6.1 | USB H/W register access                | 39 |

|-----|----------------------------------------|----|

| 6.2 | Faulty iTD transaction offset setting  | 48 |

| 6.3 | R_MMU_VAtoPA() function declaration    | 48 |

| 6.4 | Correct iTD transaction offset setting | 49 |

# **Acronyms**

**API** Application Programming Interface.

CPU Central Processing Unit.

**CS** Control Selector.

**DMA** Direct Memory Access.

**EHCI** Enhanced Host Controller Interface.

**EMI** ElectroMagnetic Interference.

**FSM** Finite State Machine.

H/W Hardware.

**HCD** Host Control Driver.

**HCI** Host Controller Interface.

**HMD** Head-Mounted Display.

**iTD** Isochronous Transaction Descriptor.

JCU JPEG Codec Unit.

**LSI** Large Scale Integration.

MGR Host Manager.

MPS Maximum Packet Size.

OTG On-The-Go.

QH Queue Head.

qTD Queue element Transfer Descriptor.

RTOS Real-Time Operating System.

**SerDes** Serializer/Deserializer.

**TMDS** Transition Minimized Differential Signaling.

**USB** Universal Serial Bus.

**UVC** USB Video Class.

**VC** VideoControl.

**VDC** Video Display Controller.

**VS** VideoStreaming.

# Chapter 1

# Introduction

# 1.1 Get Your Way

#### 1.1.1 The Company

Get Your Way [1] is a young technology company founded in 2020 by 3 engineers from the university of Liège. Their main product is a lightweight Head-Mounted Display (HMD) called arDent Display. It started off as a graduation project, intended to be used to display route indications for cyclists. As the company matured, it specialized into providing solutions to the picking <sup>1</sup> issue, for the hospital and logistics sectors.

#### 1.1.2 arDent Display

The arDent Display, shown on figure 1.1, is composed of two parts which interlock, attached to a headband. The first part contains the screen and a microcontroller, whereas the other contains a battery, as well as the only cable receptacle: a USB-C port. This USB-C port currently has two uses: battery charge, and data transfer. Indeed, the device can be used as as mass storage peripheral when plugged to a PC, which allow convenient data transfer at a relatively high speed. It also contains a Bluetooth module, which allows transfers of small amounts of data without any cable.

The operator can not interact with the *arDent Display* directly: the only button serves to power on and off the device. However, interaction is possible using an intermediate device connected to it via Bluetooth. For instance, a phone or *Get Your Way*'s wrist-attached keypad: *ScanPad*.

The battery module is removable and two are provided with the device. This allows to charge one battery while the other is being used. A battery lasts 8 hours of operation

<sup>&</sup>lt;sup>1</sup>The retrieval of items from a storage.

Figure 1.1: arDent Display Source: [2]

# 1.2 Objective

Get Your Way wants to add the capability to display video on the arDent Display. The possible use-cases are for instance, to connect an endoscope in order to look in places which an operator can not reach or fit in, or take photos using the video stream display on the screen to aim. Since Bluetooth has a low data rate (up to 3Mb/s [3]), using the USB-C physical interface is preferable. However, Get Your Way does not possess in-house expertise about the USB standard as they have used contractors for USB-related features, such as the mass storage peripheral functionality. This is why this project was proposed as a master's thesis.

The project thus consists in implementing the reception of a video stream, and display of received video frames on the *arDent Display*.

# 1.3 Thesis Organization

The rest of this document is organized into different chapters, described successively in this section.

Chapter 2 contains a state of the art about video formats and physical interfaces related to video transfer. This analysis ignores the *arDent Display* hardware, in order to develop a broad summary of existing technologies. The intent is both to provide *Get Your Way* information to help them design a possible future version of *arDent Display*, and to extend personal knowledge.

The two following chapters, 3 and 4, provide in depth summaries about the USB 2.0 and USB Video Class (UVC) standards, detailing every concept needed to understand the drivers used by the video streaming application. Chapter 5 details the standardized interface between a USB hardware module and driver for USB 2.0, the EHCI.

Thereafter, the implementation process of the video streaming application is described in chapter 6. This implementation was performed on a development board, which allows easier debugging. Furthermore, sample applications designed for this board can conveniently be tested before porting them to the target device: the *arDent Display*.

The implementation process on the *arDent Display* is discussed in 7. This chapter details how to port the streaming project from the development board to the *arDent* board, and the hardware constraint that prevented it.

Chapter 8 contains the conclusion and next possible developments for this project. Finally, an annex about the internship at *Get Your Way*, and an analysis about their target markets, is located in chapter 9.

# Chapter 2

# State of the Art

# 2.1 Physical Interfaces

The goal of this section is to review the existing connectors for video transfer used by cameras, as well as the protocols used in combination.

#### 2.1.1 **DVI**

The Digital Visual Interface is a royalty-free legacy standard. Three types exist: DVI-A which carries an analog signal, DVI-D which carries a digital signal and DVI-I which can carry both [4]. DVI-A and I are backwards compatible with the VGA standard. Data is transmitted without packetization, using Transition Minimized Differential Signaling (TMDS) over twisted pairs, which ensures good ElectroMagnetic Interference (EMI) resistance. A dual link DVI-D cable can reach a bitrate of 7.92 Gb/s.

#### 2.1.2 HDMI

The High-Definition Multimedia Interface is a licensed proprietary interface managed by the HDMI Forum. HDMI started as an improved version of DVI, also using TMDS over twisted pairs, and is backwards compatible with it with the help of adapters. The latest version of the protocol (2.1b) ditches TMDS for Fixed Rate Link (FRL) and support a maximum bitrate of 48Gb/s [5], as sell as the recently added power supply feature. It usually transmits uncompressed video, but can also use the DSC scheme (see section 2.2.1).

#### 2.1.3 FireWire

Firewire is a licensed legacy serial full-duplex connector, standardized as IEEE 1394 [6]. Maximum bitrate is 3200Mb/s, and power can be transferred as well. Contrary to USB, it uses a peer-to-peer architecture. It can support the GenICam GenTL standard, making it plug and play [7].

#### 2.1.4 PCle

The Peripheral Component Interconnect Express (PCIe) is a dual-simplex serial bus designed to connect hardware devices inside of computers [8]. It uses a packetized protocol and differential

signaling to transfer data. The latest version of the x16 lanes cables, 6.0, can reach a bitrate of 256Gb/s [9]. PCle can be used over optic fiber for long range applications. It can support the GenlCam GenTL standard, making it plug and play [7]. It can be noted that the PCle standard requires PCl-SIG membership for commercial use.

#### 2.1.5 MIPI CSI

The Mobile Industry Processor Interface (MIPI) alliance manages different hardware interface standards targeted for mobile applications. The Camera Serial Interface (CSI) is an open licensed standard that notably defines a packetized video transfer protocol. It offers error recovery mechanisms, low power consumption and latency, and multiplexed virtual channels [10]. The use of Differential Pulse Code Modulation (DPCM) allows for lossless compression of data [11]. It is widely used for embedded vision applications. The CSI standard also describes a protocol for camera configuration, the Camera Control Interface (CCI), based on the I<sup>2</sup>C protocol. The MIPI Camera Command Set (CCS) [12] and the GenlCam GenTL [7] standards allow CSI cameras to be plug and play.

CSI-2 is the most widespread version used, although CSI-3 is more recent. 3 different MIPI physical layer interfaces can be used with CSI-2. Those connectors are smaller than USB, and can deliver data directly to the processor, ensuring low latency [13].

**D-PHY** A D-PHY lane uses differential signaling on two conductors to transmit data [14]. This allows good EMI resistance. Four lanes can be used at the same time, which combined with the two clock pins result in ten pins. D-PHY can reach a maximum of 36Gb/s with the 3.5 version [15]. D-PHY interfaces can switch between a high speed mode, using differential signaling, and a low power mode, using single ended signaling. The alternate power mode is used during the transition between the two previous modes. D-PHY was designed to carry data over short distances, up to 4 meters, but the closer the less errors and attenuation and thus the more bitrate.

**C-PHY** C-PHY is more recent than D-PHY. It uses one more wire per lane than D-PHY but the clock is embedded with the useful signal [14]. C-PHY can support 3 lanes of 3 wires at the same time and can reuse the same pins as D-PHY. It is thus fully backwards compatible. C-PHY is designed for the same cable lengths as D-PHY, but offer better EMI resistance and higher bitrate, i.e. 75Gb/s at maximum with the 3.0 version [15]. It also consumes less power.

**A-PHY** A-PHY was designed to carry data over longer distances, up to 15 meters. It uses an asymmetrical architecture over either a shielded differential pair, a coaxial cable or a Star Quad Cable (SQC) [16]. With a dual lane architecture over SQC, it can reach a maximum bitrate of 64Gb/s in the downlink and 1.6Gb/s in the uplink [15]. It also offers good EMI resistance, and can supply power.

#### 2.1.6 **DVP**

The Digital Video Port is a parallel interface, aimed at mobile applications like CSI-2. It is simpler to implement, cheaper and more widespread [17]. However, due to its parallel architecture it requires more pins, is more prone to EMI, consumes more power and has a lower bandwidth.

#### 2.1.7 SDI

The Serial Digital Interface is a physical layer standard managed by the SMPTE used to transfer uncompressed video [18]. It is generally used over a coaxial cable but can also be used over optical fiber, offering thus good EMI resistance and long cable length without signal attenuation. Furthermore, it is plug and play, offers low latency and error recovery [19]. However no power or control signals can be transmitted. The latest version, 24G-SDI, reaches a maximum bitrate of 24Gb/s.

#### 2.1.8 Camera Link

The Camera Link is an open, licensed standard maintained by the Automated Imaging Association (AIA). The interface is based on the Channel Link technology and thus also uses Low Voltage Differential Signaling (LVDS) over twin-axial cables [20]. LVDS allows goods EMI resistance and low power consumption. The latest version of the standard, Camera Link High Speed (CLHS), offers 25Gb/s maximum bitrate per cable, long length wires using copper twisted pairs or optical fiber, low latency and single-bit error recovery [21]. It supports the GenlCam GenTL standard, making it plug and play [22]. It can be noted that CL connectors are quite large.

#### 2.1.9 CoaXPress

CoaXPress (CXP) is an open, royalty-free standard managed by the Japan Industrial Imaging Association, developed as a successor to Camera Link. It uses a coaxial cable as an asymmetric serial link to transmit data and power [23]. Control messages can thus also be exchanged on the link. The maximum bitrate per cable is 12.5Gb/s in the downlink and 42 Mb/s in the uplink with the latest CXP 2.1 version. Cables can reach 100 meters in length but at a lower bitrate. CoaXPress can also be used over optical fiber. Latency is low and fixed, and the interface is hot-pluggable. It supports the GenlCam GenTL standard, making it plug and play [22].

#### 2.1.10 GMSL

The Gigabit Multimedia Serial Link (GMSL) is a proprietary standard that uses a coaxial cable for shielding from EMI, or a twisted pair for a lower cost alternative [24]. It uses a Serializer/Deserializer (SerDes) block: Data is serialized, transmitted over an asymmetric link then deserialized. GMSL 3 can transmit 12 Gb/s in the forward channel and 187 Mb/s in the reverse channel. GMSL is used to extend the range of other physical interfaces, such as HDMI, CSI-2, LVDS or eDP. Cables can reach 15 meters without significant signal fading.

#### 2.1.11 FPD Link

Flat Panel Display Link is an open, royalty-free standard. It uses differential signaling and a SerDes block to transmit data and power [25] over either a twisted pair, a coaxial cable or a starquad cable [26]. Cables can thus reach 15 meters without signal fading, and power consumption is low. Control signals can also be exchanged on the same link, using the I<sup>2</sup>C or SPI protocols. FPD Link is used to extend the range of other physical interfaces, such as HDMI, CSI-2 or LVDS. The latest version, FPD link IV, reaches a bitrate of 13Gb/s per cable.

#### **2.1.12** Ethernet

Ethernet cables use the Internet protocol suite to transfer data. Length can reach 100 meters and bitrate 40Gb/s for twisted pairs cables [27], while optical cables can reach several kilometers and 400 Gb/s [28]. Cables that comply to the Power over Ethernet (PoE) standard can transfer also power in addition of data. Ethernet can support the GenlCam GenTL standard, making it plug and play [7]. Multiple application layer protocols can be used for video streaming, such as: RTSP, RTMP, DASH, HLS, WebRTC [29]. However, in industrial settings, GigE vision is preferred.

**GigE** The Gigabit Ethernet standard is a licensed standard which mainly describes two application layers protocols: the GigE Vision Control Protocol (GVCP) and the GigE Vision Stream Protocol (GVSP) [30]. It was designed for uncompressed video transfer, but since version 2.0 the following compression formats are also supported: JPEG, JPEG 2000 and H.264 [31]. The latest version, GigE 2.2 supports a bitrate of 10Gb/s. It can be noted that the CPU usage is slightly higher with GigE interfaces than with FireWire, USB 3.0, CameraLink or CoaXPress [32]. GigE compliance implies GenICam GenTL support [22].

#### 2.1.13 Thunderbolt

Thunderbolt is a proprietary licensed standard. It defines a packetized protocol that combines DisplayPort signals for video transfer and PCle signals (see section 2.1.4) for data transfer on the same link [33]. It uses the mini DisplayPort connector, and either optical or electrical cables. With the former it can also carry power. It can reach a bitrate of 10Gb/s with version 1, and 20Gb/s with version 2.

Thunderbolt 3 and later versions use the USB-C connector, but are not used by cameras and will thus not be discussed.

#### 2.1.14 USB

The Universal Serial Bus (USB) is a standard managed by the USB Implementers Forum (USB-IF) which defines connectors for data and power transfer, as well as the protocols to use them. USB cables are either electrical, or optical for longer range and better EMI resistance.

#### 2.1.14.1 USB Protocols

Multiple USB standards exist, with different bitrates, but they are not available on every connector. USB protocols are more complex than others like CSI-2, but they make up for it with their widespread support and by being plug-and-play [34]. The original USB standard was created to provide a bidirectional, low cost, plug-and-play, low to mid speed bus. It was intended to be used to connect peripherals and phones to PCs. This explains why the first USB protocols implement a master-slave architecture.

**USB 2.0** The USB 2.0 protocol is a packetized half-duplex protocol. It uses a master-slaves architecture, named host and devices <sup>1</sup> in the standard [35]. The USB host initiates the communications

<sup>&</sup>lt;sup>1</sup>A device which provide a capability can also be called a function

by polling the device and supplies them with power. There can only be one in the system and the role is fixed.

The USB 2.0 protocol allows a maximum bitrate of 480Mbit/s, but it only reaches around 240-320Mbits/s because of hardware interface limitations and driver overheads [36].

**USB 3.0** USB 3.0 is the successor to USB 2.0. USB 3.0 cables have 5 additional wires than 2.0 ones, two twisted pairs and a ground wire, which form the SuperSpeed bus. It allows USB 3.0 to be dual simplex while also retaining the USB 2.0 channels, thus keeping backwards compatibility [37]. The USB 3.0 protocol is an improved version of the USB 2.0 protocol, with better flow control and error correction for instance. This allows USB 3.0 cables to reach higher bitrate, i.e. a maximum theoretical bitrate of 5Gb/s but an effective one of 3.2Gb/ [38], and a higher power supply. Furthermore, hosts do no need to poll before every data exchange, lowering the computational load. The connector can be differentiated from the 2.0 ones thanks to their blue color.

**USB 3.1** USB 3.1 is the successor to USB 3.0. It uses the same cable architecture, but the clock used on the bus is twice as fast and data encoding is more efficient [39]. This faster bus is named SuperSpeedplus. Bitrate is thus twice as high as USB 3.0, i.e. a maximum theoretical bitrate of 10Gb/s but an effective one of 7.2Gb/s [38].

USB 3.0 and 3.1 were renamed to USB 3.1 gen 1 and gen 2 afterwards.

**USB 3.2** USB 3.2 is the successor to USB 3.1. It uses two SuperSpeedplus buses, which results in double the bitrate compared to USB 3.1, i.e. a maximum theoretical bitrate of 20Gb/s but an effective one of 16Gb/s [38]. Contrary to the previous protocols, it is only available on USB-C. USB 3.0, 3.1 and 3.2 were renamed to USB 3.2 gen 1x1, gen 2x1 and gen 2x2 afterwards. SuperSpeed USB 5Gbps, SuperSpeed USB 10Gbps and SuperSpeed USB 20Gbps are also used as commercial names.

**USB4** USB4 2.0, or gen 4x2, is the latest version of the USB standard. It can reach a bitrate of 80Gb/s using the same dual lane architecture as USB 3.2 [40]. It is however not used yet by cameras and will thus not be discussed further.

#### 2.1.14.2 **USB Classes**

When a USB device gets connected to a host, it gives information about its capabilities in a process called configuration. One given attribute is the USB class of the device. USB classes are groups of devices that share common commands and descriptors [41]. The UVC and USB3 Vision classes in particular are widely used to connect cameras.

**USB Video Class** The UVC regroups devices that necessitate or perform video transfers [42]. Devices that implement the UVC standard can transfer video with the following video coding formats:

Uncompressed video

MPEG2-PS

MPEG1-SS

MPEG-2 TS

MPEG-4 SL

VP8

MJPEG

VC1

• H.264

DV

There is also the possibility to use vendor-defined formats, such as:

H.265

It can support the GenICam GenTL standard [7].

**USB3 Vision** Similarly to GigE, USB3 Vision is a licensed standard that is designed for industrial settings. It redefines some parts of the USB standard, such as device identification, control and how data is exchanged, i.e. via the USB3 Vision Streaming Protocol (UVSP) [43]. USB3 Vision implies GenICam GenTL compliance [22].

#### 2.1.14.3 USB Connectors

**USB-A** USB-A receptacles are only for hosts.

**USB-B** USB-B receptacles are only for devices.

**Micro USB** Micro USB-AB and micro USB-B receptacles can be used for both hosts and devices. They have one more pin than USB-A and USB-B receptacles, the ID pin [44]. It is used used to specify if a host or a device is connected.

Devices whose only USB receptacle is a Micro USB-AB one, and can be used both as host or device, are called On-The-Go (OTG) devices [45]. The host negotiation is done with the Host Negotiation Protocol (HNP) for USB 2.0, and the Role Swap Protocol (RSP) for USB 3.0. Some devices are not able to negotiate their role and instead rely on the plug used to determine it. These are called Dual Role Devices.

**USB-C** USB-C was designed to be smaller, more robust and easier to use than previous USB connectors. Indeed, it can be plugged upside-up and upside-down, and can be used for both hosts and devices. Host and devices are called Downstream Facing Port (DFP) and Upstream Facing Port (UFP) in the USB-C nomenclature, and the role of a port can be negotiated. The standard specifies that unshielded twisted pairs, shielded twisted pairs as well as coaxial and twin-axial wires can all be used inside a USB-C cable for the signal pairs. Simple wires are used for sideband signaling and power supply [46]. Different kinds of cables are defined in the standard:

- USB Full-Featured Type-C cables, i.e. USB-C cables that support USB 2.0, USB 3.2 and USB4 data operation as well as Power Delivery.

- USB 2.0 Type-C cables with a USB 2.0 Type-C plug at both ends

- Captive cables, i.e. cables that has one USB connector and is either permanently attached or has a non-USB connector. In this case the USB connector is either a USB Full-Featured Type-C plug or USB 2.0 Type-C plug.

• Active cables, i.e. cables with embedded signal conditioning circuits. They can be longer without signal fading.

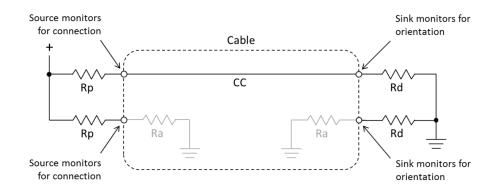

Power Delivery is a USB-C protocol that provides flexible power supply [47]. Contrary to previous USB power protocols, the power flow direction is negotiated and does not depend on the roles of the devices. Furthermore, the maximum power rate is higher. Power Delivery packets are sent on the Configuration Channel (CC). This channel can notably be used as a side-band channel, e.g. for discovery of cable capabilities, Data Role Swap (either DFP or UFP) and alternate modes negotiation.

Alternate modes, or alt modes, are protocols defined by standards or vendors, that utilize the reconfigurable pins of the USB-C cable to supersede the USB protocol. Popular alt modes include:

#### HDMI

See section 2.1.2

#### DisplayPort

Protocol designed for streaming video to a display.

#### MHL

Adaptation of HDMI targeted for mobile devices.

• Thunderbolt (3.0 onward)

See section 2.1.13

# 2.2 Video Compression Formats

The goal of this section is to review the existing video compression formats used by cameras.

Compression designates the suppression of information in some data, in order to lower its size. It can be lossless, if the discarded information was redundant, or lossy otherwise. In the case of video compression, four type of redundancy can be identified:

#### Spatial redundancy

In any non random array of pixels, e.g. a picture, pixels values are correlated with their neighbors.

#### • Temporal redundancy

In any non random series of array of pixels, e.g. a video, pixels values are correlated with values from neighboring arrays.

#### Entropy redundancy

In any non random signal, some code values appear more frequently than others and hold thus less information. Representing those frequent values by short codes will reduce the number of bits to transmit.

#### Perceptual redundancy

Some information is not visible to the human eye and is thus irrelevant in applications targeted for humans. For instance, high spatial resolution and high sampling rates are not discernible to the human eye, especially for the chrominance. Compression algorithms discarding this kind of information are said to be visually lossless.

#### 2.2.1 DSC

Display Stream Compression is a visually lossless compression scheme designed for real-time video streaming from a source to a display [48]. It is thus computationally light to ensure low latency. DSC can be notably used over the HDMI protocol.

#### 2.2.2 **MJPEG**

Motion JPEG (MJPEG) utilizes the JPEG scheme to separately compress each frame, without using temporal redundancy. It is thus computationally lighter and insensible to motion complexity, but less efficient at compression than algorithms that do use it [49]. Since frames are all intracoded, any frame can easily be extracted as a standalone image and errors in a frame do not affect others, which is useful in case of transmission errors. Thanks to the low compression, it reaches higher quality than other more efficient schemes. M-JPEG was never standardized, so multiple implementations coexist, such as the UVC one. Indeed, although frame compression uses the JPEG standard, organization of the stream of frames depends on the MJPEG implementation.

#### 2.2.3 MJPEG 2000

Similarly to MJPEG, MJPEG 2000 separately compress each frame but uses the JPEG 2000 scheme. This format thus offers slightly more compression than MJPEG but at the cost of more complexity [50]. It was standardized by the International Organization for Standardization (ISO).

#### 2.2.4 MPEG 4

The Moving Picture Experts Group (MPEG) is a working group that creates standards about coded representation of digital audio, video, 3D Graphics and genomic data [51]. The MPEG video coding formats are open, licensed standards.

Part 2 of the MPEG 4 standard covers video compression. MPEG 4 supports low bitrate applications, e.g. mobile units or streaming over the internet, as well as high bitrate high quality applications, e.g. playing a video from local storage [50].

The MPEG 4 standard supports multiple applications, using different sets of algorithms, known as profiles [52]. In order to simplify decoders, not all profiles have to be implemented. Furthermore, it is also allowed by the standard to only support a set of parameters values, known as levels. Profiles and levels are also present in other standards like H.264 or H.265.

#### 2.2.5 H.264

The part 10 of the MPEG 4 standard also covers video compression. It is better known as H.264, or Advanced Video Coding (AVC). It was designed to provide better compression for a fixed quality compared to existing formats, without increasing the complexity too much. For instance, H.264 compress 80% more than MJPEG, and 50% more than MPEG 4 part 2 [53]. It was also meant to be flexible and used for many applications such as Internet streaming, TV broadcast, storage on Blu-rays,... Indeed, it offers good error robustness to accommodate transmissions errors, a straightforward syntax to simplify implementations, and exact match decoding, i.e. it defines how calculations are made by the encoder and decoder in order to avoid accumulating errors. Furthermore, it can handle low and high bitrates, resolutions or latencies. It is widely supported nowadays.

#### 2.2.6 H.265

H.265, also known as High Efficiency Video Coding (HEVC), is the successor of the H.264 format, designed to offer more compression for similar quality. Indeed, it can reach 50% reductions in bitrate without quality loss compared to H.264 [49]. However, it is more complex and not as widely supported as H.264.

# 2.3 Case Study

This section contains a comparison of the different physical interfaces described in section 2.1, with the intent of finding the most relevant one for a possible new version of the *arDent Display*. The analysis is not done for the current *arDent* board since only one connector is present on it: a USB-C port.

#### 2.3.1 Scope Statement

Here follows a description of the needs of Get Your Way concerning the physical support used to connect the camera.

#### Limiting requirements:

- Reasonable computational load, to keep power consumption low

- Wide support by cameras, for ease-of-use by customers

- Plug and play, for ease-of-use by customers

- Power supply through cable, to allow light cameras without battery to be used

- Control through cable, to allow interactivity with the camera, e.g. to take a photo at a specific time

- Bandwidth sufficient for a stream of 854x640-pixel frames at 30 FPS

- Small connector receptacle, since the arDent Display is relatively small itself

- Royalty-free, to reduce expenditures

#### Non limiting requirements:

- Cable length up to 0.5m

- Low EMI resistance

These two non limiting requirements allow the use of electrical cables. Optical cables will thus not be considered as they are more expensive and consume more power [54].

# 2.3.2 Technology Comparison

As a first sorting, the following standards can be ditched:

- SerDes standards, as cable length and EMI resistance are non limiting requirements:

FPD Link, GMSL

- Licensed standards, to limit expenditures:

HDMI, PCIe, CSI, Camera Link, Thunderbolt

- Obsolete legacy standards: DVI, FireWire

- Parallel interfaces, as they are less energy efficient than serial interfaces:

DVP

4 standards remain: SDI, CoaXPress, Ethernet and USB. Table 2.1 compares them using relevant characteristics. USB2 and USB3 are both assumed to be used with a USB-C receptacle, Ethernet with a RJ45, SDI and CoaXPress with a micro-BNC.

|                       | 24G-SDI           | CoaXPress | Ethernet  | USB2      | USB3.2    |

|-----------------------|-------------------|-----------|-----------|-----------|-----------|

|                       |                   | 2.1       | Cat 8.2   |           |           |

| Maximum bitrate       | 24                | 12.5      | 40        | 0.48      | 20        |

| [Gb/s]                |                   |           |           |           |           |

| Computational         | low               | low       | medium to | medium    | low       |

| load [32]             |                   |           | low       |           |           |

| Plug and play         | yes               | yes       | yes       | yes       | yes       |

| Power through cable   | no                | yes       | yes       | yes       | yes       |

| Control through cable | no                | yes       | yes       | yes       | yes       |

| Receptacle size [mm]  | 7.48x7.48         | 7.48x7.48 | 16×13.24  | 8.34x3.26 | 8.34x3.26 |

| Compression           | none <sup>2</sup> | none      | possible  | possible  | possible  |

Table 2.1: Physical interfaces comparison.

# 2.3.3 Summary

SDI can not be used because of the lack of power supply and control through cable. Since Ethernet and USB2 have higher computational load than CoaXPress and USB3, they are less suited for embedded applications and should also be avoided. CoaXPress is targeted for industrial uses, and cameras are thus rare and expensive.

The USB-C connector is thus the most suited physical interface for this application. The protocol used in combination should be at least 3.0 to benefit from the low computational load, or a more recent version like 3.2.

<sup>&</sup>lt;sup>2</sup>JPEG support was added in 2024, but the intended and most widespread use of SDI is uncompressed video transmission [55]

# Chapter 3

# **USB 2.0 Standard**

This chapter describes the vocabulary and concepts from the USB 2.0 protocol [35] [56] that are necessary to understand the description of the USB Host Driver in section 6.4, with a focus on high-speed devices.

#### 3.1 General Architecture

As mentioned in section 2.1.14.1, the USB 2.0 protocol uses a master-slave architecture. The master is called a host, whereas slaves are called devices. Devices that provide a capability to the host are called functions. The host is expected to be implemented on a powerful device such as a computer, and most of the complexity of the USB protocol is thus managed by the host. For instance, it is the host that supplies power to the devices, and only hosts can initiate USB requests to connected devices. Indeed, devices can not send USB packets unprompted, they must first be polled. All this allows to simplify USB peripherals. USB hosts are supposed to support every USB class of devices (see section 3.2). Simpler hosts were later added to the USB specification: so-called targeted hosts, which only support only a specific set of classes. Some devices can either be used as host or function, and are called OTG devices.

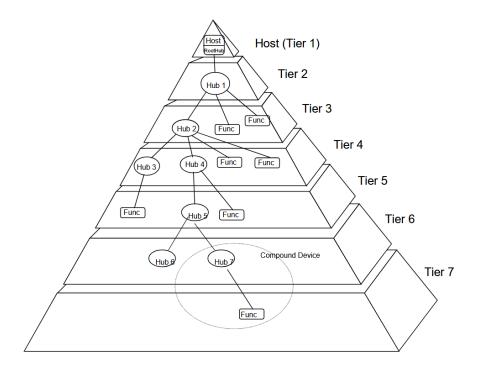

A USB system thus consists of one host and at least one device. The host initiates every transfer, and can target them to the right device by using their address, which the host assigns. Multiple devices can thus be in operation at the same time. Hubs are special USB devices that allow to use one USB port to connect multiple devices, including other hubs potentially. A USB system is thus a logical tree with the host at the root and devices at the leaves, with hubs in between. Figure 3.1 represents the bus tiered star topology. Only 7 tiers are allowed, and only 5 non-root hubs can be chained, in order to keep hub and propagation delays reasonable. A compound device is represented on the diagram: it is a device that contains an embedded hub.

A USB host is made up of two components. The first is the host controller, implemented both through software and hardware. It implements the following features:

- Detection of device attachment and removal

- Management of data and control flows between the host and devices

- Management of power supplied to the devices

- Management of bus activity

Figure 3.1: USB bus topology Source: [56]

The second component is the root hub. It is a USB hub embedded in the host that connects the host controller to every USB port of the device. The root hub is handled by the hub class driver like any other hub, but the interface between this hub and the host controller depends on the hardware implementation. Indeed, USB transactions may not be necessary to exchange data between the controller and the root hub, given the close integration possible between the two.

### 3.2 USB Devices

USB devices are classified into groups that share common commands and descriptors, called classes. They are supported by specific class drivers. Many classes are defined by the USB standards and custom ones are also allowed. A descriptor is a data structure that contains information about the device capabilities. Descriptors are either part of the USB 2.0 standard itself, standardized in class-specific standards or vendor-defined. Each descriptor contains at least a length field for parsing purposes and a descriptor type field. Values stored on multiple bytes use the little endian encoding scheme.

The main descriptor is the device descriptor: it is a unique and contains information about the device itself, such as the implemented USB specification number, product ID, USB class and subclass <sup>1</sup>, indexes to strings describing the device, and numbers of configurations.

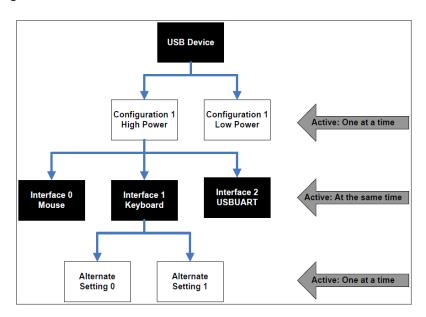

Configuration defines which interfaces can be used and what is the power source of the device: self powered or bus powered, as well as the max drawable current. Only one configuration can be enabled at a time.

<sup>&</sup>lt;sup>1</sup>Classes and subclasses can also be defined separately for each interface

Interfaces are the layer below configurations: they represent a particular function implemented by the device. Interface descriptors contain USB class and subclass fields, and serve as anchor for endpoint descriptors as well as class-specific descriptors. Devices with interfaces that implement different functions are called composite devices. The host can switch interface during device operation in order to access other functions. For instance, a camera with a microphone which possess a video and an audio interface. An interface may also have alternate settings, i.e. interfaces with the same interface number but with different endpoints descriptors. As only one alternate setting can be active at a time, the same endpoint numbers can be reused.

Figure 3.2 is a diagram that describes a composite device with multiple configurations, interfaces, and alternate settings.

Figure 3.2: USB device configuration Source: [35]

# 3.3 USB Communications

# 3.3.1 **Pipes**

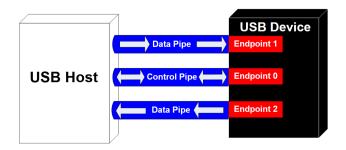

USB communications between the host and a given device are done through a pipe. A pipe is a connection pathway between the host controller and a specific addressable buffer of a device, called an endpoint. An endpoint is either used to transfer data to the host (IN type) or to transfer data the device (OUT type). Multiple pipes to the same device can be set, as long as they use a different endpoint, as depicted on figure 3.3. In this example, 3 pipes are set: the default control pipe, a IN data pipe and a OUT data pipe. The default control pipe is a special bi-directional pipe which always uses endpoint 0. It exists on every USB device as long as they are powered, and is used to access device configuration, status and control information.

They are two types of pipes: message and stream pipes. The data exchanged with a message pipe transaction follows a packet structure defined by the USB 2.0 standard, while no structure is

Figure 3.3: USB pipe model Source: [35]

imposed for stream pipes. The only message pipes are the control pipes, described in section 3.3.3.1. As mentioned earlier, a pipe is defined by 2 variables: a device address and an endpoint number. However, it is not enough information to execute a transfer, and the host has to store additional pipe-related data, such as: bus access frequency, transfer type, direction and the Maximum Packet Size (MPS), i.e the maximum transaction length. Pipes other than the default control pipe are set during the configuration process, described in section 3.4.3.

#### 3.3.2 Transfers

USB transfers are defined by the USB specification as follows: "one or more bus transactions to move information between a software client and and its function". There are multiple types of transfers defined in the specification, described in the following sections. They can be separated into two categories: periodic transfers, which offer bandwidth and latency guarantees, and asynchronous transfers, which implement a best effort model. Isochronous and interrupt transfers are periodic, whereas bulk and control transfers are asynchronous. All transfers except isochronous ones implement a transaction retry mechanism upon error detection.

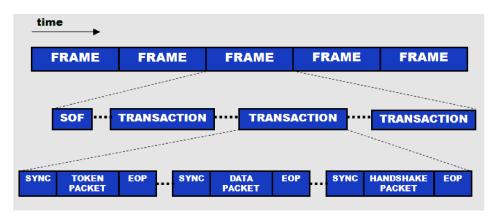

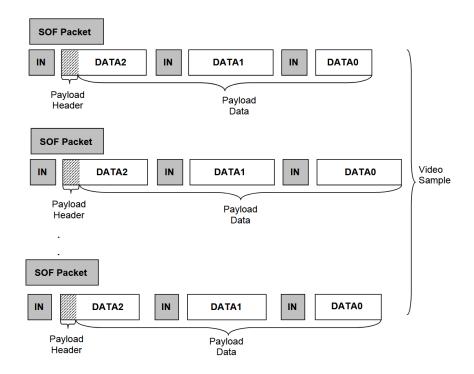

In order to implement the periodic transfers, the USB specification defines a 1ms time base called a frame, and a  $125\mu s$  time base called microframe. Frames are the base used by low- and full-speed devices, whereas the microframe is used by high-speed devices. Each transfer type describes what transactions and how many can be executed during a (micro) frame  $^2$ . Transfers denoted as periodic are given an opportunity to be executed every N number of (micro) frames, with N the polling period, which is endpoint-dependent.

Figure 3.4 describes the USB communication protocol from a time perspective. Each (micro) frame starts with a Start Of Frame (SOF) transaction, to mark the beginning of a (micro) frame, and synchronize host and device clocks. Multiple transactions are then executed, up to 3. Transactions are done by sending 3 packets: a token packet containing the address, endpoint number and direction, a data packet containing the data requested by the host, and a handshake packet <sup>3</sup> to acknowledge the transaction.

The handshake packet can also be used by a device to communicate a STALL condition to the host. Two situations warrant this:

• Functional STALL: the function is unable to transmit or receive data over a specific pipe. The

<sup>&</sup>lt;sup>2</sup>(micro) frame means frame or microframe, according to the USB speed.

<sup>&</sup>lt;sup>3</sup>Except for isochronous transactions

host has to explicitly clear this STALL. The host can never return a STALL during handshake but can set a halt bit on a device endpoint, which triggers a STALL on that endpoint. This commanded STALL can be used for instance if the host wants to stop receiving data from an IN endpoint temporarily.

Protocol STALL: the function is unable to complete the requested control transfer, for instance because the data content of the transfer is invalid. This STALL is automatically cleared upon the next control transfer.

A control pipe may support functional STALLs, but this is not recommended by the standard. The standard also states that devices do not need to return STALL for class-specific and vendor-specific requests.

The USB protocol, detailing the execution of bus transactions, will not be described any further as it is implemented by the USB host hardware module, whereas it is the controller software component that is of interest here.

Figure 3.4: USB communications Source: [35]

### 3.3.3 Asynchronous Transfers

#### 3.3.3.1 Control transfers

Control transfers are used to send commands, configure the device and obtain status information. Some commands are supported by all USB devices, while others are only implemented by specific classes. Control transfers are done using a control pipe, which is a message pipe. They have priority over bulk transfers. As mentioned earlier, the default control pipe is always present, so that the device can be configured with it. The standard also allows a device to provide other control endpoints in addition to endpoint 0, in order to set up other control pipes.

A control transfer consists of 3 steps. First, the host performs a set-up transaction to specify the request. Afterwards, data transactions are performed in the direction specified during the set-up transaction. Finally, the device returns status information to the host by performing a status transaction.

The different fields of the set-up transaction packet are specified by the standard, but the interpretation of the values they hold is class-dependent. Table 3.1 details those fields. The data packet content depends entirely on the USB class.

| Offset | Field         | Size (B)             | Value           | Description                                             |  |  |  |  |

|--------|---------------|----------------------|-----------------|---------------------------------------------------------|--|--|--|--|

| 0      | bmRequestType | <b>Type</b> 1 Bitmap |                 | Characteristics of request:                             |  |  |  |  |

|        |               |                      |                 | D7 - Data transfer direction:                           |  |  |  |  |

|        |               |                      |                 | 0 = Host-to-Device                                      |  |  |  |  |

|        |               |                      |                 | 1 = Device-to-Host                                      |  |  |  |  |

|        |               |                      |                 | D65 - Type:                                             |  |  |  |  |

|        |               |                      |                 | 0 = Standard                                            |  |  |  |  |

|        |               |                      |                 | 1 = Class                                               |  |  |  |  |

|        |               |                      |                 | 2 = Vendor                                              |  |  |  |  |

|        |               |                      |                 | 3 = Reserved                                            |  |  |  |  |

|        |               |                      |                 | D40 - Recipient:                                        |  |  |  |  |

|        |               |                      |                 | 0 = Device                                              |  |  |  |  |

|        |               |                      |                 | 1 = Interface                                           |  |  |  |  |

|        |               |                      |                 | 2 = Endpoint                                            |  |  |  |  |

|        |               |                      |                 | 3 = Other                                               |  |  |  |  |

|        |               |                      |                 | 431 = Reserved                                          |  |  |  |  |

| 1      | bRequest      | 1                    | Value           | Specific request                                        |  |  |  |  |

| 2      | wValue        | 2                    | Value           | Word-sized field that varies according to request       |  |  |  |  |

| 4      | wIndex        | 2                    | Index or Offset | Word-sized field that varies according to request; typ- |  |  |  |  |

|        |               |                      |                 | ically used to pass an index or offset                  |  |  |  |  |

| 6      | wLength       | 2                    | Count           | Number of bytes to transfer if there is a data stage    |  |  |  |  |

Table 3.1: Format of Set-up data packet Source: [56]

#### 3.3.3.2 Bulk transfers

Bulk transfers are used to transfer large amounts of data. They utilize all available bandwidth but do not offer any guarantee on speed or latency. The highest MPS allowed is 512 bytes. Although the theoretical maximal USB 2.0 bandwidth is announced to be 60MB/s, the specification actually mentions that is not reachable. Indeed, the bus frequency and microframe timing limit the number of successful bulk transactions within one microframe,  $N_{t/\mu f}$ , to 13. The maximum amount of periodic data  $D_{\mu f}$  transferable during one microframe is thus:

$$max(D_{\mu f}) = max(N_{t/\mu f}) * max(MPS))$$

(3.1)

$$= 13 * 512 = 6656B/\mu frame \tag{3.2}$$

The maximal bulk bandwidth  $B_B$  is thus :

$$max(B_B) = N_{\mu f/s} * max(D_{\mu f})$$

(3.3)

$$= 8000 * 6656 = 53.248MB/s \tag{3.4}$$

With  $N_{\mu f/s}$  the number of micro-frames in a second.

#### 3.3.4 Periodic Transfers

Periodic transfers provide a bounded latency and can reserve bandwidth. The entire bandwidth can not be reserved however: with a high-speed device for instance, 80% of a microframe can be used for periodic transfers at most. This allows to save some bandwidths for asynchronous transfers.

The USB 2.0 specification states that for a high-speed device, the MPS is limited to 1024 bytes and the number of transactions per micro-frame  $N_{t/\mu f}$  is limited to 3. The maximum amount of periodic data transferable during one microframe  $D_{\mu f}$  is thus:

$$max(D_{\mu f}) = max(N_{t/\mu f}) * max(MPS)$$

(3.5)

$$= 3 * 1024 = 3072B/\mu frame$$

(3.6)

The maximum amount of data that can be transferred during an entire frame is thus:

$$max(D_f) = N_{\mu f/f} * max(D_{\mu f})$$

(3.7)

$$= 8 * 3072 = 24576B/frame$$

(3.8)

With  $N_{\mu f/f}$  the number of micro-frames within one frame . Since a frame is equal to 1ms, the maximum bandwidth reservable for periodic transfers  $B_p$  is :

$$max(B_p) = max(D_f) = 24576B/ms$$

(3.9)

$$= 24.576MB/s (3.10)$$

#### 3.3.4.1 Isochronous transfers

Isochronous transfers require a guaranteed latency and share of the USB bandwidth. They use stream pipes, i.e. the content structure of the transactions depend on the USB class used. The host is allowed by the specification to poll at a higher rate than the one advertised, and devices must be able to handle it. In the case where data is no yet ready to be written into the IN endpoint, the device has to send a 0-length packet.

#### 3.3.4.2 Interrupt transfers

Interrupt transfers offer both reliable delivery of data and bounded latency. They are used when small amounts of data have to be transferred infrequently. Contrary to what the name might suggest, the host has to poll the device at a defined frequency, and the device has to acknowledge all transactions until it has data to send. Reception of said data by the host concludes the interrupt transfer.

#### 3.4 Device Attachment

This section contains a simplified description of how a device gets configured for use upon attachment. There are 3 main processes: first the device gets detected during dynamic detection. Then is it given an address during enumeration. Finally, the host learns about the device capabilities and configures the device during configuration.

# 3.4.1 Dynamic detection

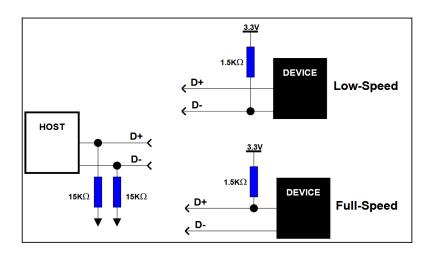

As described earlier, a USB device can only be connected through a hub, which can either be the root hub or a hub device. Upon attachment, the device raises the voltage of one of the D lines of the port, depending on the device USB speed. As can be seen on figure 3.5, it is done using pull-up

resistors. Depending on the D line used, the hub can learn if the device supports low- or full-speed. High-speed support can not be inferred at this stage. The device can only draw 100mA from the bus for the time being.

Figure 3.5: USB device detection Source: [35]

#### 3.4.2 Enumeration

The host has to query the hub in order to learn about the attachment, and the device speed. It uses an interrupt pipe for that purpose. The host then has to send a reset the device, by commanding the hub to do so. During this reset, a high-speed device can use the D lines to send a specific binary sequence which inform the hub about its high-speed support. Once the device has left the reset state, it can now respond to control requests. The default control pipe associated with this device always uses address 0, which is reserved for devices undergoing enumeration. This implies that only one device can be enumerated at a time.

The host then sends a GET\_DESCRIPTOR request to the device, to obtain the device descriptor. Only the eighth byte, containing the MPS of endpoint 0, is of interest. Devices are thus allowed to only send the first eight descriptor bytes. A device reset is executed again, so that the second GET\_DESCRIPTOR does not perturb the device. Finally, the hosts sets an address for the device. All following communications now utilize the new address, until the device is detached, reset, or the host reboots.

# 3.4.3 Configuration

The host begins by asking for the configuration descriptor. It uses this descriptor to learn about the device capabilities, in order to choose the correct driver to manage the device. Finally, the host issues a SET\_CONFIGURATION request. From that point on, configuration is over and the device can draw the maximal agreed power from the bus. The device can now also respond to class-specific requests, which likely involves other configuration commands before it can be used.

# **Chapter 4**

# **UVC Standard**

As mentioned in section 2.1.14.2, the USB Video Class (UVC) is a USB class which implements video-related functionalities, such as remote control of camera and video streaming over USB. This section describes the UVC standard concepts needed to understand the UVC driver implementation in section 6.8. The focus is thus on a USB host which receives a video stream through.

Every UVC version is backwards compatible: either the host or the peripheral can implement an outdated version and still remain compatible. Version 1.0 is thus sufficient to implement basic video streaming while still being supported by a wide array of devices, which is why it is the version described in this section. As the 1.0 specification is no longer available online, version 1.1 was used as source [57]. The revision history details the changes made by version 1.1, which only consists of optional functionalities and a few clarifications.

# 4.1 UVC Operational Architecture

Video functions are implemented at the interface level, via two UVC-specific interface subclasses. A UVC device contains one VideoControl (VC) interface and may contain multiple VideoStreaming (VS) interfaces. Different settings, stored in logical objects named controls, can be modified by the host. Controls belong to different addressable entities, i.e.: either a terminal, unit, interface or endpoint. It can be noted that the term entity just designates terminals and units however.

#### 4.1.1 VideoControl interface

The VC interface is used to configure the video device itself, e.g. the camera. VC controls are located inside units and terminals and can be used to modify the zoom or focus for instance. The VC interface is thus unique, and no alternate setting can be defined. It contains two endpoints:

- A control endpoint, implemented using the default endpoint (number 0). It is used to access controls of units and terminals. It is also used to access statuses of the video function.

- An optional interrupt endpoint, used to return status information about any addressable entity of the entire video function (VC and VS interfaces). It is located in this interface because it is always present, whereas the VS interface is optional.

Controls of this interface are initialized with default values. This implies that streaming is possible without modifying them.

#### 4.1.2 VideoStreaming interface

VS interfaces are used to configure and execute transfers of video data into or out of the function. VS controls can be used to modify the video format or frame dimensions for instance. Multiple VS interfaces might be exposed to allow concurrent video streams with different characteristics. The use of interface alternate settings allow to change the capabilities of a given endpoint, such as the bus access period or the MPS. The endpoint and alternate choice is done during the negotiation described in section 4.4. The specification also allows to provide no VS interface, which is useful in the case where the peripheral camera is just remotely controlled via USB but does not stream any video data for instance.

A given VS interface can only contain one bulk or isochronous endpoint for video transfer, and one optional bulk endpoint for still image transfer. The associated endpoints may either use IN or OUT as direction, depending on whether the device transmits or receives the video stream.

Some parameters of this interface have to be negotiated between the host and the device in order to set up the video stream. This negotiation is detailled in section 4.4. It is only after this negotiation that a VS interface can be chosen, and the related endpoint initialized.

# 4.2 UVC Descriptors

As described in section 3.2, a device can have multiple interfaces in the same configuration, which could potentially belong to different independent video functions if it is a composite device. Interfaces that belong to the same video function are regrouped into a video interface collection, described in an interface association descriptor. Subclass-specific descriptors are then used to store additional information about those interfaces, such as the supported video formats.

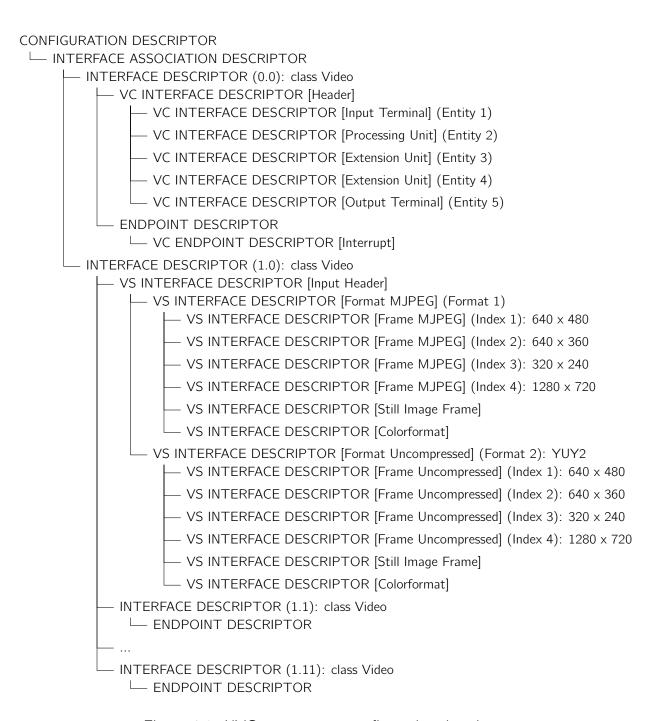

Figure 4.1 is a tree structure describing the device descriptor of the UVC camera used in chapter 6. Child nodes contain additional information about their parent node. This structure can be deferred from the configuration descriptor sent during the configuration process (see section 3.4.3): descriptors are sent from top to bottom, whereas dependencies between descriptors are described in the specification. For instance, when an interface descriptor is found during parsing of the device descriptor, it implies that every following descriptors are related to it, until another interface descriptor is found.

Figure 4.1: UVC test camera configuration descriptor

# 4.3 UVC-Specific Requests

The UVC standard specifies class-specific requests using the control transfers described in section 3.3.3.1. These UVC control transfers make use of the protocol STALL mechanism described in section 3.3.2 in the following cases: unsupported command, invalid target entity, unexpected data length, or invalid data content. The host can learn about the STALL cause by requesting the value of the VC Request Error Code Control for VC requests.

Since control transfers are used, set-up packets must follow the structure defined in table 3.1. The *bmRequestType* and *wLength* have the same meaning as defined in the table. The interpretation of *wValue* depends on the targeted entity. There are two types of UVC-specific requests, which use different values of *bRequest*. They are described in the following sections. *wIndex* is used to target an addressable entity, which depends on the control that is accessed and the *bRequest* type. An entity (unit or terminal) can be stored in the high byte and an endpoint or interface can be stored in the low byte.

### 4.3.1 Set request

Requests with *bRequest* set to SET\_CUR are used to set an attribute of a specific entity of the video function. For most entities, *wValue* stores the Control Selector (CS) field, which is used to select a specific control in an entity which own several. If the entity only has one control, it can be used to store other data instead. The actual value to set in the control is stored in the data stage of the transfer.

## 4.3.2 Get request

Multiple requests which are used to retrieve attribute values from specific entities are defined, each using a different *bRequest*. These allow to specify which attribute of a control parameter to request.

- Current setting attribute (GET CUR)

- Minimum setting attribute (GET MIN)

- Maximum setting attribute (GET MAX)

- Default setting attribute (GET DEF)

- Resolution attribute (GET RES)

- Data length attribute (GET LEN)

Additionally, information about the control can be obtained using GET INFO as bRequest.

# 4.3.3 Summary of VideoStreaming requests

As mentioned in section 4.1, some VS controls have to be modified in order to set up a stream, while VC controls all have default values. It is thus relevant to summarize the VS different requests in a table.

Table 4.1 details the possible requests to the VS interface. The Control Selector (CS) and the interface numbers must be stored in the high byte.

| bmRequestType | bRequest | wValue | wIndex    | wLength                   | Data            |

|---------------|----------|--------|-----------|---------------------------|-----------------|

| 00100001      | SET_CUR  | CS     | Interface | Length of parameter block | Parameter block |

| 10100001      | GET_CUR  |        |           |                           |                 |

|               | GET_MIN  |        |           |                           |                 |

|               | GET_MAX  |        |           |                           |                 |

|               | GET_RES  |        |           |                           |                 |

|               | GET_DEF  |        |           |                           |                 |

|               | GET_LEN  |        |           |                           |                 |

|               | GET_INFO |        |           |                           |                 |

Table 4.1: VideoStreaming request fields Source: [56]

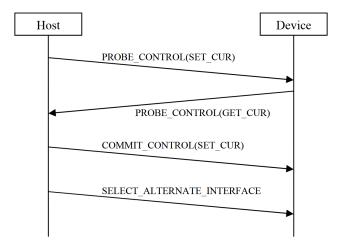

# 4.4 VS Parameter Negotiation

Contrary to VC parameters, it is not sensible to set default values for some VS parameters related to the video stream format and encoder. These particular parameters include the format, frame size and frame rate of the stream. Key frame rate and compression factor are also included, if relevant to the video format used. A stream can not be started before the host and the device negotiate the values of those special parameters.

Theses negotiable parameters are handled via the Video Probe and Video Commit controls. The Probe control is used for the negotiation itself, whereas as the Commit Control is used to set the parameters to the values previously negotiated. Table 4.2 summarizes the Probe and Commit controls parameters that are relevant to establish a basic video stream with a frame-based format (e.g. MJPEG or uncompressed formats). The offset field is relative to the control data structure, which is the data payload used in GET\_CUR and SET\_CUR requests. It is 26-byte long is UVC 1.0. Later versions of the UVC standard added fields to these controls, but they are optional to maintain backward compatibility.

| Offset | Field                    | Size (B) | Value  | Description                                                                                                                                                                                                                         |

|--------|--------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bmHint                   | 2        | Bitmap | Hint bitmap, used by the host to inform the VS interface about which fields shall remain constant during parameter negotiation. The only relevant hint for frame-based formats is <b>dwFrameInterval</b> , stored in the first bit. |

| 2      | bFormatIndex             | 1        | Number | Video format index, corresponding to the order of the VS format descriptors.                                                                                                                                                        |

| 3      | bFrameIndex              | 1        | Number | Video frame index, corresponding to the order of the VS frame descriptors of the chosen format.                                                                                                                                     |

| 4      | dwFrameInterval          | 4        | Number | Frame interval in 100 ns units. The value must be in the range defined in the frame descriptor.                                                                                                                                     |

| 18     | dwMaxVideoFrameSize      | 4        | Number | Maximum video frame size in bytes. Relevant if compression is used.                                                                                                                                                                 |

| 22     | dwMaxPayloadTransferSize | 4        | Number | Maximum number of bytes that the device can transmit or receive in a single payload transfer.                                                                                                                                       |

Table 4.2: Relevant VS Probe and Commit controls fields for frame-based formats

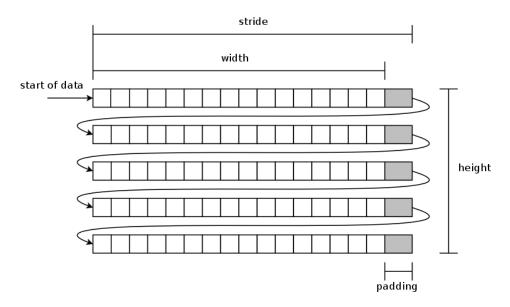

The endpoint direction determines which parameters are negotiable and which are fixed by either the host or the device. For a IN endpoint, the device proposes values for all but 3 parameters: **bmHint**, **bFormatIndex** and **bFrameIndex**, which must be proposed by the host. Some of the parameters are not modifiable by the host.