https://lib.uliege.be

https://matheo.uliege.be

# Master thesis and internship[BR]- Master's thesis: Design and Implementation of a Low-Cost Multi-channel Coherent Software Defined Radio Receiver for Educational and Amateur Radio Use[BR]- Integration internship

Auteur: Rouma, Alexandre

**Promoteur(s)**: Redouté, Jean-Michel **Faculté**: Faculté des Sciences appliquées

Diplôme : Master en ingénieur civil en aérospatiale, à finalité spécialisée en "aerospace engineering"

Année académique: 2024-2025

URI/URL: http://hdl.handle.net/2268.2/23363

#### Avertissement à l'attention des usagers :

Tous les documents placés en accès ouvert sur le site le site MatheO sont protégés par le droit d'auteur. Conformément aux principes énoncés par la "Budapest Open Access Initiative" (BOAI, 2002), l'utilisateur du site peut lire, télécharger, copier, transmettre, imprimer, chercher ou faire un lien vers le texte intégral de ces documents, les disséquer pour les indexer, s'en servir de données pour un logiciel, ou s'en servir à toute autre fin légale (ou prévue par la réglementation relative au droit d'auteur). Toute utilisation du document à des fins commerciales est strictement interdite.

Par ailleurs, l'utilisateur s'engage à respecter les droits moraux de l'auteur, principalement le droit à l'intégrité de l'oeuvre et le droit de paternité et ce dans toute utilisation que l'utilisateur entreprend. Ainsi, à titre d'exemple, lorsqu'il reproduira un document par extrait ou dans son intégralité, l'utilisateur citera de manière complète les sources telles que mentionnées ci-dessus. Toute utilisation non explicitement autorisée ci-avant (telle que par exemple, la modification du document ou son résumé) nécessite l'autorisation préalable et expresse des auteurs ou de leurs ayants droit.

# Design and Implementation of a Low-Cost Multi-channel Coherent Software Defined Radio Receiver for Educational and Amateur Radio Use

#### **ALEXANDRE ROUMA**

# UNIVERSITY OF LIÈGE SCHOOL OF ENGINEERING AND COMPUTER SCIENCE

MASTER'S THESIS COMPLETED IN ORDER TO OBTAIN THE DEGREE OF:

MASTER OF SCIENCE IN AEROSPACE ENGINEERING

Abstract: Current coherent software defined radio receivers, although on a path towards affordability for amateur radio and educational use, still have major down sides such as low bandwidth, hard to calibrate architectures, low channel count or high prices. Reviewing the state of the art in the field reveals that reusing mass produced commodity hardware by working around its intrinsic limitations is a viable path towards an affordable, high channel count, medium bandwidth coherent receiver. This masters thesis investigates the design of such a receiver using tuner ICs originally meant for low cost digital television receivers and a recently released high channel count ADC. Due to each tuner having its own local oscillator and phase locked loop, an onboard phase reference is added with the option of switching it into the receive path for auto-calibration. Before the full receiver is assembled, various subsystems are tested in advance to make sure they will perform adequately. The results shows that the phase reference splitter required for auto-calibration is able to maintain under 1% phase difference between its outputs over the entire frequency range of the receiver. It is also demonstrated that the power supply has the required accuracy and low ripple noise. Some mistakes were found in the design such as an incorrect capacitor in the power supply, an incorrect resistors in the tuner supporting circuitry and incorrect supply sequencing for the clock generator but all issues were easily resolved. Single channel reception was demonstrated showing that each channel on its own is a capable receiver with good sensitivity. Due to time constraints, mutli-channel coherent reception has not yet been demonstrated, but the currently obtained results do not indicate anything that would preclude the full system from working as intented.

THESIS SUPERVISOR: PR. JEAN-MICHEL REDOUTÉ

ACADEMIC YEAR 2024 - 2025

# Contents

| 1            | Introduction |                                                      |  |  |

|--------------|--------------|------------------------------------------------------|--|--|

|              | 1.1          | Goals                                                |  |  |

| 2 Background |              |                                                      |  |  |

|              | 2.1          | LimeSDR                                              |  |  |

|              | 2.2          | AMD RFSoC                                            |  |  |

|              | 2.3          | USRP x310                                            |  |  |

|              | 2.4          | KrakenSDR                                            |  |  |

|              | 2.5          | Comparison and Conclusions                           |  |  |

|              |              |                                                      |  |  |

| 3            |              | dware 1                                              |  |  |

|              | 3.1          | Frontend                                             |  |  |

|              |              | 3.1.1 Input Selection                                |  |  |

|              |              | 3.1.2 Tuner                                          |  |  |

|              | 3.2          | Clocks                                               |  |  |

|              |              | 3.2.1 Generation                                     |  |  |

|              |              | 3.2.2 Distribution                                   |  |  |

|              | 3.3          | Phase Reference                                      |  |  |

|              |              | 3.3.1 Generation                                     |  |  |

|              |              | 3.3.2 Distribution                                   |  |  |

|              | 3.4          | ADC                                                  |  |  |

|              | J.T          | 3.4.1 Anti-Aliasing Filter Design                    |  |  |

|              |              |                                                      |  |  |

|              |              | 1                                                    |  |  |

|              | 2 -          | 3.4.3 Power Conditioning                             |  |  |

|              | 3.5          | FPGA 3                                               |  |  |

|              |              | 3.5.1 Configuration Memory                           |  |  |

|              |              | 3.5.2 JTAG Programming and Debugging Port            |  |  |

|              |              | 3.5.3 The FPGA itself and 1PPS input                 |  |  |

|              | 3.6          | USB Interface                                        |  |  |

|              |              | 3.6.1 USB FIFO                                       |  |  |

|              |              | 3.6.2 USB Type C circuity                            |  |  |

|              | 3.7          | Power Supply                                         |  |  |

|              |              | 3.7.1 Power Requirements                             |  |  |

|              |              | 3.7.2 Power Regulation                               |  |  |

|              |              | 3.7.3 USB Type-C Power Delivery                      |  |  |

|              | 2.0          |                                                      |  |  |

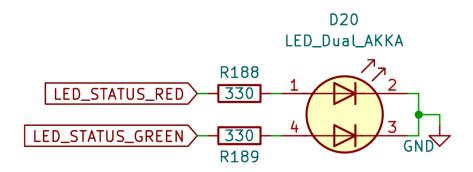

|              | 3.8          | LED Indicators                                       |  |  |

|              |              | 3.8.1 Frontend State                                 |  |  |

|              |              | 3.8.2 Power Supply State                             |  |  |

|              |              | 3.8.3 10MHz Reference Input State                    |  |  |

| 4            | Firn         | nware 4                                              |  |  |

|              | 4.1          | Logic Design                                         |  |  |

|              |              | 4.1.1 Soft Core                                      |  |  |

|              |              | 4.1.2 Memory Mapper                                  |  |  |

|              |              | 4.1.3 Double-Data-Rate to Single-Data-Rate Converter |  |  |

|              |              | · · · · · · · · · · · · · · · · · · ·                |  |  |

|              |              | 4.1.4 Deinterleaver                                  |  |  |

|              |              | 4.1.5 Sample Frame Packer                            |  |  |

|              |              | 4.1.6 USB FIFO Controller                            |  |  |

|              | 4.2          | CPU Code                                             |  |  |

|              |              | 4.2.1 Initialization                                 |  |  |

|              |              | 4.2.2 Command Loop                                   |  |  |

| _            | TT -         |                                                      |  |  |

| 5            | Host         | t Software 5                                         |  |  |

| 6 | Test  | ing     |                    | 57         |

|---|-------|---------|--------------------|------------|

|   | 6.1   | Clock   | Generator          | 57         |

|   |       | 6.1.1   | Methodology        | 57         |

|   |       | 6.1.2   | Issues             | 57         |

|   | 6.2   | Phase   | Reference Splitter | 59         |

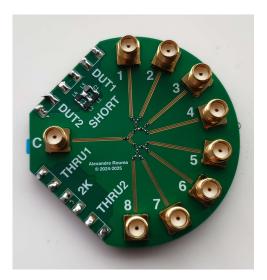

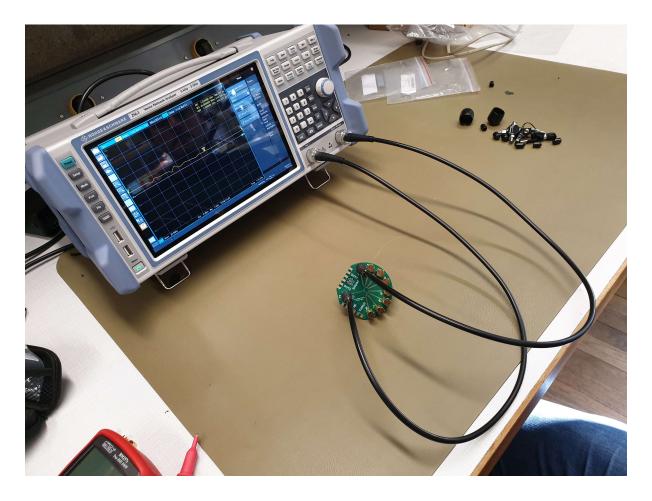

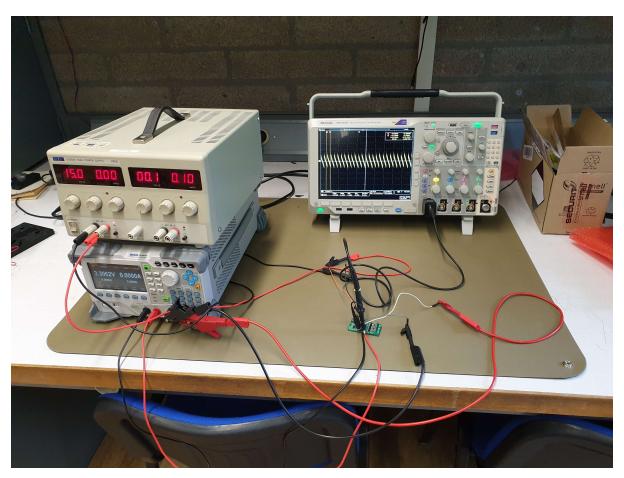

|   |       | 6.2.1   | Prototype          | 59         |

|   |       | 6.2.2   | Methodology        | 60         |

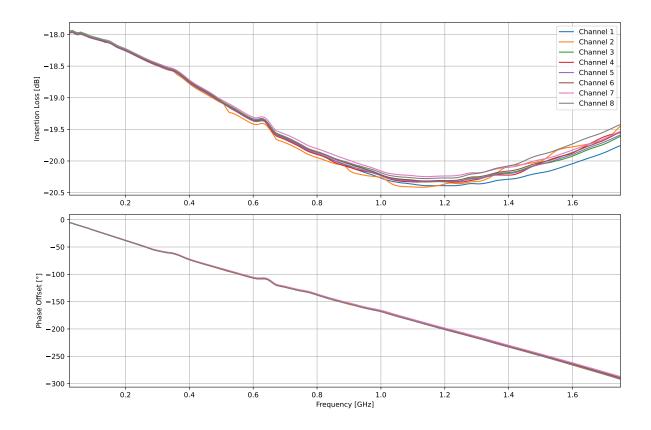

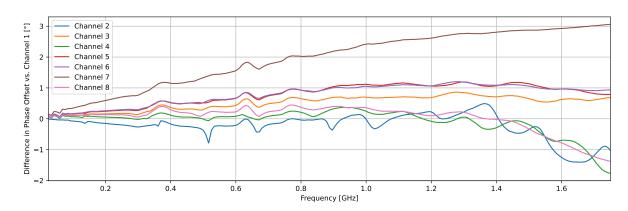

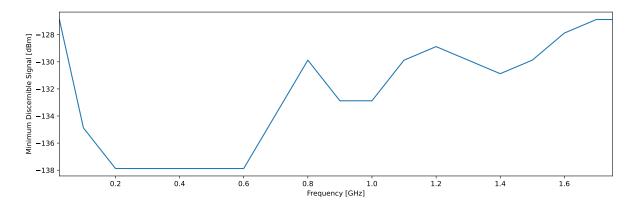

|   |       | 6.2.3   | Results            | 60         |

|   | 6.3   | Anti-A  | liasing Filter     | 62         |

|   |       | 6.3.1   | Custom tooling     | 62         |

|   |       | 6.3.2   | Prototype          | 63         |

|   |       | 6.3.3   | Methodology        | 63         |

|   |       | 6.3.4   | Results            | 63         |

|   | 6.4   |         | Supply             | 64         |

|   |       | 6.4.1   | Prototype          | 64         |

|   |       | 6.4.2   | Methodology        | 65         |

|   |       | 6.4.3   | Issues             | 65         |

|   |       | 6.4.4   | Results            | 66         |

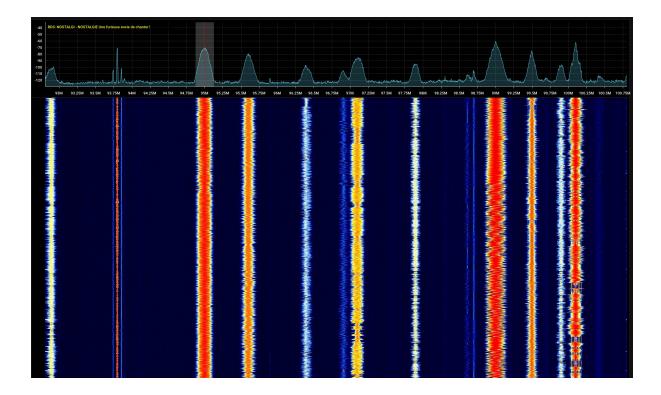

|   | 6.5   | _       | Tuner Operation    | 67         |

|   |       | 6.5.1   | Methodology        | 67         |

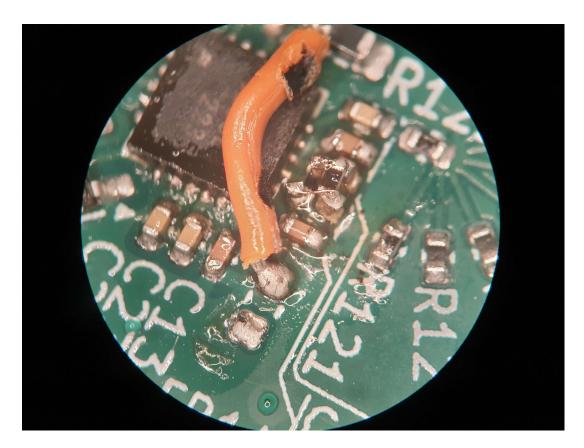

|   |       | 6.5.2   | Issues             | 68         |

|   |       | 6.5.3   | Results            | 68         |

| 7 | Con   | clusion |                    | <b>7</b> 0 |

| 8 | Ack   | nowledg | gements            | 71         |

| 9 | State | ement o | on AI use          | 71         |

## 1 Introduction

This report describes the process of designing and testing a low cost 8 channel coherent SDR receiver for use by hobbyists and education institutions in applications such as radio astronomy, beamforming experiments and satellite reception.

First, clear goals are set in order for the designed hardware to be a useful addition to the currently available software defined radio tool set. This is done by requiring that the device designed for this thesis project has at least equal or better performance to to the current cost leader. Additionally, the total price of the device must lower than the current cost leader.

Following this, the state of the art in terms of affordable coherent receivers is reviewed. A huge emphasis is set on "low-cost" as, like will be demonstrated, getting a receivers with many coherent channels is not difficult is a high budget is available. Four different devices each corresponding to a specific RF architecture are reviewed before being compared to each other.

With a clear idea of the goals and the current implementation, a hardware design is drafted and described in detail. The design process is broken up into a series of subsystems, the design and relation of which will be detailed sequentially. For each subsystem, both the schematic of the circuit and the PCB layout are described and discussed.

Next, since the hardware design will use an FPGA, the internal logic design is drafted and described. Again, the description of the design is done on a per module basis describing the relation of each module to the other through its interfaces. In the case of modules implementing a finite state machine, state diagrams will be draw up and discussed.

The FPGA design will include a soft CPU core, therefore its firmware will also be described and discussed. The description of said firmware will start by describing the initialisation procedure followed by the runtime command handling.

Finally, with the hardware, firmware and software discussed, the tests done on each system will be detailed and discussed. Specifically, the discussion will be broken up in 3 to 4 parts. First, if a prototype outside of the full receiver prototype has been created, its design is discussed. Next, the testing methodology and expected results are described. If any issue was discovered during testing, a dedicated subsection will be included to discuss them and the remediation measures that were taken. Finally, the results of the test after issues were corrected are exposed and discussed.

#### 1.1 Goals

As will be exemplified in the state of the art review, current educational and/or amateur radio grade coherent receivers are relatively expensive, only support a low number of channels and, in some cases, are not actually truly coherent out of the box. This has contributed to a situation where coherent reception is still relatively uncommon in amateur radio, and thus, means that no developments are made on the technology in the amateur space. Historically, amateur radio has been on the forefront of radio communications innovation, but without the right tools, this cannot be extended to coherent reception.

| Parameter       | Minimum | Maximum | Description                                                      |

|-----------------|---------|---------|------------------------------------------------------------------|

| Channels        | 6       | -       | At least more channels than the current cost-per-channel leader. |

| Frequency range | 144 MHz | 440 MHz | Must cover at least 2-meter and 70-centimeter bands.             |

| Bandwidth       | 2.4 MHz | -       | Must have at least the same bandwidth as a RTL-SDR.              |

| Bit-depth       | 8 bits  | _       | Must have at least the same bitt depth as the RTL-SDR.           |

| Price           | _       | \$499   | Must be cheaper than the current cost-per-channel leader.        |

Table 1: Goals set for this thesis project in terms of the receiver's performance and cost.

In order for a new coherent receiver design to be successful in the amateur radio and educational space, several conditions have to be met. First, it must support a frequendcy range which allows experimentation on amateur radio bands such as the 2-meter band and the 70-centimeter band. Second, it must have at least as much bandwidth as low-end SDR receivers such as the RTL-SDR. Indeed, anything less than that makes browsing for signals in the

area increasingly cumbersome as the user is only able to see a tiny swath of bandwidth at a time. Finally, and most importantly, it must be affordable. As will be shown later, current coherent receivers, even with only two channels easily cost over \$400, and models with even more channels easily get into the tens of thousands of dollars. With a clear understanding of what would make a good amateur radio or educational coherent receiver, it is now possible to put these traits into numbers as is done in table 1.

## 2 Background

This section investigates the state of the art in the domain of coherent software defined radio receivers, with an emphasis on those designed to be low-cost enough for educational and amateur radio use. Since there exist many different architectures of software defined radios which all have their advantages and disadvantages indepedently of their coherent capabilities, an example was chosen for each of the common SDR receiver architecture.

The LimeSDR was chosen as an example of receiver using an integrated IQ transceiver RFIC, the AMD RFSoC was chosen as an example of a direct sampling integrated transceiver, the USRP x310 was chosen as an example of a discrete IQ transceiver, and finally the KrakenSDR was chosen as an example of a discrete Low-IF receiver.

Finally, all the devices mentioned above and some more are compared to each other and conclusions are drawn to be used in the design of the receiver described in this report.

#### 2.1 LimeSDR

Figure 1: Picture of the LimeSDR Software Defined Radio receiver.

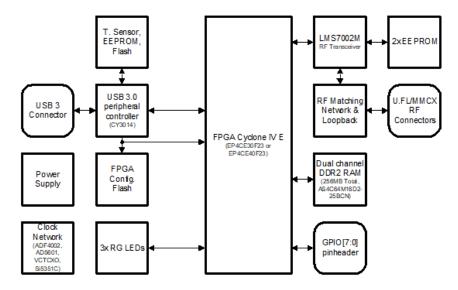

The LimeSDR[18] as shown in figure 1 is a Software Defined Radio tranceiver based on, and designed as the main development board for, the LMS7002[15] RF Integrated Circuit (RFIC). It is capable of receiving and transmitting two 51 MHz channels coherently. A block diagram of the LimeSDR is shown in figure 2.

Figure 2: Block diagram of the LimeSDR Software Defined Radio receiver.

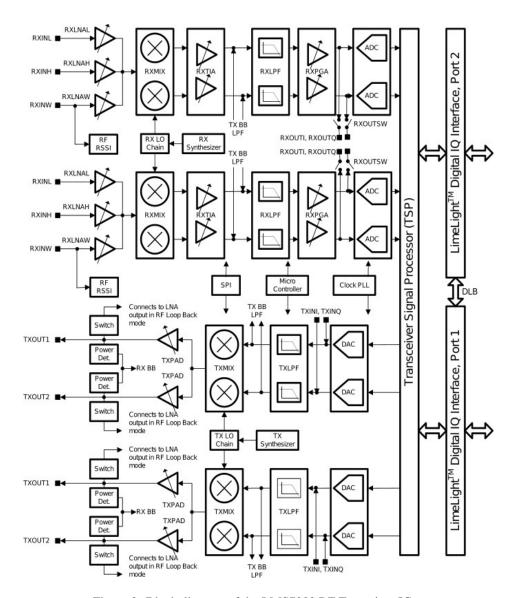

At the heart of the LimeSDR lies the LMS7002 RFIC. As shown in figure 3, RF entering the RFIC first passes through variable amplifiers before heaving to quadrature mixers. Following this, the now quadrature IF passes through another set of amplifiers and then passed through programmable low pass filters which set the receive bandwidth. Finally, the filtered IF passes through one more stage of variable amplifier before finally being sampled. The transmit path is essentially the same concept except in reverse. The fact this design is coherent comes from that fact that both channel's quadrature mixers are fed from the same local oscillator.

Both the transmit and receive Local Oscillators (LOs) are generated on-chip from a selectable reference input and can be tuned from 100 kHz to 3.8 GHz. The LMS7002 also features a built-in 8051 microcontroller capable of fully controlling the state of the transceiver outside of the actual baseband data streams. Those datastream go through a separate programmable Digital Signal Processor called the Transceiver Signal Processor (TSP).

In conclusion, this RFIC contains every part needed to create a dual channel coherent software defined radio up to the actual signal demodulation. This level of integration allows the LimeSDR to be not only remarkably compact, but most importantly to be relatively cheap at only \$350 compared to a discrete design like the USRP x310 described later.

Figure 3: Block diagram of the LMS7002 RF Tranceiver IC.

In order to be processed, the digital baseband then needs to be transfered to the host computer. For this, the LimeSDR uses an Altera Cyclone IV and a Cypress FX3 USB 3.0 interface IC. The FPGA is responsible for acting as glue logic between the USB IC and the LMS7002 RFIC as well as responding to control commands from the PC. While the Cypress FX3 is easy to integrate into designs for streaming data from a device to a PC, it has well known reliability issues[19] which have, by extension, been plaguing the LimeSDR since its release. Finally, clocking of the entire board is achieved via a SiLabs Si5351c clock generator IC using a TCXO as its reference.

While this design is relatively cheap and simple, it has one major downside: The RFIC costs over \$80 and only has two receive channels. While two channel MIMO is generally enough for diversity reception[29], more directional or complex antenna patterns are not possible. Adding more channel would require adding more of the same RFIC and using an external phase reference signal as will be done later with much cheaper RFIC in this thesis.

#### 2.2 AMD RFSoC

Figure 4: Picture of the AMD RFSoC development board from AMD's marketting material.

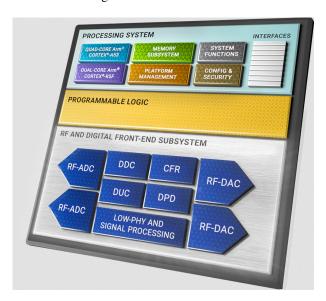

The RFSoC[5] series of RFICs shown in figure 4 are a relatively new Software Defined Radio platform developed by AMD. They feature up to 8 receive and transmit channel with a frequency range of DC to 5 GHz and a bandwidth of up to 5 GHz. This extremely high bandwidth is due to its novel direct RF sampling architecture. A block diagram of the latest RFSoC generation is shown in figure 5.

Figure 5: Block diagram of the AMD RFSoC chip as shown in AMD's marketing material.

As shown in figure 5, the AMD RFSoC integrates ultra high speed Analog to Digital and Digital to Analog converters as well as a programmable logic area, dedicated DSP and an entire hexa-core ARM SoC. As described previously, this chip uses direct RF sampling instead of analog mixers and local oscillators. This has only recently become possible for higher frequency bands as it requires extremely fast ADCs. The integrated ADCs are capable of running at up to 10 GHz. The RF signal is then down converted using Digital Down Conversion (DDC) and processed through the integrated DSP and programmable logic, after which the ARM CPU can interact with the data.

Such a high level of integration allows the RFSoC to have amazing performance per dollar in terms of bandwidth and flexibility, but it is so complex that the price is at the very upper end of what is acceptable for amateur and

educational use.

#### 2.3 USRP x310

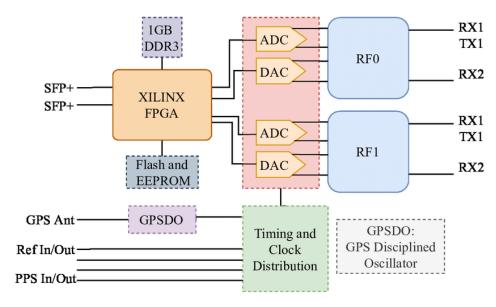

Figure 6: Ettus Research USRP x310 modular SDR transceiver.

The Ettus Research USRP x310[9] as shown in figure 6 is a modular Software Defined Radio receiver platform. Unlike the previously described devices, this design is based on discrete data converters connected through a standard daughterboard interface to user replaceable frontends. Particularly of relevance is the TwinRX[8] daughterboard which instead of providing analog IQ signals, provides one channel on the I branch and another on the Q branch. This allows, as its name indicates, to receive from two inputs coherently instead of only having one input. Since the USRP x310 has space for up to two daughterboards, a single device is able to receive on up to four channels coherently.

Figure 7: Block diagram of the USRP x310 modular SDR transceiver.

As shown in figure 7, the USRP x310 uses an FPGA to package up the samples from the data converters and send them over a standard SFP+ interface. While Ethernet over SFP+ is a relatively simple protocol to implement within an FPGA, SFP+ requires a dedicated network card in the host computer and expensive cables making it quite expensive and inflexible. The receiver possesses a frequency reference input and output as well as an integrated GPSDO socket for frequency synchronisation between devices.

#### 2.4 KrakenSDR

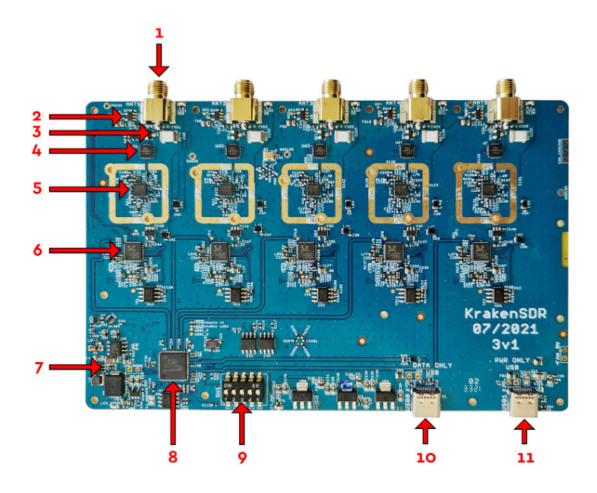

Figure 8: The KrakenSDR 5-channel coherent Software Defined Radio receiver.

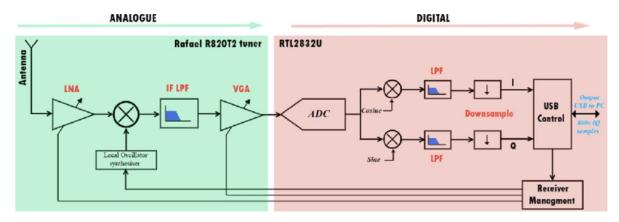

The KrakenSDR[13] shown in figure 8 as is a 5 channel Software Defined Radio receiver based on the RTL-SDR[24]. In order to truly understand it, it is first therefore necessary to understand the RTL-SDR, for which a block diagram is shown in figure 9. The RTL-SDR is based on the Realtek *RTL2832u* USB TV dongle chipset. Its original use was as a DVB-T TV dongle demodulator and USB interface, but reverse engineering efforts revealed it featured a mode in which IQ samples going to the built-in OFDM demodulator would instead be sent over USB directly[23], making it useful as an SDR receiver. The *RTL2832u* however is only half of the receiver as it still requires a frontend to give it an analog IF signal in either Low-IF or IQ format. For this, most modern RTL-SDRs use the Rafael Micro *R820T2* tuner. This tuner uses a simple heterodyne architecture with tracking filters for image rejection and include built in variable amplifiers for gain control. It also includes a fractional PLL synthesizer to generate its own LO internally.

Figure 9: Block diagram of the RTL-SDR Software Defined Radio receiver. [34]

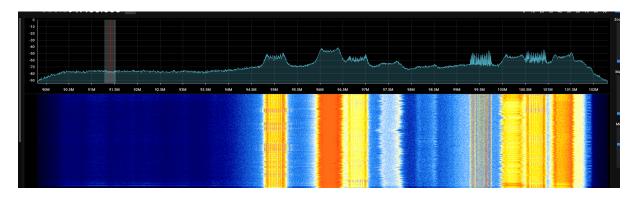

As shown in figure 10, the KrakenSDR is simply 5 RTL-SDRs sharing a common clock and communicating back to a computer through an integrated USB hub. No block diagram of the hardware is available from the manufacturer so an annotated diagram they provide as has been included here instead.

| 1. SMA Antenna inputs         | <b>5.</b> R820T2 tuner | 9. Individual tuner on/off DIP switched |  |

|-------------------------------|------------------------|-----------------------------------------|--|

| 2. Bias Tee                   | <b>6.</b> RTL2832U ADC | <b>10.</b> USB Type-C DATA              |  |

| 3. ESD protection             | 7. Noise source        | 11. USB Type-C PWR                      |  |

| 4. Noise calibration switches | 8. USB Hub             |                                         |  |

Figure 10: Annotated picture of the KrakenSDR PCB. [12]

Unlike the previously mentioned devices, the KrakenSDR is not inherently coherent. Indeed, while the five RTL-SDR are running from the same reference clock, the phase of the various PLLs used to drive the ADCs and the mixers in the tuners will take on random phase offsets relative to one another every time they unlock. In order to achieve coherence, the device features a noise source that can be switched into all of its RF inputs. The PC software is then responsible for synchronizing the channels both in time and frequency. Time synchronisation is especially difficult as buffers of samples may be lost while going over USB and buffers have no inherent guarantee to line up with one another.

#### 2.5 Comparison and Conclusions

In order to compare these coherent receiver implementations, it is first necessary to define the measure by which to rate both them and the hardware designed for this project. Indeed, as exposed in the previous examples, there is no shortages of variations for bandwidth, frequency coverage and channel count. For amateur and educational applications as targeted by this project, bandwidth and frequency coverage are secondary, within reason, to channel count. This is because if the use of the device is experimenting with beamforming and radio direction finding applications, bandwidth and frequency range are simple pass/fail requirements depending on signal the user wishes to receives and do not impact the beamforming or RDF performance in anyway. As such, channel count will be one of the factors used to rate the devices.

Since as mentioned previously the goal of this project is to create something of value to amateurs and educational institution, price must also be a factor in judging the performance. Indeed, if price is of no concern, there is already no shortage of high end offering from manufacturers like Per Vices Corporation and their 16 channel Cyan SDR costing over \$200,000[25]. As such, the final index used to rate the receivers will be  $i = \frac{p}{c}$  the price in dollar per number of channels. Table 2 shows the specifications, architecutre, price and rating index for every receiver investigated for this project. The table is sorted from lowest (best) to highest (worst) index.

| Device       | Architecture   | Freq. Range [MHz] | B.W. [MHz] | Chan. [-] | Price [\$] | Index [\$/Ch.] |

|--------------|----------------|-------------------|------------|-----------|------------|----------------|

| KerberosSDR  | RFIC (LIF)     | 25 - 1750         | 2.4        | 4         | 299        | 74.75          |

| KrakenSDR    | RFIC (LIF)     | 25 - 1750         | 2.4        | 5         | 499        | 99.8           |

| LimeSDR      | RFIC (IQ)      | 0.1 - 3800        | 61.44      | 2         | 450        | 225            |

| BladeRF 2.0  | RFIC (IQ)      | 70 - 6000         | 61.44      | 2         | 540        | 270            |

| USRP B210    | RFIC (IQ)      | 70 - 6000         | 61.44      | 2         | 2160       | 1080           |

| AMD RFSoC    | RFIC (Dir.)    | 0 - 5000          | 5000       | 8         | 16995      | 2125.375       |

| P.V. Crimson | Discrete (IQ)  | 0 - 6000          | 325        | 4         | 17000      | 4250           |

| USRP x310    | Discrete (LIF) | 10 - 6000         | 80         | 4         | 19480      | 4870           |

| P.V. Cyan    | Discrete (IQ)  | 0 - 18000         | 1000       | 16        | 208950     | 13059.375      |

Table 2: Specifications of various coherent SDR receivers sorted by the index corresponding to price per number of channels.

Inspecting table 2 reveals several notable points. First, very high end devices are, as expected, very badly rated in this comparison, costing in the worst case over 170 times more per channel then the best rated receiver. This can be explained by the fact that these receivers are targeted at very different markets like Signals Inteligence (SIGINT) and Spectrum Monitoring [26] which are happy to pay a lot more per device for higher bandwidths and frequency ranges.

Second, all the better rated devices use RFICs instead of descrete receivers. This is trivial to explain by the cost advantages or integration and mass production. Discrete receivers, IQ or Low-IF all require considerably more components since the different units are split between several integrated circuits. While this usually allows for higher performance, it significantly increases the bill of material as well as production costs.

Finally, both the best and second best rated receivers are based on the RTL-SDR. This does however mean that they are also both affected by the limitations of the RTL-SDR, supporting a bandwidth of only 2.4 MHz, over 25 times less than the next best rated receivers. The reason for this dominance in the rating is explained by the fact that they benefit from cheap consumer grade hardware repurposed for SDR use, as opposed to more expensive RFICs like those used in the LimeSDR and BladeRF which are designer for commercial telecom infrastructure [16].

## 3 Hardware

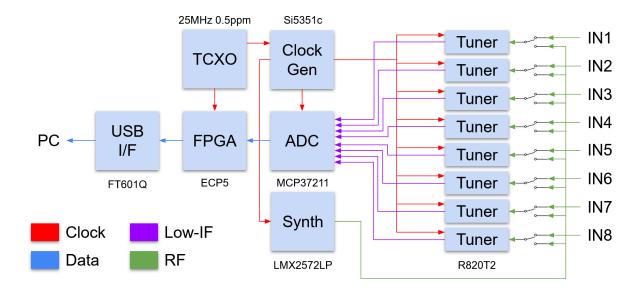

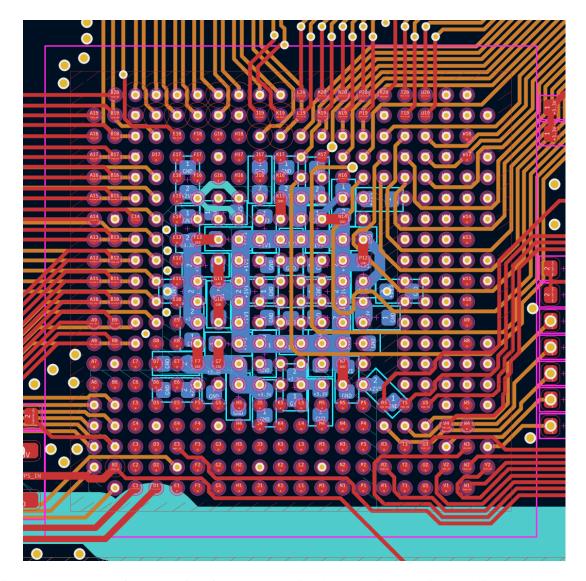

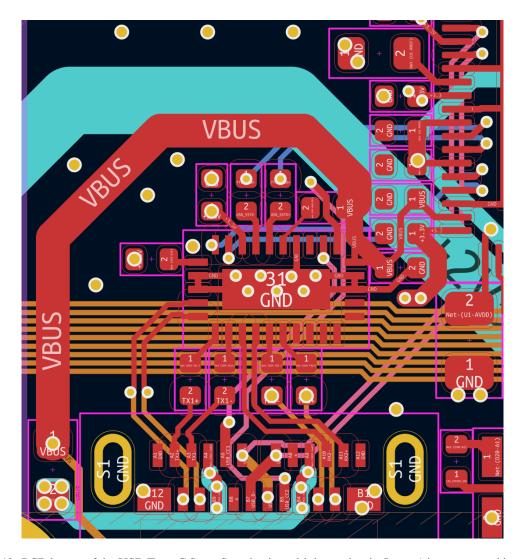

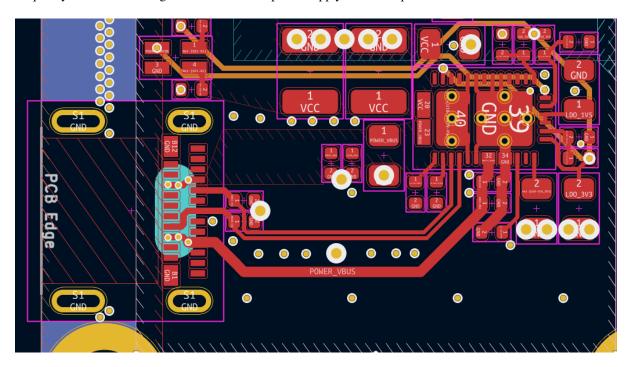

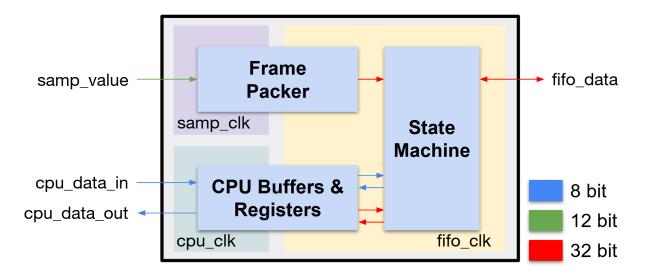

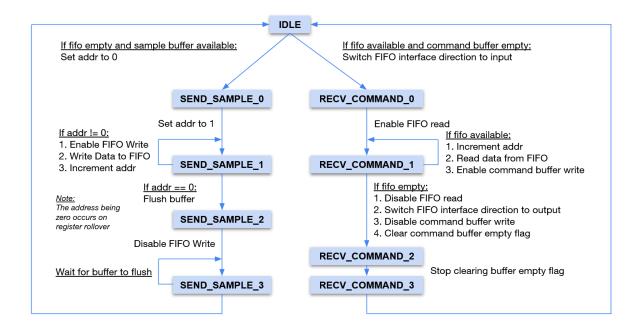

As was demonstrated when reviewing the state of the art in affordable coherent SDR receivers, re-using commodity components outside of their original purpose and working around their limitations is key to achieve an affordable receiver design. The design created for this thesis is as shown in figure 11 and an overview of said design is provided below.

Figure 11: Architectural overview of the receiver hardware. Signal conditioning components are ommitted for clarity.

Starting from the RF side, antenna input connect through Single-Pole Double-Throw RF switches to directly to individual tuners. The RF switches are used to switch out the received signal with a locally generated phase reference signal generated by a LMX2472LP single chip RF synthesizer IC. The tuners are Rafael Micro R820T2. These were originally designed as TV tuners for USB DVB-T dongles but happen to be very capable general purpose tuners. Due to behind massproduced commodity hardware, their price is extremely low at only around \$3 per unit. This explains why the phase reference is required. Indeed, these tuners come with their own integrated local oscillators and phase locked loop with no option to feed an external oscillator instead. Therefore, the reference is there so that a signal of known phase can be applied to each tuner's input and calibrate out the differences in phase that each PLL ended up with.

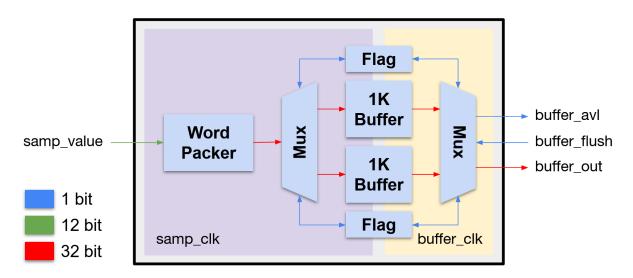

Next, the tuners output the downconverted and bandpassed signal as a Low-IF centered around 4.57 MHz. This IF passes through signal circuits conditioning not shown on the diagram before being sampled by an 8-channel 12-bit 25 Ms<sup>-1</sup> ADC. This recently released low-cost ADC from Microchip is another part that allows the receiver to be quite cheap for its performance. The digitized IF is then sent over to an FPGA for processing.

Nowadays, many low cost FPGAs are available such as Intel/Altera's MAX10 and AMD/Xilinx's Spartan series. However, in order to further reduce costs like licensing, the Lattice *ECP5* was chosen due to the fact that a fully Free and Open Source toolchain exists for it. The FPGA is, in fine, supposed to do some basic signal processing and calibration on the IFs before packaging them into fixed length packets and forwarding them to the USB fifo. As will be described later, the onboard DSP has not yet been implemented and the samples are instead immediately packed as it.

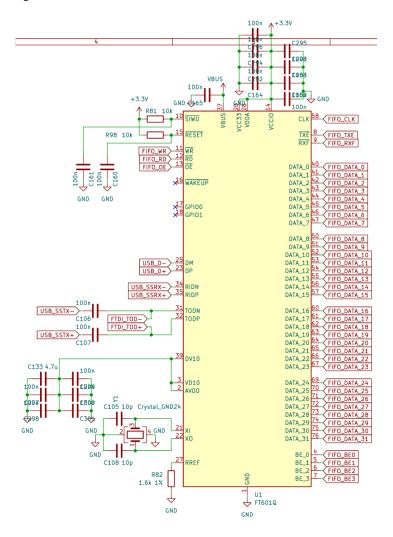

The USB FIFO used for this design is an FTDI *FT601* capable of up to 3.2 Gbit s<sup>-1</sup>, well over the maximum data rate produced by the ADC. As will be explained later, this chip was chosen for its extraordinary low cost and to avoid other ICs like the Cypress FX3 which have a bad reputation in terms of stability, and are also much more expensive.

Finally, none of these subsystems could run without a clock, so a *Si5351c* clock generator is used to take the output of the single 25 MHz precision Temperature Controlled Oscillator and generate clocks for the ADC, synthesizer

and tuners. Not shown on the diagram are the specialized splitter circuits used to distribute the the clocks and phase references adequately to the tuners.

With the rough design covered, an important part of actually implementing the design into a circuitboard is the EDA tool that will be used. For this thesis project, the Free and Open Source KiCad EDA software was chosen. This software has been in development for three decades is already used in industry. Its free and open source nature avoids the layer count or other annoying restrictions of the free versions of proprietary EDA tools such as Eagle or Altium Designer require.

#### 3.1 Frontend

The frontend of the receiver in this design encompasses the ESD protection circuit, the phase reference injection, and down conversion to a low-IF using a tuner IC.

#### 3.1.1 Input Selection

In order to calibrate the phase of each tuner it is necessary to add a Single Pole Double Throw (SPDT) switch in line with the input which allows selecting between the antenna port and the reference signal. Due to the fact that the synthesizer generating the reference signal is turned off when not in use, low insertion loss is to be preferred over high isolation. Indeed, keeping the insertion loss of the switch to a minimum is essential in keeping the noise figure of the front end low.

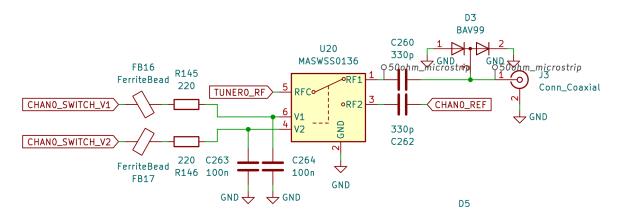

The switch chosen for this design is the *MASWSS0136* from Macom. It features a very low insertion loss of only 0.4 dB with a moderate isolation of 27 dB. It was chosen specifically for its low cost given its insertion loss. The circuit of the input selection circuit is as shown in figure 12.

Figure 12: Schematic of the input selection and protection circuit.

Starting at the input, the signal coming from the antenna connector is connected through a BAV99 low capacitance double diode to ground. This is done for ESD protection purposes as the RF switch IC does not have any built-in ESD protection. Connecting a diode directly to the RF port is simple but has two minor disadvantages. First, if a device such as a LNA imparts a DC offset onto its output and is connected to the antenna port of this device, the diode will short out the DC offset. To remedy this, an additional DC blocking capacitor could be added directly after the antenna connector. Second, although low, the parasitic capacitance of the diode will cause an impedance mismatch and thus induces reflections and losses in the frontend. The BAV99 is specified to have a maximum parasitic capacitance of  $1.5\,\mathrm{pF}$ . At the upper end of the operating frequency range of the receiver, that is  $1725\,\mathrm{MHz}$ , this creates a parallel reactance of  $61\,\Omega$ .

Assuming a  $Z_0 = 50\,\Omega$  source and RF switch input, it is possible to compute the losses due to impedance mismatch. The impedance at the receiver's input connector will the the  $50\,\Omega$  of the RF switch input in parallel with the capacitor's  $61\,\Omega$  reactange. This gives a total impedance of  $Z_L = 30.677 + 24.347i\Omega$ . The reflection coefficient is then computed as  $\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} \approx -0.1360 + 0.3428i$ . Finally, since the power reflected from the impedance change is given by  $P_{\rm in} |\Gamma|^2$ , one can conclude that the power transmitted through the impedance change is equal to

$P_{\rm in}(1-|\Gamma|^2)$ , and thus an insertion loss of  $10\log_{10}\left(1-|\Gamma|^2\right)=-0.635{\rm dB}$  is therefore to expect at 1750 MHz.

After ESD protection the signal continues through a DC blocking capacitor to the switch. All ports of the switch have a DC blocking capacitor as the interal workings of the switch is such that a DC offset will appear on its ports. The manufacturer does go into detail about this but very clearly warns about the requirement for DC blocking capacitors. The exact value of these capacitors is not crucial but the choice is explained later in the Tuner subsection.

Finally, the state of the switch is controlled through two input pins V1 and V2. In order to isolate any noise coming from the FPGA's GPIOs from the sensitive RF signals, the control signals are first run through a ferrite bead and a RC low pass filter. This low pass filter was designed to have a time constant of 50 µs which was chosen relatively arbitrarily to be short enough for switching to be fast without allowing too much signal noise to leak through at 25 MHz, that is the lower end of the receive frequency range.

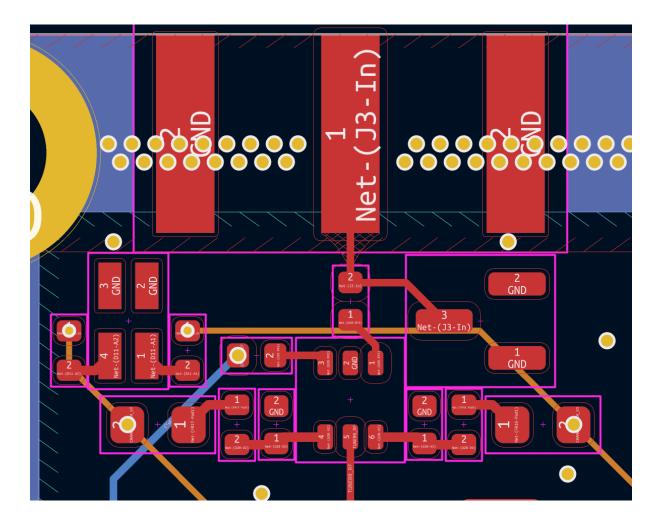

Figure 13: PCB layout of the input selection and protection circuit. Layer 1 is represented in red, layer 3 in orange and layer 6 in blue.

The PCB layout of the input selection and protection circuit is as shown in figure 13. all RF traces were layed out on the first layer and kept as short as possible to reduces losses and keep the PCB compact. Additionally, the second layer is kept a ground plane under the entire section in order to provide the ground required for the micro-strip traces and to properly isolate them from other signals running in the area.

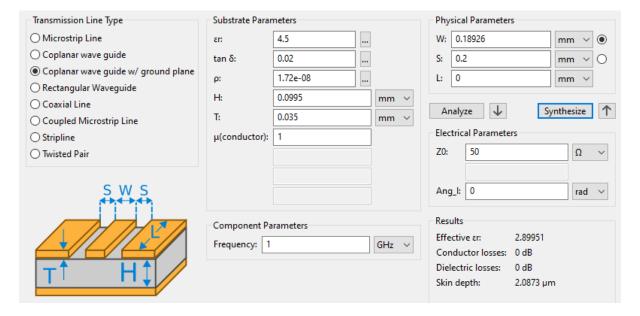

In order for the microstrip traces to be matched to both the input and the RFICs, their width must be calculates using the parameter given by the PCB manufacturer, which for this project was JLCPCB. The exact stackup used was JLC06161H-3313 using FR-4 substrate. All the physical parameters of this stackup such as layer thicknesses and dielectric indices are indicated on the manufacturer's website[10] and the stackup is shown in figure ??.

| layer       | Material Type | Thickness |                                 |  |

|-------------|---------------|-----------|---------------------------------|--|

| Layer       | Copper        | 0.035mm   |                                 |  |

| Prepreg     | 3313*1        | 0.0994mm  |                                 |  |

| Inner Layer | Copper        | 0.0152mm  |                                 |  |

| Core        | Core          | 0.55mm    | 0.55mm<br>(without copper core) |  |

| Inner Layer | Copper        | 0.0152mm  |                                 |  |

| Prepreg     | 2116*1        | 0.1088mm  |                                 |  |

| Inner Layer | Copper        | 0.0152mm  |                                 |  |

| Core        | Core          | 0.55mm    | 0.55mm (without copper core)    |  |

| Inner Layer | Copper        | 0.0152mm  |                                 |  |

| Prepreg     | 3313*1        | 0.0994mm  |                                 |  |

| Layer       | Copper        | 0.035mm   |                                 |  |

Figure 14: Stackup specification as shown on the PCB manufacturer's website[10].

The values for the first and second layer as well as the dielectric between them can then be entered in KiCad's integrated micro-strip calculator aiming for a trace impedance of  $50\,\Omega$  and a microstrip type of coaxial waveguide. The results of the calculation are as shown in figure 15. The calculator shows a required width of 0.189 mm. Since the stackup is symmetric, the results are also valid for traces run on the under side of the PCB such as the phase reference signals.

Figure 15: Interface of KiCad's Micro-strip calculator with the stackup information and desired settings filled out and the results visible.

As shown in figure 13, the protection diode was placed as close as possible to the input in order to reduce the impedance to it and thus better protect the circuit in case of en ESD event. After going throught the DC blocking

capacitor mentioned previously, the signal reaches the RF switch IC. The control signals for this switch arrive from the internal 3rd layer passing under the ground plane and then go through the filters described in the explanation of the schematic. These signals and filters are layed out orthogonally to the RF traces arriving to and leaving from the switch helping with isolation. The phase reference signal arrived from the bottom layer and goes directly into the DC blocking capacitor and switch.

#### **3.1.2** Tuner

The job of the tuner is to take the un-conditioned RF signal from the antenna, extract a certain frequency range from it and down-convert it to an Intermediate-Frequency (IF). In the past, this would have required multiple chips, hundreds of passive components and would have required manual tuning or "Alignement". Thanks to advances in RF technology and the need for mass production of radio/television enabled devices, such a circuit is now available in single ICs.

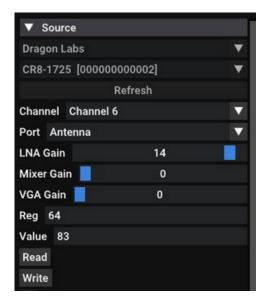

For this project, the R820T2 from Rafael Micro was selected. It features an official frequency range of 42 MHz to 1002 MHz, but has been confirmed by many amateur projects to work fine from 25 MHz to 1750 MHz. The tuner outputs a  $2 \,\mathrm{k}\Omega$  impedance differential Low-IF where the passband is located between 1 MHz and 9 MHz. This results in a usable bandwidth of 8 MHz which, for its original purpose, was enough to receive the widest standards DVB-T signals. This chip has been the basis of many of the best selling amateur Software Defined Radio devices in the past 15 years. This is due to its incredible performance for its price. In large quantities, this chip can be bought for less than 2 dollar a piece, a price unmatcheable by discrete circuitry. Notable devices using this chip are the RTL-SDR[24] and Airspy [2].

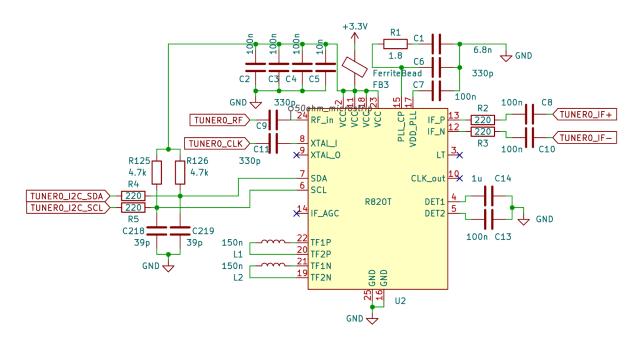

Figure 16: Schematic of the tuner sections.

As shown in figure 16, the R820T2 requires very little external circuitry to work. First, its single 3.3 V supply rail is filtered using a ferrite bead as well as 100 nF capacitors on each of it's power input pins. The R820T2 also exposes two internally generated voltages for external decoupling. The first is the PLL\_CP pin which is the voltage generated by an internal charge pump used to power the integrated Voltage Controlled Oscillator [3]. The second is VDD\_PLL which is the power supply for the PLL. The manufacturer gives the exact decoupling circuits for each of these pins so design was not necessary or even recommended in the first place.

The RF and reference clock are fed to the tuner via 330 pF DC blocking capacitors. The value of these capacitors was again specified in the datasheet but can be explained by the requirement of having a low impedance at the lowest operation frequency. Using the traditional capacitor impedance formula, it can be calculated to be only  $20\,\Omega$  at 25 MHz. While it would be possible to simply use a higher value capacitor, it was decided to keep

the manufacturer recommended value since such a small impedance change is not worth straying away from the recommended value which may cause issues with the DC offset output from the switch IC such as damage to the input of the tuner caused by the charging current of the DC blocking capacitor at power on. On the IF side, the DC blocking capacitor and protection resistors were also specified by the manufacturer. Since the IF is not used outside of its official specs, there is no need to recompute these values.

Next, some additional passive components are required. First are the two 150 nH inductors. These serve as the basis of the internal tracking input filters of the tuners. Their value are obviously specified by the manufacturer as they have to work with the internal immutable circuitry of the IC to resonate at the correct frequency. Second are the decoupling capacitors connected to the DET1 and DET2 pins. These serve as low pass filters for the power detectors built into the R820T2 for use by the intergrated Automatic Gain Control. Since this feature will not be used and the effect of leaving them unpopulated is not known, they were included with their manufacturer recommended value.

In order to reduce noise going into the tuner from the digital section and as per the manufacturer's specifications, RC low pass filters are included on the I2C pins of the tuner. The values specified by the manufacturer were used as is but it is possible to confirm that they are sensible. Knowing the 3 dB corner frequency of a RC filter is given by  $F_{3dB} = \frac{1}{\pi RC}$ , one can conclude that  $F_{3dB} = 18.55$  MHz, which is both well over the maximum operating frequency of the I2C bus of  $100 \, \text{kHz}$ , but also well below the lower end of the receive frequency range of 25 MHz ensuring that the I2C communications won't be disrupted and that the noise coming from these lines will be attenuated in the receive frequency range.

Finally, the Low-IF output if the tuner passes through some  $220\,\Omega$  protection resistors and DC blocking capacitors before going off to the rest of the receiver circuit. The value of the DC blocking capacitors are much higher at  $100\,\text{nF}$  than those on the RF side due to the much lower frequency of 1 MHz at which they are to operate. Their exact value is again not critical so the very commonly used value of  $100\,\text{nF}$  was chosen. This creates a series impedance of  $1.591\,\Omega$  which is negligeable compared to the  $2\,\text{k}\Omega$  differential impedance of the IF.

#### 3.2 Clocks

The description of the clock generation hardware will be split into two section. First, the generation of the clock signals will be discussed, followed by splitter circuit used to feed the 8 tuners.

#### 3.2.1 Generation

As shown in the overview, three subsystems of the receiver require separate clock signals as listed below.

- 1. **Tuners:** Each tuner require a fixed 16 MHz CMOS clock.

- 2. **Synthetize:** The phase reference synthesizer requires a configurable 5 to 125 MHz LVDS clock.

- 3. **ADC:** The ADC requires a LVDS sampling clock equal to the desired sample rate. For this design, this means 200MHz.

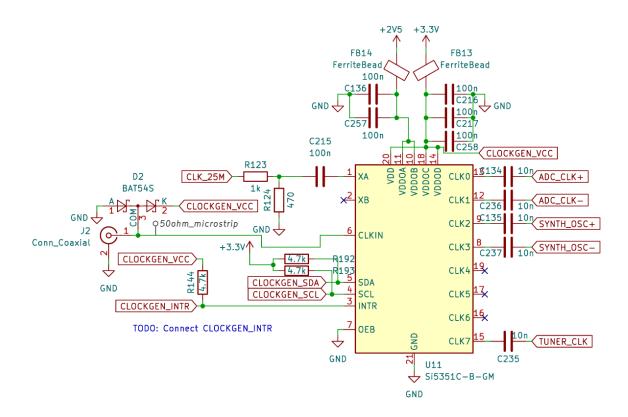

A very popular clock generator that fits these requirements is Silicon Labs's Si5351C-B [28]. This clock generator features 8 CMOS or 4 LVDS outputs that can range in frequency from 25KHz to 200MHz. This chip requires a 25 or 27MHz input clock, so this design includes an onboard 25MHz Temperature Controlled Oscillator (TCXO) with 2ppm frequency stability which will be discussed later in this section. The Si5351C-B also features a 10MHz reference input which can be used as the input clock for its PLL in order to use an external high precision reference such as a Oven-Controlled Oscillator (OCXO), GPS Disciplined Oscillator (GPSDO), Rubidium standard or other atomic clock. The circuit for this clock generator is shown in figure 17.

Figure 17: Schematic of the clock generation section of the receiver.

Power for the Si5351C-B's power rails first pass through ferrite beads to create a high impedance for high frequency components in the power supply. This is done because any interference on the power rails of the clock generator will translate directly to phase noise in its generated clocks. Power is then distributed to each of the power pins in parallel with 100 nF decoupling capacitor.

The Si5351C-B requires a 3.3 V for VDD. The output buffer power inputs VDDOx's voltages depend on what is connected to them. VDDOA covers outputs 0 and 1, VDD0B covers outputs 2 and 3 and so on. The unused output pins CLK4, CLK5, CLK6 as well as the output going to the tuners CLK7 are all configured as CMOS and correspond to VDDOC and VDDOD which are therefore connected to 3.3 V. On the other hand, output pins CLK0, CLK1, CLK2, CLK3 are connected to the ADC and phase reference synthesizer and are configured as LVDS which requires a 2.5 V supply according to the Si5351C-B's datasheet [28].

The oscillator input XA of the Si5351C-B expects a maximum voltage of 1.3 V. As such, a resistor divider required to reduce the 3.3 V of the 25 MHz TXCO. This can be done with a division ratio of around 3 and was achieved using  $1 \text{ k}\Omega$  and  $470 \Omega$  resistors. These values were chosen because they were already required elsewhere in the circuit which avoids adding different component values to the Bill of Material. A 100 nF DC blocking capacitor is also added as per the manufacturer's recommendations.

The 10 MHz reference input is CMOS compatible is this directly connected to the input connector. For Electrostatic Discharge (ESD) protection, some reverse-biased diodes are connected from this input to ground and 3.3 V.

Finally, the I2C pins are pulled up to 3.3 V by  $4.7 \text{ k}\Omega$  resistors and so is the *INTR* pin which didn't end up being used. The signals go straight to the FPGA for controlling the chip.

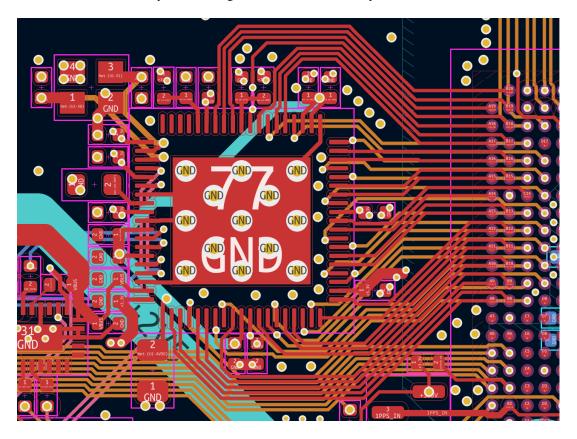

The layout of the clock generation section of the receiver is as shown in figure 18.

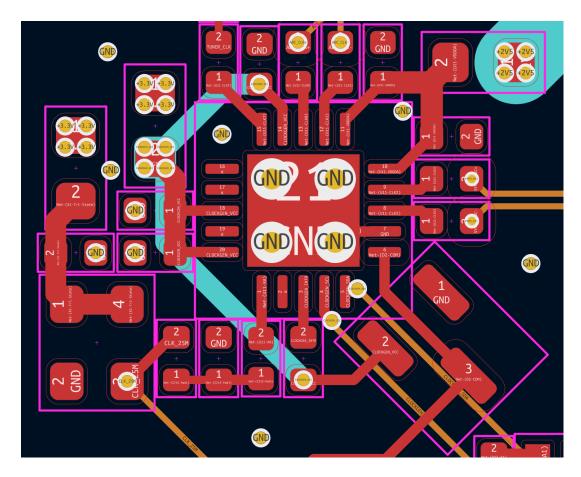

Figure 18: PCB layout of the clock generation section of the receiver. Red corresponds to the first layer, orange to the third and cyan to the forth. Layer 1 is represented in red, layer 3 in orange and layer 4 in cyan.

As can be seen in figure 18, decoupling capacitors are always placed directly in front, and as close as possible to their respective power pins. This is done in order to minimize the impedance to the decoupling capacitor which helps reduce power rail ripple. Four large vias are placed on the ground pad of the *Si5351C-B*. This is done both to help with thermal dissipation, but also to ensure a very low impedance path to ground.

Most signals are routed directly on the top (red) layer, with power rails on the 4th and 5th (not visible in the figure 18) and inter-section signals on the 3rd layer. Layers 2 and 6 are used as dedicated ground layer, and all unused areas of layers 3 are also connected to ground.

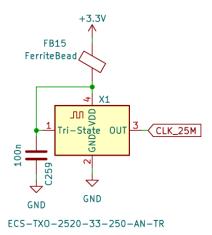

Figure 19: Schematic of the Temperature Controlled Oscillator used as the 25 MHz source of the clock generator.

As mentioned earlier, a 25 MHz CMOS clock is necessary for the *Si5351C-B* to operate. This is provided by a 2 ppm TXCO as shown in figure 19. Just like the clock generator, a ferrite bead and decoupling capacitor are placed at the power input of the TCXO in order to attenuate high frequency components from the power rail and improve phase noise performance.

#### 3.2.2 Distribution

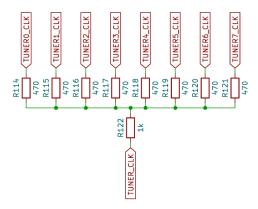

Finally, the generated clock must be split out to each tuner. Contrary to what one would expect, matching the phase of these clock signals to each tuner is not actually necessary. Indeed, any phase shift to these signals will be calibrated out anyway when compensating for the random phase offset of each of the tuner's PLL. However, in order to ease debugging, best efforts were made to still keep these signals in phase. Clock splitting is implemented using a simple resistive network as shown in figure 20.

Figure 20: Schematic of the resistive clock splitter used to feed all 8 tuners from a single output of the clock generator chip.

This circuit is implemented in such a way to accomplish two things. First, the level of the clock signal must be dropped from the 3.3 V LVCMOS output of the clock generator down to around 150 mV. This is because the tuners were not originally meant to be driven by a regular clock, they are designed to resonate using an external crystal and have a built-in oscillator amplifier. Driving them at 3.3 V could potentially lead to damage. Second, each tuner must have a relatively high impedance to the next. This is done to prevent unwanted interactions between the tuners such as signal and noise leakage. The exact values of this splitter were tentative as no specifications are available on the crystal port of the tuner. These values were suggested by Mr. Youssef Touil from Airspy SA. who has significant experience using the R820T2 chip. The layout of this splitter is shown in figure 21

Figure 21: PCB layout of the resistive network used to split the tuner clock into 8 in-phase clock signals. Layer 1 is represented in red and layer 3 in orange.

The network is layed out in such a way that it is fully symetric from the clock source to each tuner and thus won't shift the phase of the clock. Of course, the wave length of the 16 MHz clock, equal to  $\lambda = \frac{c}{F} = 18.737 \,\mathrm{m}$  is extremely large compared to the circuit which is in the order of a few millimeters. This means that any asymetry in this section would have a minimal effect, but it is still good practice to use a symetric layout as that has effectively no cost.

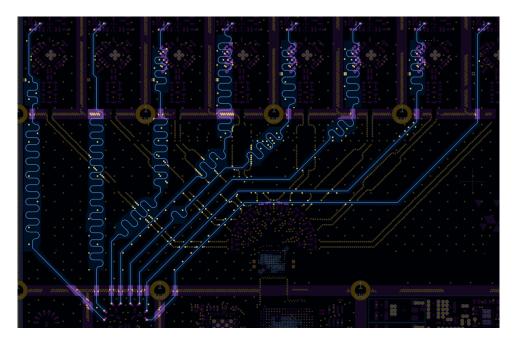

Finally, after being split, the clock signals have to be routed to their respective tuner ICs. As shown in figure 22, the clock signals are run on the third layer, first groupe together and then spread out shortly before reaching the tuners. Before each tuner, length matching sections are implemented to ensure the phase of the clock reaching each tuner is identical. The geometry of these length matching sections is automatically computed and generated by KiCad given a desired length, which in this case was simply the length of the longest trace before length matching.

Figure 22: Routing of every clock signal generated by the Si5351c clock generator. The signals in question are highlighted.

#### 3.3 Phase Reference

The description of the phase reference hardware will be split into two section. First, the generation of the refrence signal will be discussed, followed by the design and analysis of its distribution circuit.

#### 3.3.1 Generation

As described earlier, each tuner in this design uses its own internal synthetizer generated from their clock input as their local oscillator. Unfortunately, this means that even while sharing the same input clock, all tuners will only be frequency locked and not phase locked. Any time their integrated PLL unlocks, for example when tuning to another frequency or when powering them off while the receiver is idle, their relative phase is randomized. As such, a phase reference signal is generated and distributed to each tuner. The purpose of this signal is to provide known phase reference that can be used to infer the phase offset of each tuner, and thus make the entire system truely coherent.

There are relatively few requirements on this reference signal. It must of course have relatively low phase noise to avoid requiring impractically long calibration periods, but most importantly, it should cover the entire desired frequency range of the receiver.

As such, Texas Instrument's LMX2472LP was chosen for its low price and fitting the requirements outlined above. This chip features two parallel output of which only one will be used. It's able to cover a frequency range of 12.5 MHz to 2 GHz which almost perfectly fits the receiver's frequency range. It is controlled via a Serial Peripheral Interface (SPI) bus and only requires a single clock input anywhere from 5 to 125 MHz.

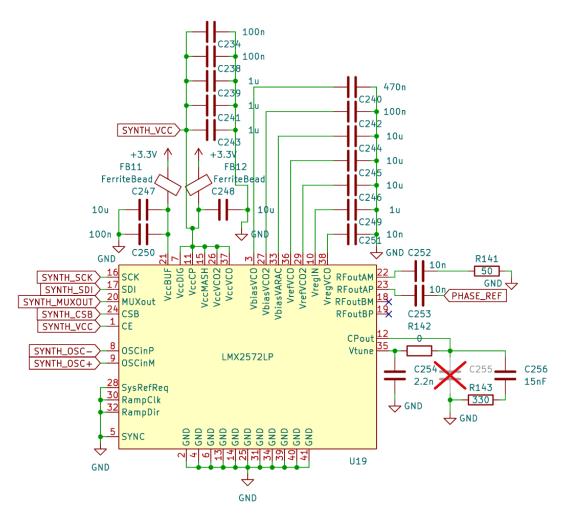

The phase refence circuit is as shown in figure 23.

Figure 23: Schematic of the phase reference synthesizer.

Just like for the clock generation, power for the *LMX2572LP*'s power rails first pass through ferrite beads to create a high impedance for high frequency components in the power supply in order to attenuate high frequency component in the power supply. Power is then distributed to each of the power pins in parallel with decoupling capacitors of which the characteristics were specified by Texas Instruments [30]. As per the manufacturer's specification, separate ferrite beads were used for the output buffer power pins in order to insolate them better from the rest of the chip's power rails.

The *LMX2572LP* provides dedicated pins for decoupling various internal signals. The required values of the capacitors on these pins were also directly given in the datasheet.

The output of the synthesizer being  $100 \Omega$  differential, it is necessary to adapt it to  $50 \Omega$  single ended. For this, DC blocking capacitor are first added to each side of the differential output, after which the positive side is connected to ground through a  $50 \Omega$  resistor and the negative side goes out to the distribution network. This looks to the chip

as if there was a  $100\,\Omega$  differential load on its output while being extremely wide band and cost effective, unlike a balun for example. Whether the positive or negative side of the output is connected to the grounded resistor does not matter since only the relative phase between tuners is of concern. For this project, the negative side was chosen as this made routing easier on the PCB.

Another important part of the phase reference circuit is the loop filter composed of C254, C255, C256, R142 and R143. The manufacturer does not give particular guidance on designing this filter and asks to use their software to design it. Fortunately, the schematic for the evaluation board of the LMX2572LP is available so the values for these parts was taken from it. As can be seen in the schematic, both C255 and R142 were not needed and thus were replaced respectively with nothing (Do Not Populate) and a  $0\,\Omega$  jumper.

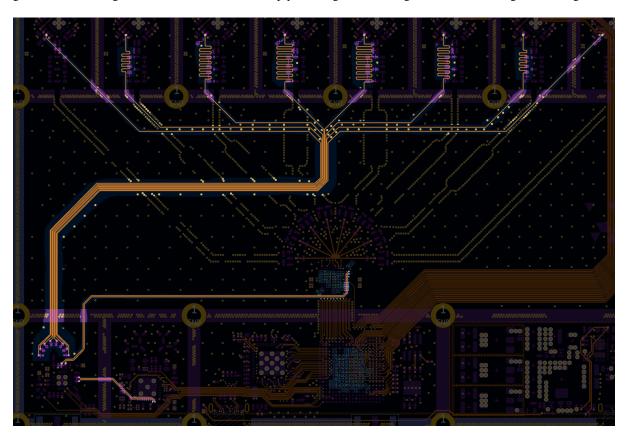

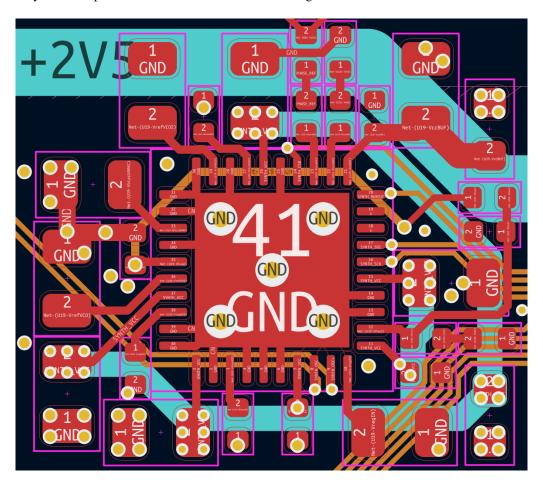

The PCB layout of the phase reference section is as shown in figure 24.

Figure 24: PCB layout of the phase reference generation circuit. Layer 1 is represented in red, layer 3 in orange and layer 4 in cyan.

#### 3.3.2 Distribution

The most critical property of the phase reference signal is that it must arrive at each frontend with exactly the same phase. Indeed, any phase offset in this reference would directly translates into a phase error because the phase calibration algorithm assumes the references have the same phase on every channel. Like the tuner clocks, distribution of the phase reference consists in first splitting it and then routing it to the frontends.

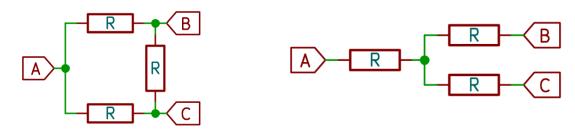

To split the reference, both an active or passive splitter could be used. Since the tuners are extremely sensitive, losing power in the phase reference is not only desirable, but mandatory to avoid damaging the tuners. Thus, a passive resistive splitter is chosen. In order to design this splitter, lets first start by inspecting the two most common three port networks, that is the *Delta* configuration as shown in figure 25 and the *Star* configuration as shown in figure 26.

Figure 25: Three-port "Delta" configuration network.

Figure 26: Three-port "Star" configuration network.

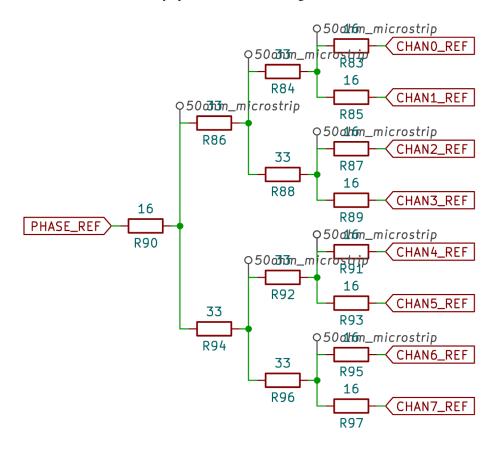

While both of these networks can achieve the goal of splitting the signal between multiple ports, one has to consider how the circuit will evolve when trying to stack this circuit recursively in order to get an 8-way splitter. In the case of the *Delta* network, one would end up with 3 \* (1 + 2 + 4) = 21 resistors with no obviously way to simplify the resistors. However, when using the *Star* network, one can notice that the output resistor of one stage and the output resistor of the other are in series and can thus be added up to 2R. This reduces the number of required resistors from 21 to only 1+2+4+8=15, making the *Star* network 29% more spare/cost efficient that the *Delta* network.

Going back to the signle stage *Star* network, since the impedance on each port assuming a  $50\,\Omega$  termination on the two other must be  $50\,\Omega$ , we can conclude that all three resistors must be equal by symmetry. Solving for R is shown in equation 1.

$$R_{\rm A} = R + \frac{1}{\frac{1}{R+50} + \frac{1}{R+50}} = \frac{3R+50}{2} = 50 \iff R = \frac{50}{3} \approx 16.667 \,\Omega$$

(1)

Knowing the value of R, it is now possible to build the full 8-way splitter using both R and 2R resistors as explained above. The schematic for this final 8-way splitter is as shown in figure 27.

Figure 27: Circuit of the 8-way resistive splitter used to split the phase reference to the 8 frontends.

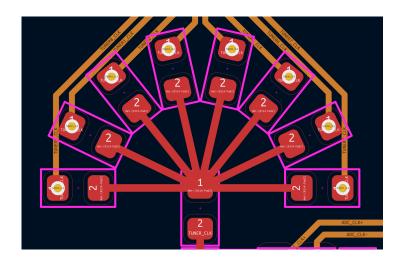

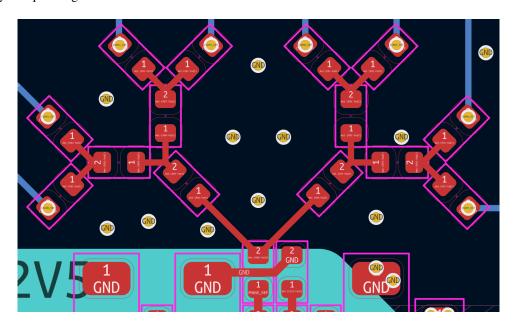

Of course, the circuit is only one part of ensuring that each output receives the same phase. The second part is

the physical layout of the components. Indeed, the phase reference frequency can be as high as 1750 MHz which corresponds to a wavelength of approximately 17 cm. This corresponds to a phase offset of over 2° per millimeter, meaning that the physical layout of the circuit will be crucial to ensuring phase matching on all ports. As shown in figure 28, each branch of the splitter is made to be recursively symetric with the last, ensuring that all paths are perfectly of equal length.

Figure 28: PCB layout of the 8-way resistive splitter used to split the phase reference to the 8 frontends. Layer 1 is represented in red, layer 4 in cyan and layer 6 in blue.

Finally, just like the tuner clocks, the phase references must be routed to the frontends making sure that all they all arrive to the front ends with the exact same phase. This is done by running the signals on the bottom layer of the PCB and adding length matching sections so that all traces end up the same length as shown in figure 29

Figure 29: PCB layout of the traces going from the 8-way splitter to each frontend.

#### **3.4** ADC

The Analog to Digital Converter (ADC) is the one chip that this entire design was built around. The MCP37211-200 [17] from Microchip features 8 channels multiplexed to a central 12bit 200MS/s core allowing a samplerate per channel of up to 25 MHz. Due to this chip's intended use in radar and sonar applications, it features a built in Digitial Signal Processor capable of time-shifting the samples of each channel such that they are virtual sampled at the same time. This allows to simulate a 8 channel non-multiplexed ADC but comes at the cost that the resampling filters use only properly time shift the samples within a certain frequency rangek, specifically up to approximately 9 MHz.

What truely sets this chip apart from the alternative is it's extremely low cost of only \$27 in single quantities. This is what allows this receiver design to be viable in the first place. As discussed in the Background section, previous designs had to make due with either multiple very cheap ADCs which required external time synchronisation and calibration, or expensive multi-channel ADCs that were often too high performance for hobby or educational level hardware.

#### 3.4.1 Anti-Aliasing Filter Design

First, the IF signals to be sampled must be adequately low-pass filtered to avoid out-of-band components appearing in the final passband. The design of this filter is based on three variables. First, the sampling rate of the ADC which in this case is 25 MHz per channel, second, the desired alias-free passband, which the manufacturer specifies as 0.57 MHz to 8.57 MHz and third, the desired minimum attenuation of these out of band signals.

The sampling frequency being significantly higher than the upper passband frequency as well as the way signals over  $F_s/2$  fold back means that the filter doesn't need to be as sharp as one would expect. Indeed, the frequency  $F_d$  at which a signal of frequency  $F_a$  in nyquist zone n appears in the digital signal after sampling at sampling rate  $F_s$  is given by equation 2.

$$F_{\rm d} = \pm \left[ (n-1)F_{\rm s} - F_{\rm a} \right] \begin{cases} + \text{ if } n \text{ even} \\ - \text{ if } n \text{ odd} \end{cases} \qquad F_{\rm a} \in \left[ \frac{n-1}{2} F_{\rm s}, \frac{n}{2} F_{\rm s} \right] \qquad n \in \mathbb{Z}_0^+$$

(2)

The frequency of signals in the second nyquist zone (n = 2) necessary to reach the 9 MHz upper limit of the passband is therefore trivially computed assuming  $F_{\rm d} = 8.57$  MHz and  $F_{\rm s} = 25$  MHz giving  $F_{\rm a} = 16.43$  MHz which is the frequency at which the anti-aliasing filter will be expected to provide the desired minimal out of band attenuation.

The required out of band attenuation can be deduced from the tuner and ADC specification. Ideally, one should base the antialiasing filter specifications on the specifications of the filters higher up the RF chain. Unfortunately, the manufacturer of the tuner does not provide any such data. However, as previously described, the tuner is originally meant for DVB-T usage, and us thus, reports the minimum adjacent channel attenuation that it is capable of. This value can be used along with the ADC's maxmimum Signal to Noise ration to compute the attenuation at which an out of band signal will be below the ADC's noise floor. The tuner reports a minimum adjacent channel rejection of -47dBc, and the ADC supports an SNR of 71.33dBFS. Therefore, the anti-aliasing filter must provide at the very least 71.33 - 47 = 24.33 dB of attenuation at the previously computed 16.43 MHz point.

With all the parameters of the requirements of the filter in hand, it is now possible to select a filter type. Before that however, one has to chose between an RC and LC filter. In terms of cost, an LC circuit is naturally more expensive than a RC filter as inductors, especially precise ones, are more expensive. However, they feature twice as fast amplitude drop off and no passband attenuation, therefore a LC filter is chosen for this use case. There exist many types of LC low-pass filters, a comparison of which is shown in table 3.

| Type Roll-off ra |          | Passband ripple | Group delay variations | Ultimate attenuation |

|------------------|----------|-----------------|------------------------|----------------------|

| Bessel           | Very low | None            | Very low               | Unbounded            |

| Butterworth      | Low      | None            | Small                  | Unbounded            |

| Legendre         | Low      | None            | Moderate               | Unbounded            |

| Chebyshev        | Moderate | Present         | Moderate               | Unbounded            |

| Elliptic         | High     | Present         | Large                  | Bounded              |

Table 3: Qualitative comparison of common LC low-pass filter types at a given order sorted by roll-off rate from slowest to fastest as described in [?].

From this comparison, it is possible to understand that a fast roll off comes with numerous trade off. Firstly, filter types with a higher roll-off rate have passband ripple. This, if kept within reasonable bounds is not problematic. The second issue are group delay variations. In the case of audio processing, this is generally not problematic as the human ear cannot hear phase information, however, for a modulated digital signal, a nonlinear phase will cause distortion and thus increase the bit error rate. The final investigated parameter is ultimate attenuation, and it is shown that it is bounded for elliptic filters, which means that the filter has an attenuation value that it will not exceed no matter the input frequency.

As such, a Chebychev filter is chosen due to its higher roll off rate while featuring only moderate group delay variations and an unbounded ultimate attenuation. From here, it is now possible to determine the order necessary to achieve the required attenation. For this, a filter calculator tool by Marki Microwave[?] was used to compute filter designs of increasing order. The tool allows to specify a few more parameters then previously established, such as impedance and maximum allowable passband ripple. For the impedance, the same impedance as the tuner of  $2 k\Omega$  differential preferable. However, since the filter design tool is meant for single-ended filters, the impedance is specified as  $1 k\Omega$ , after which the components will be mirroed to form a differential filter. For the passband ripple, a standard 0.1 dB value is used. One important thing to note is the filter is configured to limit its component choices to standard 5% precision values, ensuring manufacturability with off-the-shelf components. The results from the tool are as shown in table 4.

| Order | Attenuation at 16.43 MHz |  |  |

|-------|--------------------------|--|--|

| 1     | −0.278 dB                |  |  |

| 2     | −1.021 dB                |  |  |

| 3     | −12.529 dB               |  |  |

| 4     | −20.882 dB               |  |  |

| 5     | −32.575 dB               |  |  |

| 6     | −42.042 dB               |  |  |

Table 4: Results of the filter calculator tool for different filter orders

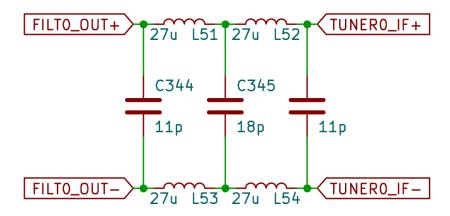

These results show that in order to achieve the previously described required attenuation, a filter order of at least 5 is necessary. Going with an order higher than 5 would only add more components and cost to the design, so 5 is chosen as the filter order for this design. The component values generated by the calculator tool, after mirroring the filter circuit to create a differential circuit are as shown in figure 30.

Figure 30: Circuit of the 5th order Chebyshev low-pass filters designed for use as anti-aliasing filters in front of the ADC.

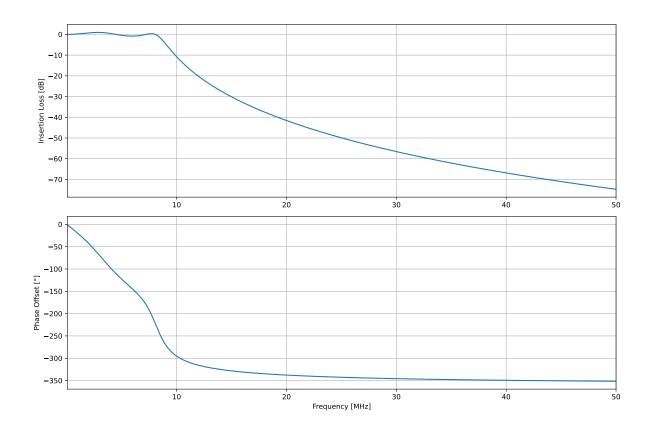

In order to verify that the values generated by the tool result in a filter with the desired response, the circuit is first simulated using the LTspice[?]. This yields the filter response shown in figure 31.

Figure 31: Bode plot of the anti-aliasing filter as computed by the LTspice circuit simulator software.

The simulation results show that the attenuation is even slightly higher that what the Marki Microwave filter design tool. This is almost certainly because of slight manual selection errors when selecting the position of the marker for 16.43 MHz. Next, the passband ripple is clearly over the 0.1dB value configured in the tool. This is likely due to the fact that the tool had to chose standard component values which are slightly off the theoretically ideal values. Finally. the 3dB corner frequency is computed to be 8.754 MHz. This is slightly different from the 8.57 MHz corner frequency that the tool was instructed to use, but this is again explained by the tool being forced to chose standard component values.

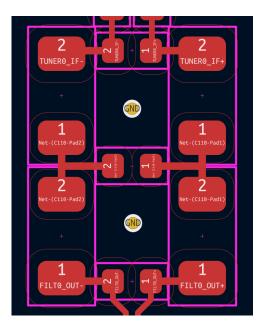

Figure 32: PCB layout of the anti-aliasing filter.

Finally, the layout of the anti-aliasing filter is as shown in figure 32. The anti-aliasing filter is layed out with the shunt capacitors in between the inductors in order to reduce the total length of the filter. The anti-aliasing filter are placed inside of the tuner compartment in order to reduce cross-talk between channels as much as physically possible.

#### 3.4.2 Input Driver

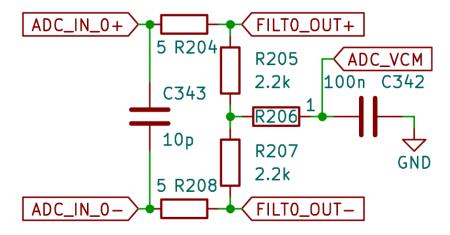

Coupling the output of the anti-aliasing filter to the ADC requires two main steps. First, the ADC requires a precise common mode offset on its input that it generates by itself. Second, a kickback filter is required in order to minimize the amount of ADC sampling noise that makes it back to the tuner through the IF filter. The circuit create to drive the ADC's input is as shown in figure 33.

Figure 33: Driver circuit for the ADC.

Traditionally, this is accomplished either by using a dedicated ADC driver amplifier, or by using a transformer. An ADC driver amplifier would be relatively expensive as 8 separate units would be required. Transformers would have the same issue, with the added problem they take up a significant amount of space on the PCB. Therefore, a fully passive driving circuit is designed. Starting with the kickback filtering capacitor, its value was chosen to be as large as possible without significantly reducing the bandwidth of the ADC's input.  $5\,\Omega$  resistors are added in series with each branch as per the manufacturer's recommendation to reduce ringing which would be caused by the high transient currents when the sampling switches close. Then, for DC offset injection, a resistor divider between the positive and negative branches. The value of the resistors is chosen such that the total impedance as seen by the the tuner is close to  $2\,\mathrm{k}\Omega$ .

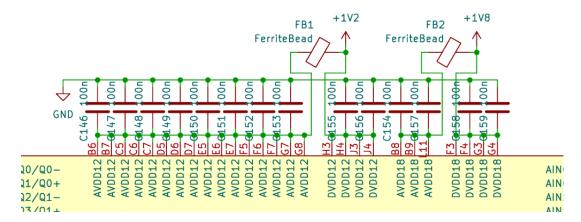

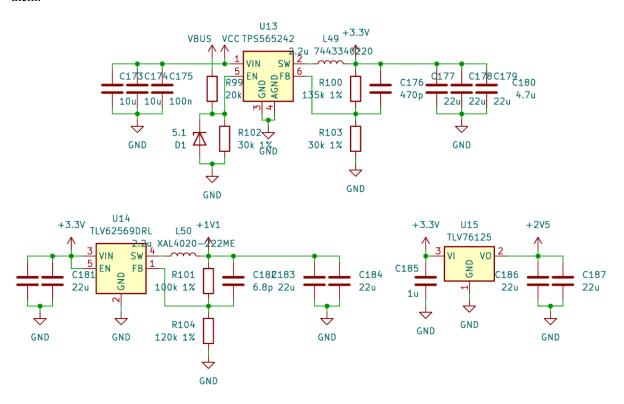

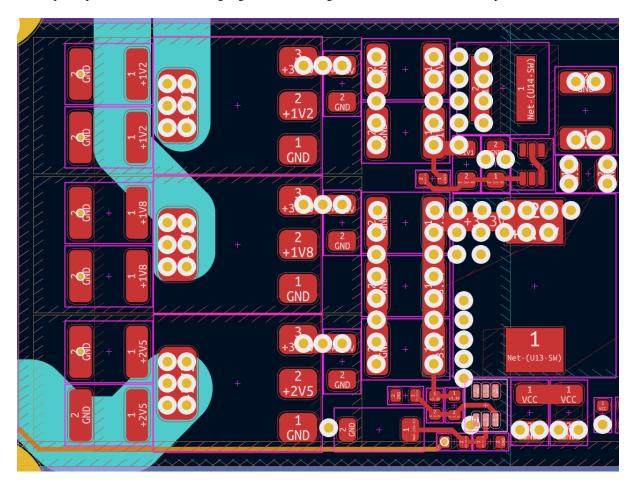

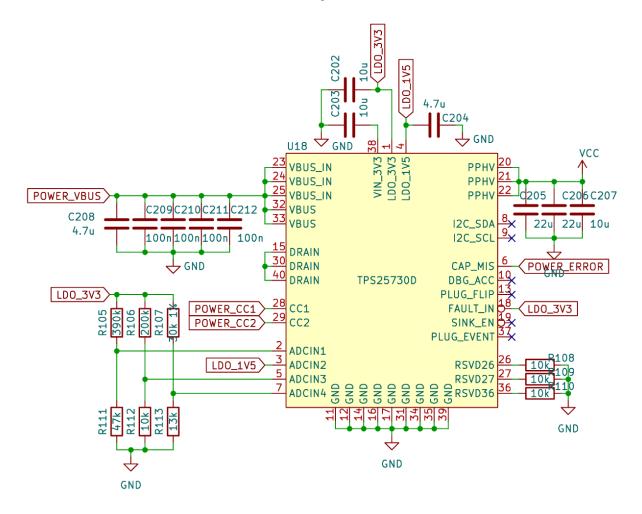

#### 3.4.3 Power Conditioning

A clean power supply is paramount to ensuring a low noise and spur free digitized signal. This is achieved in a two step process. First, both power rails of the ADC are generated for it alone by linear voltage regulators which drastically isolates the ADC from low frequency noise due to the closed-loop nature of linear voltage regulators. Secondly, power to the analog power pins of the ADC passes through ferrite beads which in turn isolates it from high frequency noise and decoupling capacitors are placed on all power pins. The circuit of the power conditioning section after the linear regulators is as shown in figure 34.

Figure 34: Power conditioning circuit for the ADC.

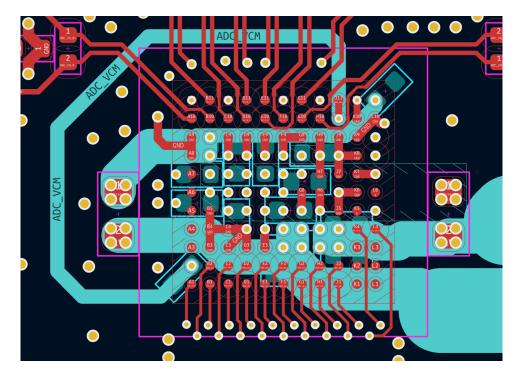

The layout of the ADC's power circuitry is as shown in figure 35. The power rails arrive on the forth layer and connect directly to the digital supply pins as well as to one side of the ferrite beads. After passing through the ferrite beads, the supply rails make their way to the analog supply pins also via the fourth layer. All decoupling capacitors are placed on the back side of the PCB so that their pads can be behind, or as close as possible to the BGA pads ensuring that their path to the pads is as low impedance as possible. This does mean that during manufacturing, an adhesive must be used to keep the capacitor fastened to the board during the reflow soldering process as they will be hanging upside down.

Figure 35: PCB layout of the ADC and its associated power conditioning components.

#### 3.5 FPGA

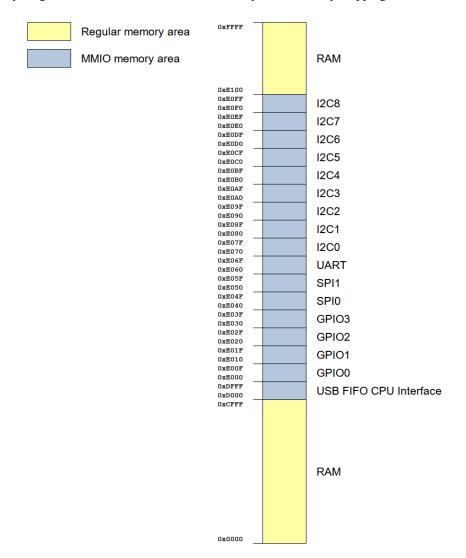

In order to process samples from the ADC and interface with the USB FIFO, some sort of Digital Signal Processor (DSP) is required. In the past, the solution would generally have been to use a specialized DSP chip such as Analog Device's *SHARC*[6], Texas Instrument's *TMS320*[32] or NXP's *VSPA*[20]. Nowadays, with the advent of low-cost, high LUT count FPGAs, such an approach has become obsolete.

Serving as the only processing chip on the receiver is Lattice's *LFE5U-85F*[14], a low cost 85k LUT FPGA. This FPGA was chosen for its extremely low cost and, most importantly, the fact that a Free and Open Source toolchain[27] exists for it. This makes developing designs for this FPGA cheap since no licensing costs are required for the development tools. It is important to note that the 85k LUT variation is likely over-specified, but it was chosen as this is a prototype board and running out of space would have been highly problematic.

#### 3.5.1 Configuration Memory

In order for the FPGA to load its design at startup, an external configuration flash memory is required. Indeed, most FPGAs do not come with non-volatile configuration memory and require either an external flash or a microcontroller to program it after a power interruption or hard reset. In this case, since the microcontroller will be a soft core inside of the FPGA, a configuration flash is chosen.

The FPGA's manual lists the minimum recommended flash sizes for each of the FPGA variants and does not go over 64 Mbit. However, most development boards for this chip, including Lattice's own evaluation board use a 128 Mbit flash chip. As such, since this board is a prototype, it is chosen to also use a 128 Mbit flash chip.

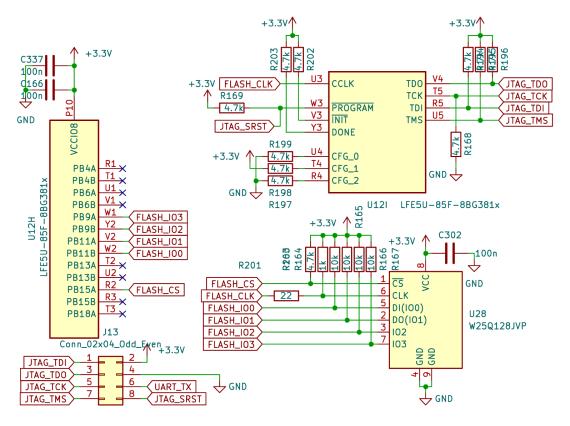

Winbond's W25Q128JVP was chosen as it is one of the most widely used and available SPI flash memory chips for the ECP5 line of FPGAs, being used by Lattice's evaluation board as well as third party development boards such as OneBitSquared's OrangeCrab[22] which was used for early development of the firmware for this project before the PCBs were manufactured. The circuit for the configuration memory is as shown in figure 36.

Figure 36: Circuit of the FPGA configuration memory and JTAG debug port.

The configuration flash chip is directly connected to the FPGA through a QSPI interface. The data and clock lines are all pulled up to ensure they remain in a safe state before the FPGA enters configuration mode where they would

otherwise be floating. The power to the flash chip is as usual decoupled with a 100 nF capacitor.

Next, the configuration pins CFG\_0 through CFG\_2 are tried in such a way to encode 0b010 which sets the FPGA in SPI master mode. This mode is the one that enables the FPGA to talk to an internal flash chip to load its configuration at power on or after a reset. The INIT and DONE pins are unused in SPI master mode and are thus pulled high as per the manufacturer's recommendations.

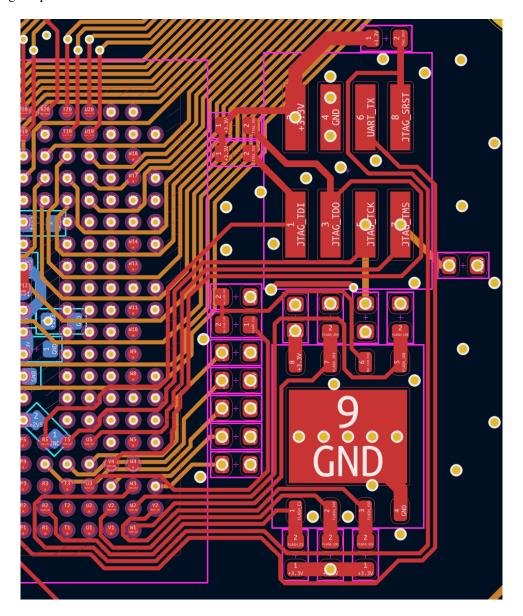

Figure 37: PCB layout of the FPGA configuration memory and JTAG debug port. Layer 1 is represented in red, layer 3 in orange and layer 6 in blue.

As shown in figure 37, the decoupling capacitor of the flash chip is placed immediately in front of its power pin. All the various pull ups and pull downs are placed whereever made sense from a layout perspective as their exact location is not important. All signals are run on the first and third layers.

#### 3.5.2 JTAG Programming and Debugging Port

In order to program the FPGA and flash memory, as well showing debug messages through a UART interface, a JTAG port is added to the PCB. JTAG allows not only to program the FPGA and flash memory but also to probe any IO pin under the package making it useful for testing of PCBs during manufacturing. The circuit of the JTAG port is also shown in figure 36.

The pull ups and pull downs are used to keep the jtag port in a safe state when no debugger is connected. Indeed, TCK is pulled low as a rising edge changes the state of the JTAG state machine and TMS is pulled high because keeping TMS high and clocking the input resets the JTAG state machine. The other pins are pulled high as per the manufacturer's recommendation. Due to how trivial this part of the circuit is, the layout will not be discussed.

#### 3.5.3 The FPGA itself and 1PPS input

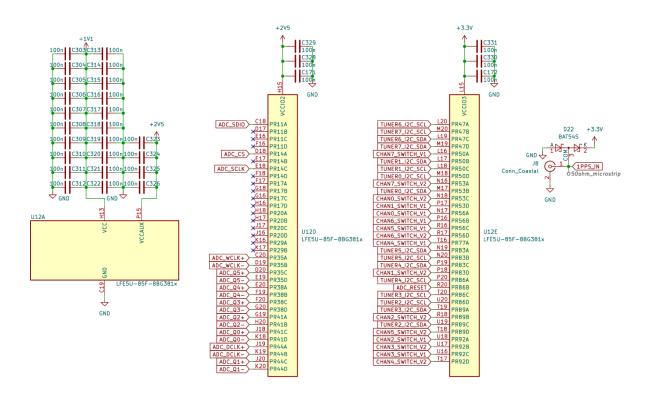

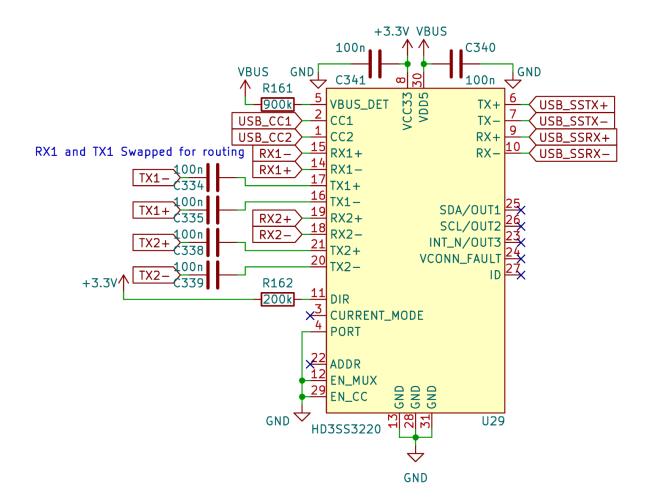

Outside of the configuration memory, the FPGA requires very little external circuitry. As shown in figure 38, all power pins are as usual decoupled using 100 nF capacitors. Additionally, an SMA connector with ESD protection diodes is connected directly to a pin of the FPGA to use as a One Pulse-Per-Second (1PSS) input for GPS time synchronisation of the samples.

Figure 38: Partial circuit of the FPGA section showing the connections to the ADC, tuners and the 1PPS input.