University of Liège - Faculty of Applied Sciences

# Optimization of the AX.25 and D-STAR telecommunications systems of the OUFTI-2 nanosatellite

Graduation Studies conducted for obtaining the Master's degree in "Electrical Engineering" by

François Piron

Academic year 2018-2019

University of Liège - Faculty of Applied Sciences - Electrical Engineering

# Optimization of the AX.25 and D-STAR telecommunications systems of the OUFTI-2 nanosatellite

#### François Piron

Supervisor: Jean-Michel Redouté Academic year 2018-2019

#### Abstract

This work focuses on the development of the telecommunication systems of the OUFTI-2 educational CubeSat, based on its predecessor OUFTI-1. Both satellites embed 3 communication channels: control by the ground station with the AX.25 protocol, a repeater for the digital amateur radio D-STAR protocol (its primary payload) and a continuously emitting beacon.

The AX.25 uplink presented a known (but so far unsolved) issue in OUFTI-1. The On-Board Computer (OBC), which handles the packets, had no external way to detect their presence, and was thus interrupted 9600 times per second to decode the incoming data and look for a valid frame. The Sync Word Detection (SWD) feature of the ADF7021 transceiver could not be used because of a random scrambling process in the protocol. However, it is observed to actually be predictable and therefore the SWD mechanism can notify the OBC upon receiving a packet. The fix is then tested with a similar power level to what the ADF7021 will experience in space.

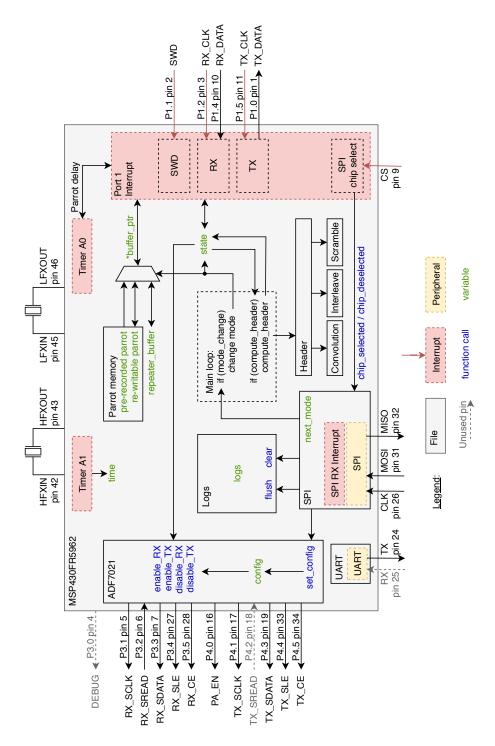

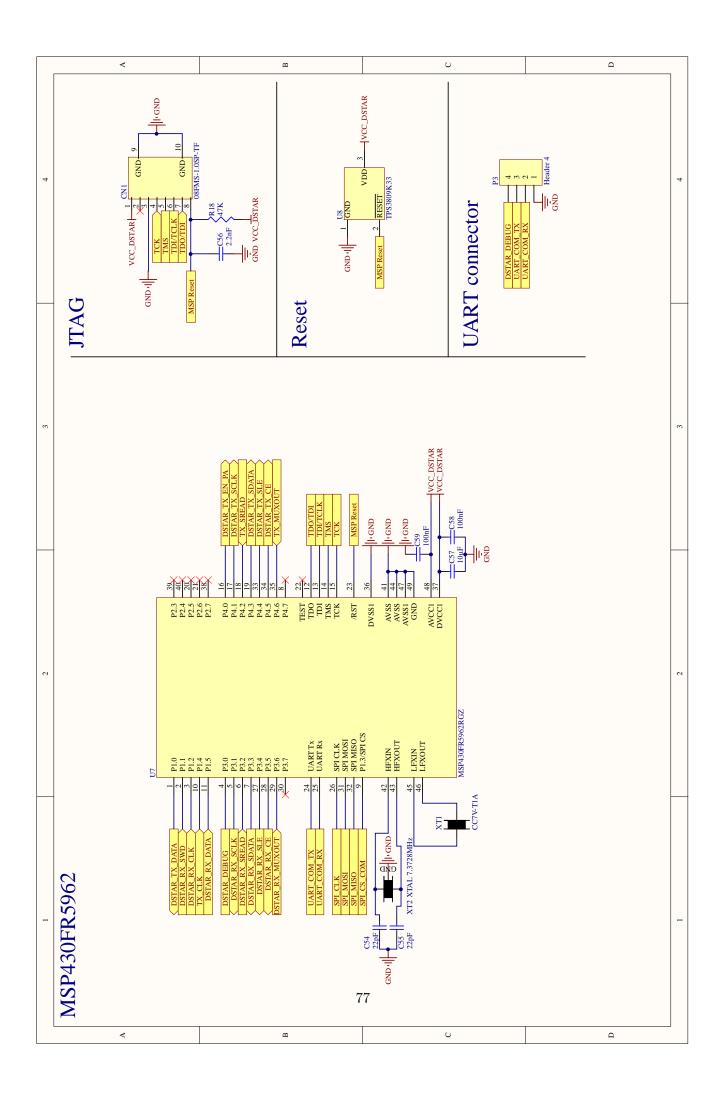

The D-STAR relay is implemented on a separate microcontroller. Due to the extent of the required modifications and the microcontroller model change for the FRAM-equipped MSP430FR5962, its source code was entirely rewritten during this work. New features were added, such as a logging system, and the parrot mode, allowing to transmit pre-recorded D-STAR messages stored in memory on command.

The modified telecommunications systems were thoroughly tested on their own, but further work will still have to test these at space-like RF power levels, and validate their interactions with the other subsystems, before OUFTI-2 can be put in orbit.

Université de Liège - Faculté des Sciences Appliquées - Ingénieur Civil Electricien

# Optimisation des systèmes de télécommunication AX.25 et D-STAR du nanosatellite OUFTI-2

#### François Piron

Promoteur : Jean-Michel Redouté Année académique 2018-2019

#### Résumé

Ce travail porte sur le développement des systèmes de télécommunication du CubeSat éducatif OUFTI-2, basé sur son prédécesseur OUFTI-1. Les deux satellites intègrent 3 canaux de communication : le contrôle par la station au sol avec le protocole AX.25, un répéteur pour le protocole radioamateur numérique D-STAR (sa charge utile principale) et une balise émettant en continu.

La liaison montante AX.25 présentait un problème connu (mais non résolu) dans OUFTI-1. L'ordinateur de bord (OBC), qui traite les packets, n'avait aucun moyen externe de détecter leur présence et était donc interrompu 9600 fois par seconde pour décoder les données entrantes et y chercher une trame valide. La fonction de détection de séquence (SWD) du (dé)modulateur ADF7021 ne pouvait pas être utilisée en raison d'un mélange aléatoire dans le protocole. Cependant, il est observé qu'il est en fait prévisible et, par conséquent, le mécanisme SWD peut notifier l'OBC à la réception d'un paquet. Le correctif est ensuite testé à un niveau de puissance similaire à celui que l'ADF7021 rencontrera dans l'espace.

Le relais D-STAR est implémenté sur un microcontrôleur séparé. Au vu de l'étendue des modifications nécessaires et du changement de modèle de microcontrôleur pour le MSP430FR5962 avec FRAM, son code source a entièrement réécrit dans ce travail. De nouvelles fonctionnalités a été ajoutées, telles qu'un système de journal et le mode perroquet, permettant de transmettre sur commande des messages D-STAR préenregistrés stockés en mémoire.

Les systèmes de télécommunication modifiés sont testés, mais il faudra encore le faire à des niveaux de puissance RF similaires à ceux de l'espace et valider leurs interactions avec les autres sous-systèmes avant de pouvoir mettre OUFTI-2 en orbite.

## Acknowledgements

I would like to thank Prof. J.-M. Redouté for his follow up and enthusiasm for this project. I am also grateful to V. Broun for his valuable advice, and the ISIL laboratories that he made available for us to work in ideal conditions. I want to thank X. Werner as well for his help during the first half of this thesis, and Prof. J. Verly and S. De Dijcker for their interest in my work and useful remarks.

I thank my OUFTI-2 teammates François Grosjean (ULiège), Florian Radelet (ULiège), David La (ULiège), Soulaimane Harika (ULiège) and Guillaume Martin (INPRES) for our collaboration and the good atmosphere in the lab. Thank you to all the previous students that worked on OUFTI-1 and OUFTI-2 whose work I benefited. Thank you to my promotion mates and everyone I worked with and learned from during these studies.

I also want to thank my godfather Stéphane, Joachim and Samy for their proofreadings and suggestions, Robin, Gaël and Loïc for our library sessions (and breaks), Lucas, Gaëtan and Gilles. Thank you to my family for their support, my grandfather and grandmother, my godmother, Léon and Jean-Christophe. Finally, I would like to thank my mom and dad, to whom I owe everything, and who, I hope, would be proud of me.

# Contents

| 1 | Intr | oducti                                |                                        |  |          | 1               |  |  |  |  |  |  |  |

|---|------|---------------------------------------|----------------------------------------|--|----------|-----------------|--|--|--|--|--|--|--|

|   | 1.1  | OUFT                                  | ΓI-2 details                           |  |          | 3               |  |  |  |  |  |  |  |

|   | 1.2  | Comm                                  | nunications                            |  |          | 4               |  |  |  |  |  |  |  |

|   | 1.3  | Goals                                 | of this work                           |  |          | 5               |  |  |  |  |  |  |  |

|   | 1.4  | Activi                                | ities                                  |  |          | 6               |  |  |  |  |  |  |  |

| 2 | AX   | X.25 synchronization 7                |                                        |  |          |                 |  |  |  |  |  |  |  |

|   | 2.1  | Descri                                | iption of the issue                    |  |          | 7               |  |  |  |  |  |  |  |

|   |      | 2.1.1                                 | AX.25 protocol                         |  |          | 7               |  |  |  |  |  |  |  |

|   |      | 2.1.2                                 | Uplink chain                           |  |          | 9               |  |  |  |  |  |  |  |

|   |      | 2.1.3                                 | G3RUH modem                            |  |          | 14              |  |  |  |  |  |  |  |

|   |      | 2.1.4                                 | The scrambled SWD issue                |  |          | 16              |  |  |  |  |  |  |  |

|   | 2.2  | Consid                                | dered potential solutions              |  |          | 16              |  |  |  |  |  |  |  |

|   | 2.3  | Obser                                 | vations and solution                   |  |          | 18              |  |  |  |  |  |  |  |

|   |      | 2.3.1                                 | Sampling                               |  |          | 18              |  |  |  |  |  |  |  |

|   |      | 2.3.2                                 | Decoding                               |  |          | 21              |  |  |  |  |  |  |  |

|   |      | 2.3.3                                 | Shift register value                   |  |          | 21              |  |  |  |  |  |  |  |

|   |      | 2.3.4                                 | Test of the solution                   |  |          | 23              |  |  |  |  |  |  |  |

|   | 2.4  | Valida                                | ation                                  |  |          | 25              |  |  |  |  |  |  |  |

|   |      | 2.4.1                                 | RSSI measurement                       |  |          | 26              |  |  |  |  |  |  |  |

|   |      | 2.4.2                                 | Sync Word Detection rate test setup    |  |          | 26              |  |  |  |  |  |  |  |

|   |      | 2.4.3                                 | Bit Error Rate hypothesis verification |  |          | 32              |  |  |  |  |  |  |  |

|   |      | 2.4.4                                 | Conclusion                             |  |          | 34              |  |  |  |  |  |  |  |

| 3 | D-S  | TAR 1                                 | relav                                  |  |          | 35              |  |  |  |  |  |  |  |

| Ū | 3.1  |                                       | AR                                     |  |          | 35              |  |  |  |  |  |  |  |

|   | 0.1  | 3.1.1                                 | D-STAR header                          |  |          | 37              |  |  |  |  |  |  |  |

|   | 3.2  | -                                     | fications                              |  |          | 38              |  |  |  |  |  |  |  |

|   | 3.3  | -                                     | controller selection                   |  |          | 39              |  |  |  |  |  |  |  |

|   | 3.4  |                                       |                                        |  |          |                 |  |  |  |  |  |  |  |

|   | 3.5  |                                       |                                        |  |          |                 |  |  |  |  |  |  |  |

|   | 3.6  | •                                     | t mode                                 |  |          | 43<br>46        |  |  |  |  |  |  |  |

|   | 3.7  |                                       |                                        |  |          |                 |  |  |  |  |  |  |  |

|   | 3.8  | , , , , , , , , , , , , , , , , , , , |                                        |  |          |                 |  |  |  |  |  |  |  |

|   | 3.0  | Acknowledgement and CRC               |                                        |  | 50<br>52 |                 |  |  |  |  |  |  |  |

|   |      | 3.8.1 $3.8.2$                         | ADF7021 configuration                  |  |          | $\frac{52}{52}$ |  |  |  |  |  |  |  |

|   |      | 3.8.3                                 | Logs                                   |  |          | $\frac{52}{53}$ |  |  |  |  |  |  |  |

|   |      | 3.8.4                                 | Parrot dump command                    |  |          |                 |  |  |  |  |  |  |  |

|   |      | 0.0.4                                 |                                        |  |          | ()()            |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Communications circuit schematics                    | 70 |

|--------------|------------------------------------------------------|----|

| 4            | Conclusion                                           | 69 |

|              | 3.12 Conclusion                                      | 68 |

|              | 3.11 Communications circuit board                    |    |

|              | 3.10.4 SPI communications with the On-Board Computer | 64 |

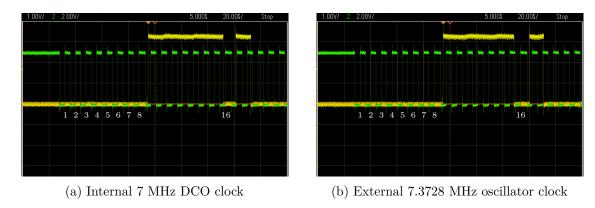

|              | 3.10.3 Clock tests                                   | 63 |

|              | 3.10.2 Test setup                                    | 60 |

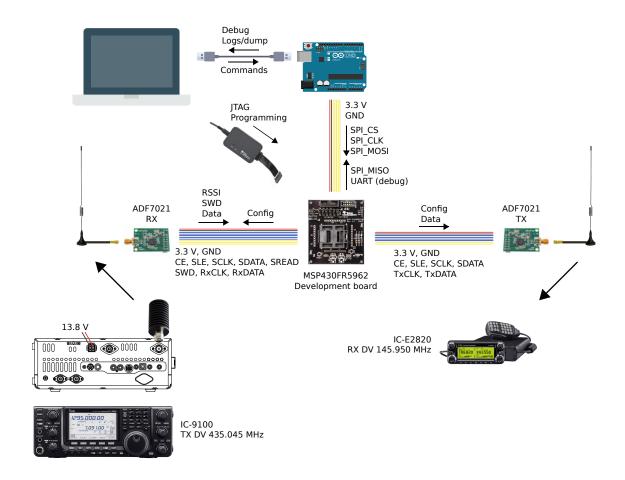

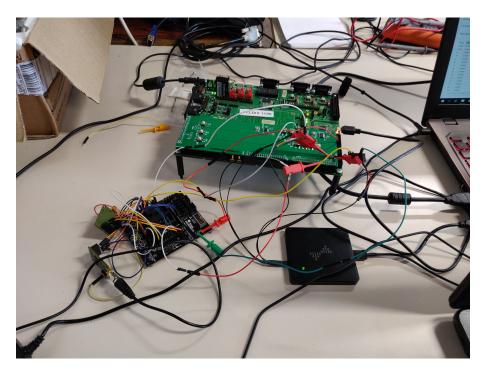

|              | 3.10.1 Compilation and programming                   | 60 |

|              | 3.10 Tests                                           | 60 |

|              | 3.9 Arduino debug tool                               | 57 |

## Acronyms

**ACK** Acknowledgement

AX.25 Amateur X.25 protocol

BCN Beacon subsystem

**BER** Bit Error Rate

COMM Communications subsystem

CRC Cyclic Redundancy Check

D-STAR Digital Smart Technologies for Amateur Radio protocol

**DV** Digital Voice D-STAR mode

FCS Frame Check Sequence

FRAM Ferroelectric Random Access Memory FSK Frequency Shift Keying modulation

GMSK Gaussian Minimum-Shift Keying modulation

**LNA** Low-Noise Amplifier

MUX Multiplexer

**OBC** On-Board Computer

**OUFTI** Orbital Utility For Telecommunication Innovations

PA Power Amplifier

PCB Printed Circuit BoardPLL Phase-Locked LoopRF Radio Frequency

**RSSI** Received Signal Strength Indication

RX Receive

SPI Serial Peripheral Interface protocolSWD Sync Word Detect ADF7021 feature

TNC Terminal Node Controller

TX Transmit

UART Universal Asynchronous Receiver Transmitter protocol

UHF Ultra High Frequency, between 300 MHz and 3 GHz

VHF Very High Frequency, between 30 MHz and 300 MHz

## Chapter 1

## Introduction

OUFTI-2 is an educational CubeSat mainly developed by students from the University of Liège and the Haute Ecole de la Province de Liège (ISIL and INPRES). The project started in 2016 after the launch of its predecessor OUFTI-1.

A CubeSat is a nanosatellite<sup>1</sup> of dimensions  $10 \text{ cm} \times 10 \text{ cm} \times 10 \text{ cm}$ , weighing around 1 kg and consuming around 1 W. It was developed in 1999 as a specification for educational satellites, by the *California Polytechnic State University* and *Stanford University*. They are usually launched either in batch by CubeSats deployment modules installed alongside bigger satellites in a launcher rocket, or from the International Space Station (ISS). More than 1000 CubeSats have been launched to this day [1].

OUFTI-2 embeds 3 payloads [2]. The main one is a repeater for the amateur radio protocol D-STAR. The second one (RAD) is a test board for new kind of multilayer electronics-shielding material. The last one (IMU) is an inertial measurement unit designed by high-school students.

The development of OUFTI-1 started in 2007. Tens of students took part in its design, implementation and tests, yielding more than 40 Master's theses. Its payloads were a D-STAR repeater like OUFTI-2 and high-efficiency solar panels from *Azur Space* [3]. It was launched in 2016 aboard the Soyuz VS14 launcher, with the 2 other CubeSats of ESA's² Fly Your Satellite program. For undetermined reasons, OUFTI-1 became silent after 12 days in orbit.

<sup>&</sup>lt;sup>1</sup>Satellite with a mass between 1 and 10 kg

<sup>&</sup>lt;sup>2</sup>European Space Agency

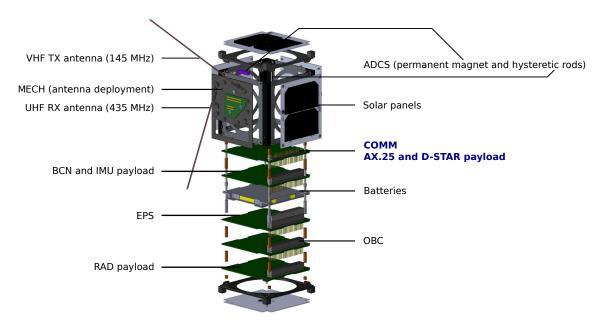

Figure 1.1 – OUFTI-2 CAD model exploded view (the antennas are truncated)

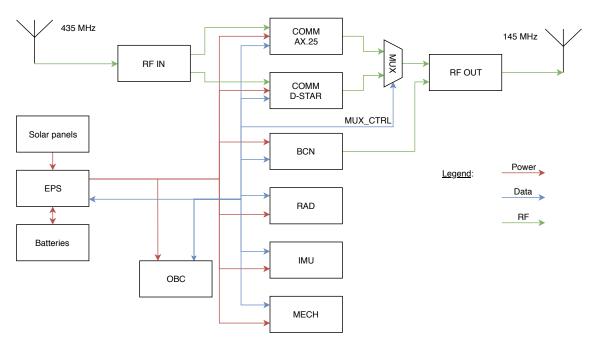

Figure 1.2 – Simplified overview of the interactions between the different subsystems

#### 1.1 OUFTI-2 details

The different subsystems making up OUFTI-2, presented in Figures 1.1 and 1.2 are [4]:

- **COMM** This subsystem includes the AX.25 and D-STAR transceivers, their associated circuits, all the other required RF components (amplifiers, filters, ...), as well as the D-STAR relay microcontroller.

- **OBC** The core or the nanosatellite is its On-Board Computer (OBC). It controls all the other subsystems, communicates with the ground station through AX.25 telecommands and telemetries, schedules received orders execution and logs the important events and measurements of the satellite.

- For OUFTI-2, the OBC is based on a new experimental 3 core controller provided by *Thales Aliena Space*, with a high resistance to radiations, a large temperature range  $(-55 +125 \, ^{\circ}\text{C})$  and embedded RAM error correction and detection. The software is currently being entirely rewritten. Unlike OUFTI-1, it will not use a Real-Time Operating System (RTOS) anymore and there will not be any backup OBC.

- BCN The beacon continuously transmits measurements and information about the state of the satellite. The beacon is as independent from the rest of the satellite as possible. Its goal is to be able to collect some data even if other subsystems fail. Its Morse transmissions can be decoded by amateur radio operators listening from all around the world, which can pick up the satellite signal even when it would be impossible from Liège. It also transmits the same data at high speed (2400 bits/s) for machine decoding.

- **EPS** The Electrical Power Supply tracks the maximum power point from the solar panels, handles the charge and discharge of the batteries, and provides 3.3 V and 5 V power buses to the rest of the satellite.

- **RAD** This payload embeds 3 identical circuits, respectively with a new kind of multilayer electronics-shielding material, a conventional shielding and no shielding at all. It will measure and compare the degradation of the components due to radiation [5].

- **IMU** This payload, designed by Belgian high-school students, will perform magnetic and inertial measurements in order to determine the attitude of the satellite.

- **ADCS** This Attitude Determination and Control System is a passive way of controlling the orientation of satellite, and try to keep it stable relative to Earth. This is necessary to optimize RF communications and make sure all solar panels have similar exposure to the sun.

- **MECH** The mechanical subsystems handles the releasing of the antennas when the appropriate signal is sent by the OBC, 30 minutes after the launch of the satellite in orbit.

- STRU, THER and VIB Respectively stand for the structure, thermal and vibrations studies and ratings.

#### 1.2 Communications

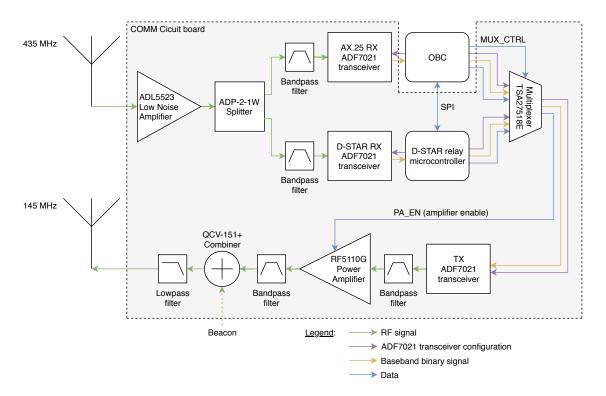

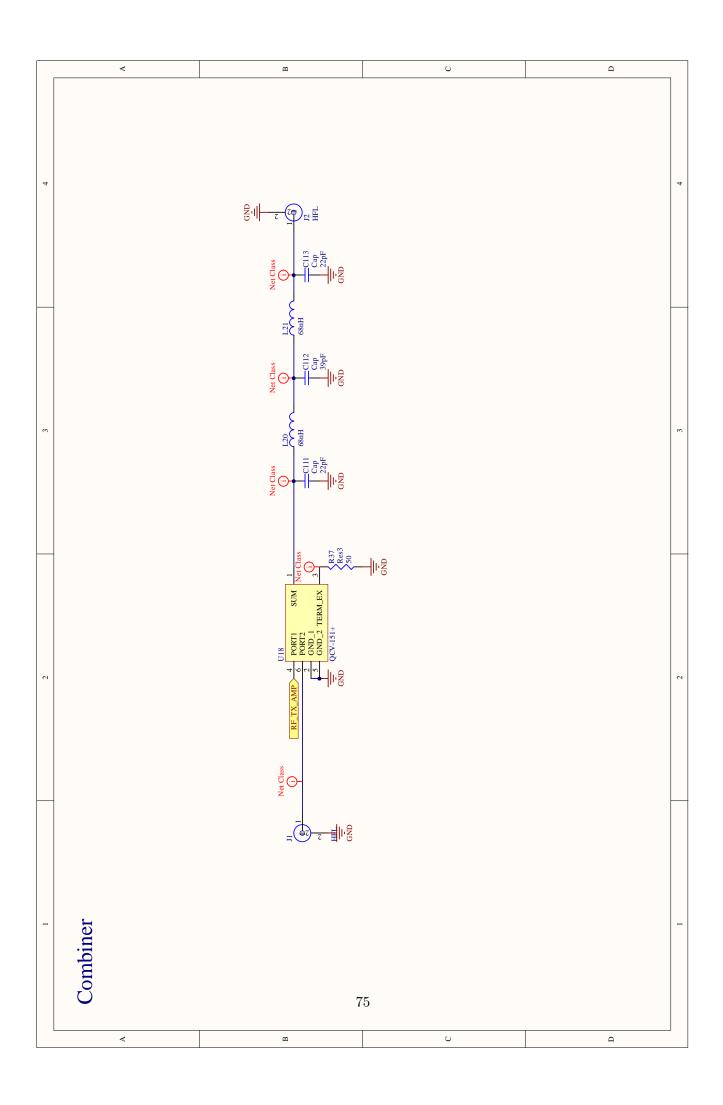

Figure 1.3 – Communication signals flow path. Impedance matching is not shown for clarity reasons

The radio communications of the satellite are divided in 3 channels:

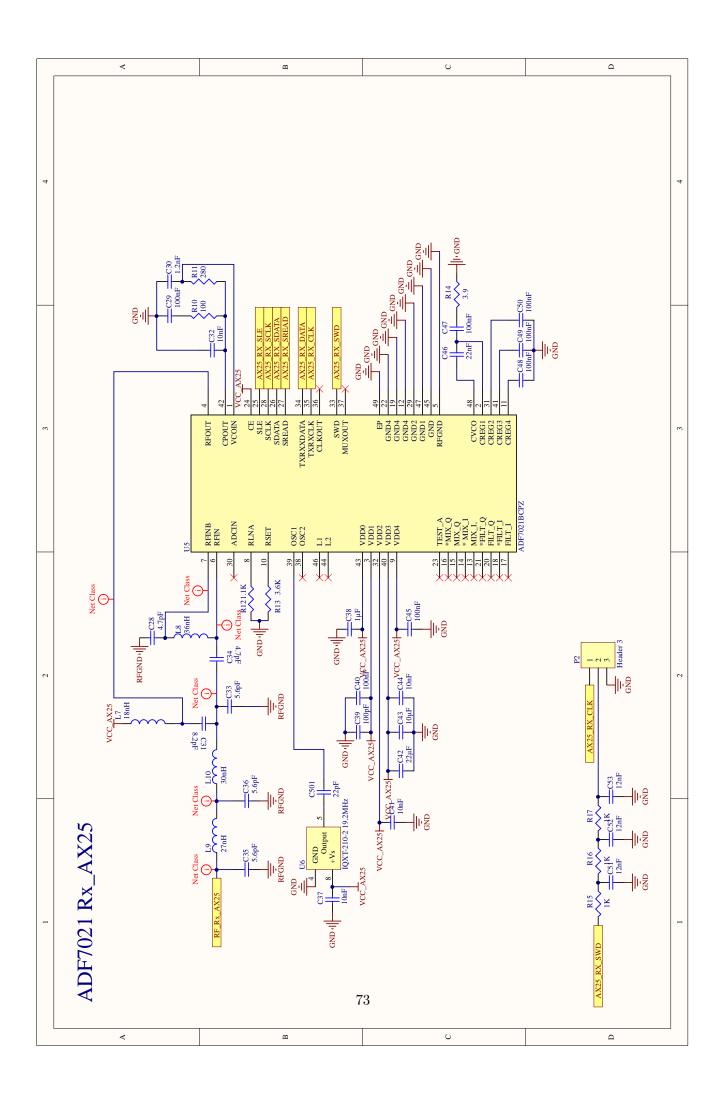

- The AX.25 channel, used to control the satellite from the ground station and retrieve the on-board measurements, with uplink at 435.015 MHz and downlink at 145.950 MHz, modulated in 2-FSK at 9600 bits/s with a bandwidth of 9.6 kHz. It is entirely controlled by the On-Board Computer. The ground to satellite link will be developed in depth in Chapter 2.

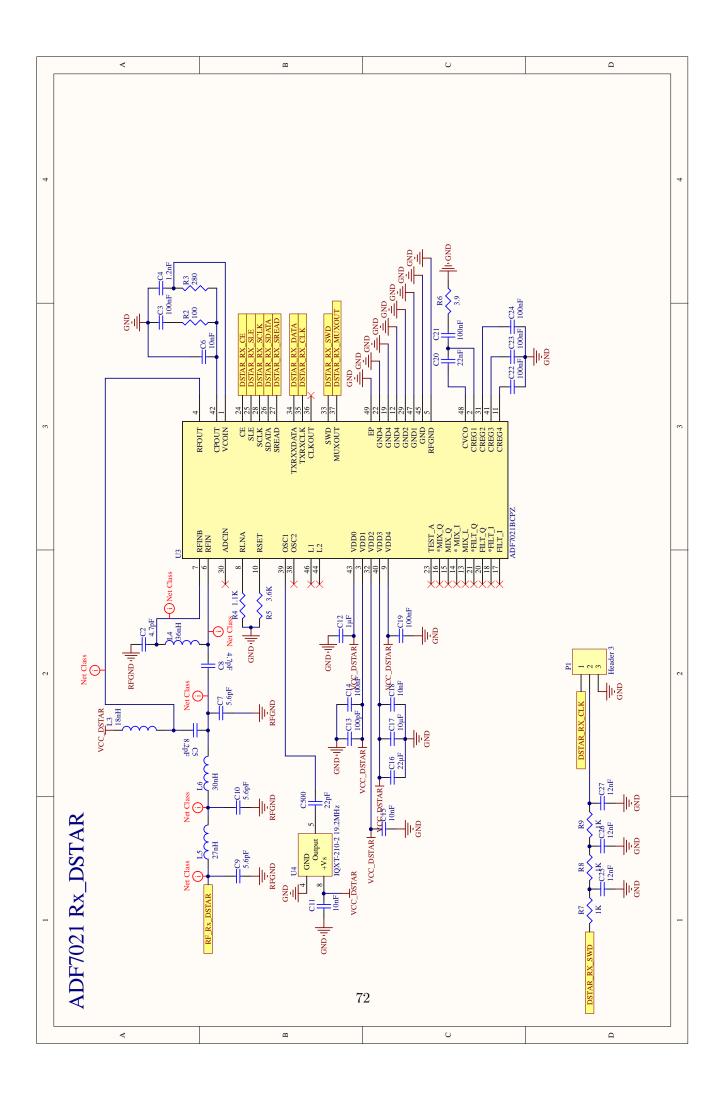

- The D-STAR amateur radio channel, repeating from 435.045 MHz to 145.950 MHz, modulated in GMSK at 4800 bits/s with a bandwidth of 6 kHz. It is handled by the COMM microcontroller, which is the subject of Chapter 3.

- The beacon, continuously emitting measurements in OOK/Morse code at 12 words per minute, as well as 2400 bits/s, at 145.876 MHz.

Their interactions and the RF components of the COMM subsystem are shown in Figure 1.3.

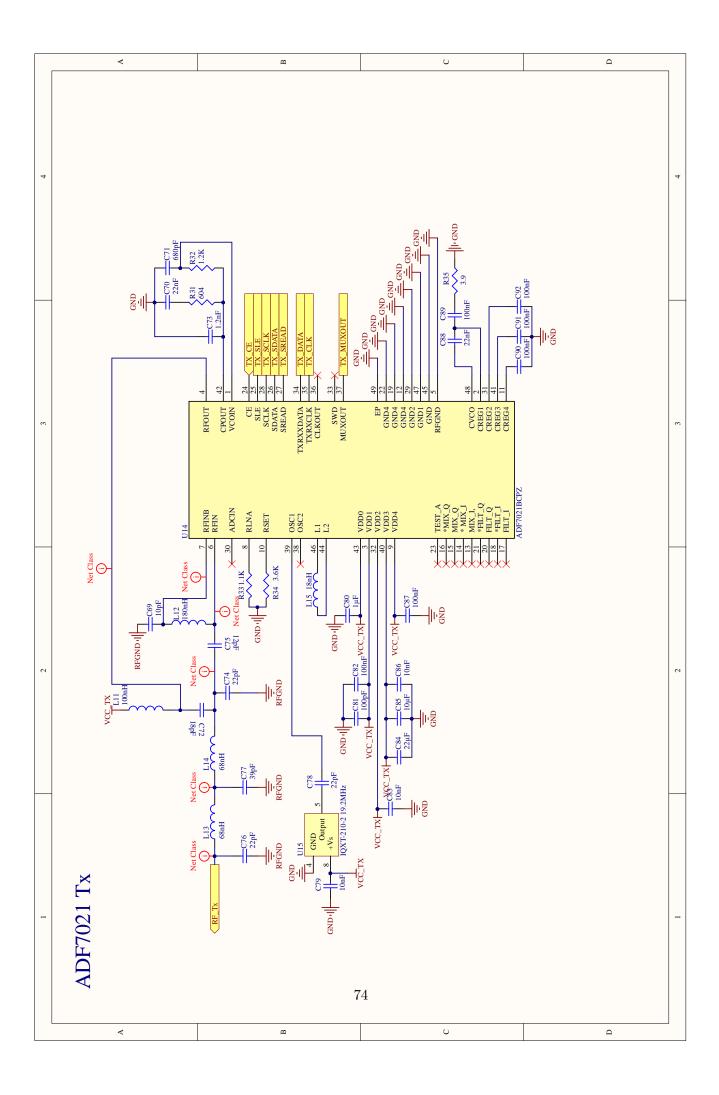

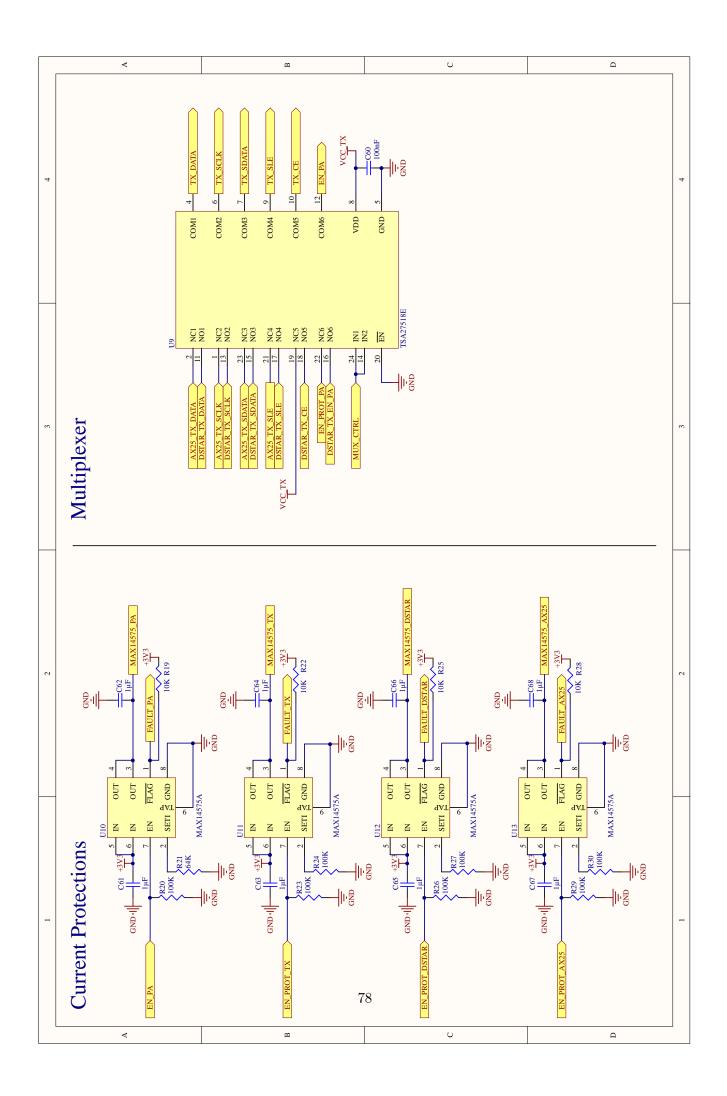

This work will focus on the AX.25 and D-STAR communications, which are handled by 3 ADF7021 transceivers on the satellite. The 2 channels have separate reception (RX) ADF7021s, and share the same transmission (TX) ADF7021. The reason for the RX separation is that when the D-STAR repeater is active, the OBC **must** still be able to receive commands. It is required by law that the satellite transmissions can be shut down at any time when ordered [6]. On the other hand, AX.25 and D-STAR transmissions are using the same ADF7021.

The OBC decides which of the D-STAR repeater or itself has control over the TX ADF7021 through a digital multiplexer. Each time it switches, the TX ADF7021 is reconfigured either for AX.25 by the OBC or for D-STAR by the D-STAR microcontroller. As the enabling of the D-STAR circuit is also controlled by the OBC, this multiplexing process is effectively transparent for the D-STAR relay. When powered on, it always has control over the TX ADF7021. If the OBC needs to transmit while the D-STAR relay is active, it will shut it down and take control of the TX ADF7021 first.

The ADF7021 is a digital transceiver working from 80 MHz to 650 MHz and 862 MHz to 950 MHz [7]. It supports multiple FSK modulation configurations and filtering options, data rates up to 32.8 kHz and many other features and settings. It can be configured through the modification of 15 registers, 4 bytes long each. The communication channel for setting these registers is a simple 4-wires serial bus, with a protocol very similar to SPI (SLE = Load Enable = Chip Select, SCLK = Clock, SDATA = MOSI, SREAD = MISO) for which the ADF7021 would be the slave. The TX or RX data is transferred on 2 wires (TxRxCLK, TxRxDATA), whose clock is given by the ADF7021. Some of its specific features that are useful for OUFTI-2 will be explained later when appropriate.

The beacon emits in parallel with the other subsystems. Its RF signal is combined with the amplified output of the TX ADF7021 before going into the antenna.

#### 1.3 Goals of this work

The aim of this work is to optimize some specific points and finalize the communications part of OUFTI-2, based on what has already been done for OUFTI-1. The first part is of course to familiarize with OUFTI-1, OUFTI-2 and their telecommunications systems, study previous work, their components and protocols. The two main tasks are then the following:

- Chapter 2: Fix a known AX.25 synchronization issue. The incoming telecommand packets could not be detected by the OBC, which forced it to continuously listen on the channel to check for the reception of valid data. The OBC was thus interrupted 9600 times per second, most of the times for nothing.

- Chapter 3: Re-develop the D-STAR repeater microcontroller code in a robust and reliable manner, and add a few features. The main addition is a "parrot" mode, which consists in the transmission of pre-recorded D-STAR frames.

Before this work, the state of the COMM subsystem was the following:

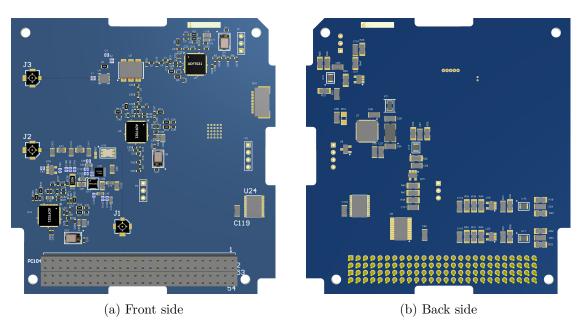

- The required hardware modifications had already been performed. The COMM board schematics only needed some small corrections and there was already a partial PCB layout.

- The D-STAR microcontroller software had not been touched since OUFTI-1. Given the extent of the required changes, it had to be rewritten from the ground up.

- The ADF7021 configurations could be kept as the carrier frequencies and RF parameters for the AX.25 and D-STAR channels are the same as OUFTI-1.

- The ground station hardware (radios, TNC) of OUFTI-1 can be kept as well. The software will need to be adapted for the new AX.25 command set.

Fixing the AX.25 synchronization issue could have implied changes to the ground or satellite hardware, depending on the solution implementation. It was not necessary though, as the fix only requires changes to the ADF7021 configuration and thus the OBC software.

#### 1.4 Activities

I took part in the following activities during this academic year:

- Visit of the CSL (Centre Spatial de Liège / Liège Space Center) on October 19<sup>th</sup>, 2018. Discussion with some employees followed by a visit of their clean room.

- Amateur radio HAREC exam passed on December 19<sup>th</sup>, 2018. The HAREC license is mandatory to use the radio equipment on the frequencies of this project. My callsign is ON9PF.

- Lecture on space radiations by Mr. Carapelle from CSL on April 4<sup>th</sup>, 2019.

## Chapter 2

## AX.25 synchronization

#### 2.1 Description of the issue

As previously explained, there are 3 telecommunication channels in OUFTI-2. Each of them has a different purpose and is managed by a different part of the nanosatellite. One of them is the AX.25 channel, which allows for the remote control of the On-Board Computer (OBC), the brain of the satellite, from the ground station. Uplink AX.25 packets are called telecommands, and downlink ones are called telemetries. The OBC only transmits telemetries as a response to a telecommand.

In OUFTI-1, the On-Board Computer was constantly listening on the AX.25 channel, waiting to receive a command. In other words, it was constantly interrupted 9600 times per second to read an incoming bit, even when no packet was sent. This was a significant loss of processor time and power.

A much wiser approach would be to have some kind of external signal, notifying the OBC when a packet is detected. That way, it could listen on the channel only when necessary. It just so happens that a Sync Word Detect (SWD) mechanism is present in the ADF7021 transceiver, which is used both in OUFTI-1 and its successor. It could very well solve this issue, but it was not be used in OUFTI-1 due to a scrambling in the modem protocol [8]. The details of this SWD, the reasons why it could not be used and the solution are described in the following sections.

#### 2.1.1 AX.25 protocol

AX.25 is an amateur radio protocol for the data link layer (layer 2 of the OSI model), derived from X.25. It was initially developed to allow amateurs to send data packets using regular radios. Devices that allow AX.25 communications are typically called Terminal Node Controllers (TNC). The main features of AX.25 are [9]:

- Synchronization flags 0x7E, bit stuffing to avoid having flags inside the packet

- Persistent connection or packet transmission

- Source and destination addressing, with variable addresses length, multiple repeaters and basic routing capabilities

- Control packets: acknowledgement, ready, reject packet, ... possibly leading to retransmission

- Different possible frame types: Supervisory (control), Information (data with sequence numbers), Unnumbered (data without sequence number)

- Frame Check Sequence (FCS)

- Multiple protocols running on top of AX.25, using Protocol Identifier field (PID)

The AX.25 specification does not impose any physical layer (layer 1 of the OSI model) protocol or modulation. However, it is most of the times frequency modulated and transmitted in the amateur radio frequency bands available between 30 MHz and 3 GHz.

Any additional layers or application can be used on top of AX.25. Some common use cases are:

- Direct communication between 2 radio amateurs, without additional encapsulation

- Internet Protocol (IP) tunneling

- Automatic Packet Reporting Systems (APRS), usually to send GPS location at regular intervals. Often used in mobile vehicles like cars and boats. Can also transmit other information: status, weather, telemetries, ...

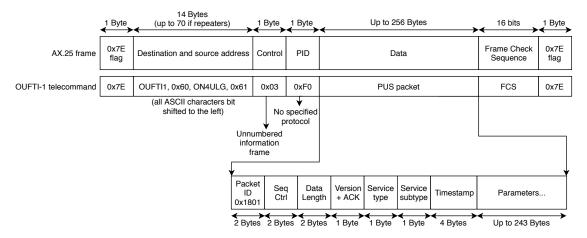

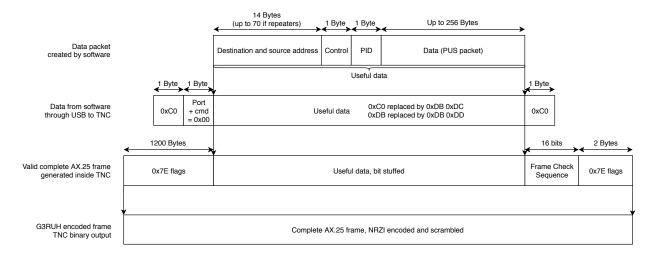

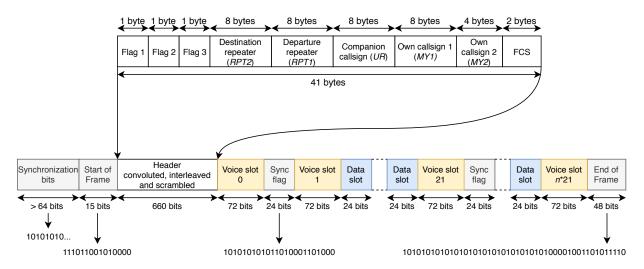

For OUFTI-1 and OUFTI-2, only the UI frame type is used (Unnumbered Information). Data inside AX.25 frames is encoded following the Telemetry and telecommand Packet Utilization Standard (PUS). It specifies the format for additional information, such as the service type, a timestamp, ... The exact format is not important for this work so it will not be detailed further. The address, control and PID fields are fixed. The AX.25 UI frame structure is shown in Figure 2.1.

Figure 2.1 – Structure of the AX.25 Unnumbered Information frame in the case of OUFTI-1 and OUFTI-2 [8–11]

The FCS is a Cyclic Redundancy Check computed with the following 16 bits CCITT polynomial:

$$x^{16} + x^{12} + x^5 + 1$$

AX.25 bytes are sent Least Significant Bit (LSB) first, except for the Frame Check Sequence (FCS) which is sent MSB first.

#### Bit Stuffing

The 0x7E flag serves as a synchronization pattern. It helps the receiver Phased Lock Loop (PLL) to synchronize its output with the incoming data. But it also acts as a Start Of Frame and End Of Frame delimiter. Therefore, it is important that it is not accidentally present inside the AX.25 packet itself. To avoid that, after every sequence of 5 '1's, an extra '0' is added. As the flag consists of 6 consecutive '1's, it is ensured to be the End Of Frame when came across. The reverse process is performed on the receiver side.

#### 2.1.2 Uplink chain

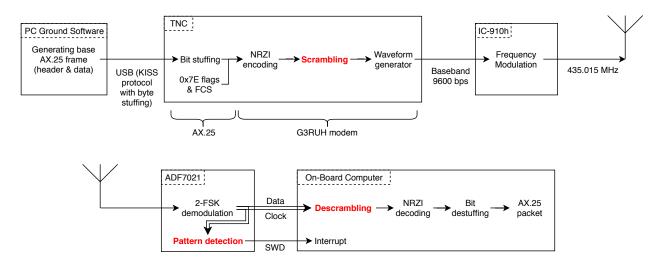

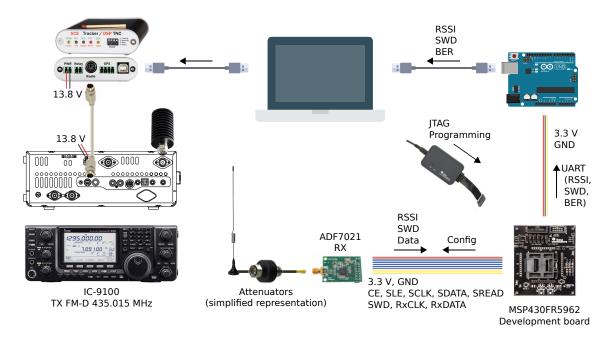

Before tackling the specific synchronization issue, it is important to understand all the elements that make up the ground-to-satellite link. The complete data flow chain is shown in Figure 2.2. Each of the elements are described in details below.

Figure 2.2 – Complete AX.25 uplink data flow (filters, amplifiers etc have been omitted for simplicity)

#### Computer

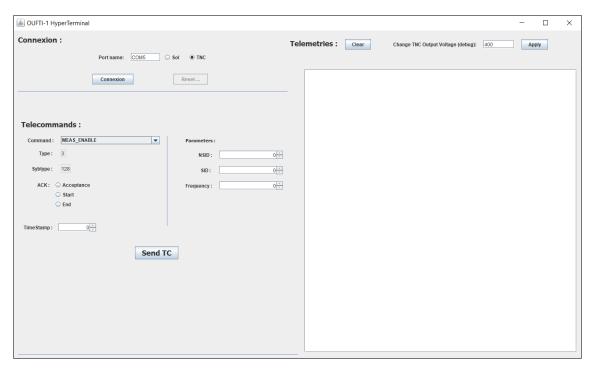

First, the useful data frame is created on a computer. A custom software has been developed to automate the creation of a valid packet [12]. It contains a Graphical User Interface (GUI), shown in Figure 2.3, on which the user can specify the type and parameters of the desired command. When the user presses the "Send TC" button, the software makes the appropriate bit sequence and sends it through a USB port to the TNC. The configuration of the TNC is also determined and sent by the software.

For OUFTI-2, a very similar software is developed to accommodate for the new telecommands and telemetries. The communications with the TNC are identical.

Figure 2.3 – OUFTI-1 AX.25 ground software

#### TNC

A Terminal Node Controller (TNC) is a device that does the interface between the digital payload and the transceiver. The goal is to use a traditional analog radio to transmit digital information. It wraps the data inside an AX.25 packet and encodes it following a configurable operating mode. It then transmits the packet at a selectable baudrate and baseband modulation (On-Off Keying OOK, Audio Frequency Shift Keying AFSK, ...).

Some TNCs are also able to transmit APRS/GPS information, as explained in 2.1.1.

Figure 2.4 – Picture of the SCS DSP TNC. Image source: [13]

The TNC that was selected is the SCS Tracker / DSP TNC [8], presented in Figure 2.4. It is configured to transmit 9600 bits/s. At that baudrate, its user manual specifies that it will encode the AX.25 frame according to the G3RUH modem [14]. Basically, reversible operations are performed in order to improve the transmission. These are explained in section 2.1.3. The documentation available for this TNC is limited. Although it contains all the information required to configure and use it, it is missing implementation details that were important for this issue. These were obtained through observations, the results of which are presented in 2.3.

The settings, sent by the computer software to the TNC, are listed in Table 2.1.

| Command | Description                         |

|---------|-------------------------------------|

| @D1     | Full duplex mode                    |

| @F1     | Do not send flags during the pause  |

| %B9600  | 9600 baud FSK mode (G3RUH modem)    |

| X1      | Push To Talk (PTT) enabled          |

| %X400   | Output of 400 mV peak-to-peak       |

| T100    | TX delay of 1 second                |

| P128    | Persistence (for CSMA)              |

| W20     | Slot time of 20 ms                  |

| O2      | Maximum of 2 unacknowledged packets |

| R0      | Digipeating disabled                |

| @V0     | Callsign check disabled             |

| @K      | Switch to KISS mode                 |

Table 2.1 – TNC configuration parameters, unchanged from OUFTI-1 [10]

The following communications between the computer and the TNC are performed in "KISS" mode<sup>1</sup>. This format is common for that kind of equipment, so that they can be operated manually through a simple terminal. The frame is wrapped into 0xC0 flags and the "data frame" command (for port 0, as only one port is used) 0x00 is added at the beginning.

<sup>&</sup>lt;sup>1</sup>Keep It Simple, Stupid

Figure 2.5 – Structure of the telecommand AX.25 frame at the different sending stages

All the manipulations performed on the packet are illustrated in Figure 2.5. The TNC outputs the encoded signal to a mini-DIN cable, which is standard for TNC to radio data links. The port 6 pins, see from the radio side, are detailed in Figure 2.6. When transmitting, the Push To Talk pin is grounded and the data is sent on DATA IN. A lot commercial amateur radio transceivers have this kind of connector, that can be selected instead of the traditional audio interfaces.

#### **9** MAIN BAND DATA SOCKET

| DATA Socket | Pin No. | Pin Name    | Description                                                                                                                                         |

|-------------|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 1       | DATA IN     | Input terminal for data (common for both 1200 and 9600 bps)                                                                                         |

|             | 2       | GND         | Ground line for the DATA IN, DATA OUT and AF OUT.                                                                                                   |

| 0-2=-2      | 3       | PTTP        | Transmits when this terminal is grounded.                                                                                                           |

| 3           | 4       | DATA<br>OUT | Received data output terminal for 9600 bps operation.                                                                                               |

| 5           | 5       | AF OUT      | Received data output terminal for 1200 bps operation.                                                                                               |

|             | 6       | SQL         | Output terminal for squelch condition (Open/Close). Outputs grounded level signal when squelch is opened, +8 V level signal when squelch is closed. |

Figure 2.6 – Pinout of the mini-DIN input of the IC-910h radio [15]

#### Radio

The radios used are ICOM's IC-910h and IC-9100, shown respectively in Figures 2.7 and 2.8. These amateur radio transceivers can handle AM, FM, SSB, CW and RTTY in the 144 MHz, 430 MHz and optional 1200 MHz bands [15, 16].

To send AX.25 telecommands to the satellite, the transceiver must be configured at 435.015 MHz, in FM data mode (FM-N on the IC-910h, FM-D on the IC-9100). The 9600 bps option must also be selected. Even though it is in data mode, the radio does not really expect binary data. Just like the regular FM mode, the input signal is used to directly modulate the frequency. The only effects of these 2 options (data mode and 9600 bps) are

the input/output port selection, and some differences in the filters and amplifiers to optimize that kind of communications [15–17]. The RF output power level of the transceiver must also be appropriately tuned.

The IC-9100 carrier frequency can be tuned down to 10 Hz steps, which allows for precise Doppler effect compensation when communicating with a satellite. Both transceivers contains a satellite mode to easily control the carrier frequency correction. There exists various computer programs that can compute the position, relative velocity and subsequently Doppler effect of any given satellite.

Figure 2.7 – IC-910h radio. Image source: [18]

Figure 2.8 – IC-9100 radio. Image source: [18]

The output of the transceiver is then connected to a power amplifier and finally to the antenna.

#### **ADF7021**

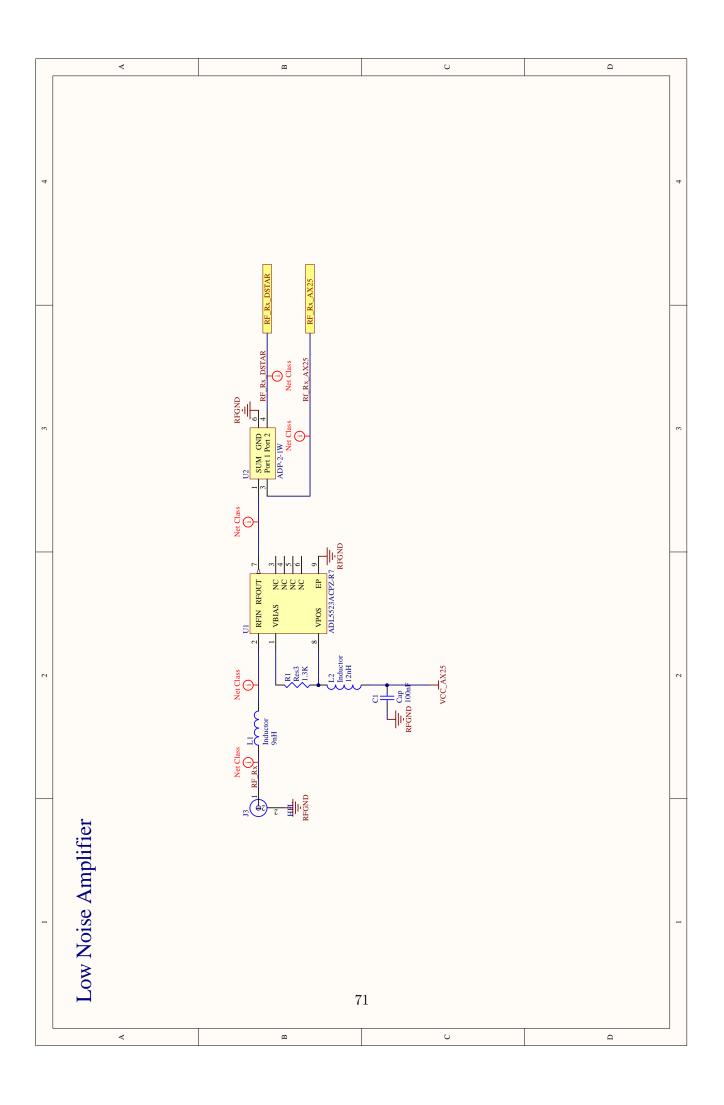

The satellite's receiving antenna captures the signal, which goes through filters and the ADL5523 Low Noise Amplifier (LNA). It is then split in 2, filtered again and goes into the 2 ADF7021 receivers, respectively for AX.25 and D-STAR. The reason for this separation is explained in 1.2.

The ADF7021 is configured, in the AX.25 case, by the OBC. It performs the FSK demodulation and outputs the bit stream to the OBC.

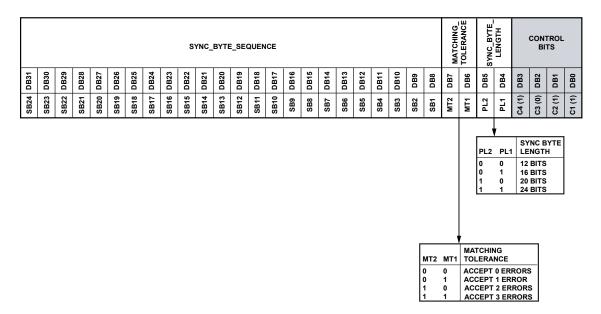

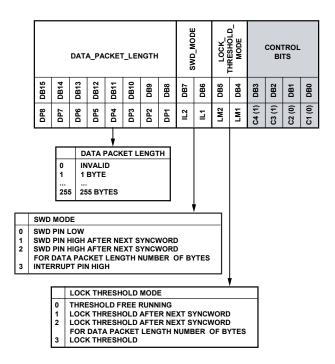

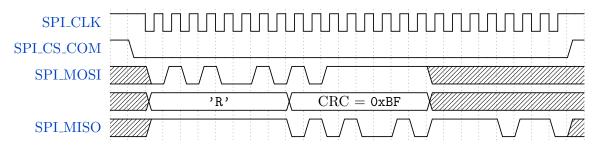

The ADF7021 also contains a Sync Word Detect (SWD) circuit [7]. Basically, an output pin of the ADF7021 is set to high when a given sequence is received. By appropriately changing the contents on register 11 and 12, one can configure:

- The pattern to look for, which can be 12, 16, 20, or 24 bits long

- The amount of tolerated errors in the received sequence to trigger the SWD, between 0 and 3 inclusive

- The length during which the SWD pin will be held high after a sync word detection: 1 bit or a given "packet length" (from 1 to 255 bytes)

- If the envelope detector threshold must lock after the reception of a sync word, and for how much time: 1 bit or a given "packet length" (from 1 to 255 bytes)

The exact contents and their final value is given in Figures 2.23 and 2.24 of 2.3.4.

#### **On-Board Computer**

The On-Board Computer is responsible for the reception of telecommands, their scheduled execution, the gathering and transmission of telemetries, logging, and the general control of the other subsystems operations [12].

The On-Board Computer receives the data line and the clock from the ADF7021. It can then reverse all the encoding performed in the TNC to access the original data. Ideally, one would want the OBC to use the SWD output from the ADF7021 as an input pin, which would enable the decoding operations. But because of the scrambling, detailed in 2.1.3, it could not be done for OUFTI-1.

#### 2.1.3 G3RUH modem

The G3RUH 9600 baud modem was developed by James Miller in 1988. Its goal is to make 9600 bauds data communication possible over a radio channel intended to transmit voice. It features 2 encoding steps, as well as a waveform generator [19].

#### Non Return to Zero Inverted (NRZI) encoding

First, the bits are modified as such: a '1' bit is encoded as a transition, and a '0' bit is encoded as no transition. With this simple encoding scheme, even if the signal is flipped, the data stays identical. It removes one source of error when using different equipment for FM communications. It also helps removing the DC component by balancing the 2 levels if there are more '0's than '1's or vice-versa in the original data. However, transmitting a long sequence of '0's will not create any transition. This is why the signal is also scrambled.

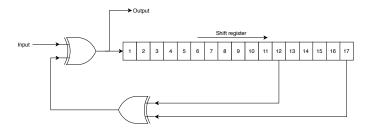

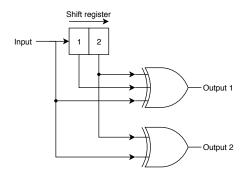

#### Scrambling

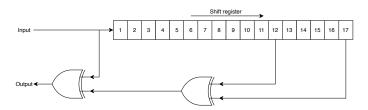

The scrambler uses a 17 bits long shift register and 3 XOR gates, as illustrated in Figures 2.9 and 2.10. It can be summarized into the following polynomial:

$$1 + x^{12} + x^{17}$$

Its goal is to further reduce the DC component by avoid long sequences of unchanged level, in the case where the useful data contains a large amount of consecutive '0's. It statistically ensures that the output signal does not stay too long without transition. Decreasing the DC component as much as possible is very important in FSK, as the receiver's Phase-Locked Loop (PLL) output frequency may drift from the real carrier frequency if the signal does not oscillate enough around it.

Figure 2.9 – Scrambler diagram

Figure 2.10 – Descrambler diagram

The shift registers of the scrambler and descrambler will naturally synchronize after having received at most 17 bits. When the shift registers are synchronized, the descrambler can work properly. This means that the descrambler needs at least 17 synchronization bits before outputting the correct data. At that point, it can already be assumed that the TNC adds synchronization bits before the flag for that purpose. In any case, synchronization bits are required for the receiver PLL to match the transmitter carrier frequency. The presence of a large amount of flags to perform both these synchronizations is confirmed to be sent for the downlink communications, as it was verified in OUFTI-1's OBC source code. The same behavior will also be observed from the TNC in 2.3.

#### Waveform generator

After these encoding steps, the TNC could naively output the binary stream to the transmitter, which would modulate it in 2-FSK. However, the theoretically instantaneous changes in the signal frequency would create a lot of higher frequency components, resulting in a much larger signal bandwidth than acceptable and distortion in the channel.

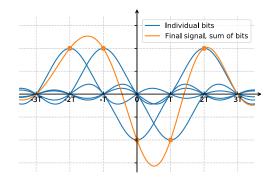

To prevent that, the TNC digitally filters the signal. It modulates each bit using a shape that compensates for the response of the channel, and that should theoretically result in a Nyquist pulse at the output of the receiver. This means that there should be no interference between bits (InterSymbol Interference ISI) [22, 23]. Examples of Nyquist pulses are the raised cosine impulse and the cardinal sine (sinc). A signal which is the sum of Nyquist pulses will theoretically be bounded in the frequency domain and stay inside a limited bandwidth, as showed in Figure 2.11. Because a Nyquist pulse has no ISI, the received signal should always be equal to +1 or -1 at the sampling points, which is verified in Figure 2.12.

Figure 2.11 – Raised cosines in the frequency domain. Image source: [20]

Figure 2.12 – Example of Nyquist pulses signal illustrating the absence of ISI. Image source: [21]

As the channel and receiver compensation cannot be predicted in advance, TNCs often offer multiple configurable waveform options. The result will never be perfect but the quality of the signal is still improved.

#### 2.1.4 The scrambled SWD issue

The issue in our case is that the scrambler's output in unpredictable. The only way to predict what its output will be is to know the contents of the shift register, which is normally obtained by receiving at least 17 bits. Its could be deducted by knowing its initial value and all the sent data. The sent data is constant as it contains AX.25 flags, but the G3RUH modem specifies that the initial value can be arbitrary. Therefore, it can be random, and that's what was assumed in [8].

So even though one wants to use the AX.25 flags as a pattern, it is theoretically not possible to predict what they will be transformed to when scrambled. That's why some processing is required to continuously descramble incoming data in order to detect the pattern, which was previously done by the OBC. But this means that the OBC is repeatedly interrupted 9600 times per second to perform a task that is useful only a handful of times per day, which is not optimal power-wise.

### 2.2 Considered potential solutions

During the research, many ideas emerged to find a workaround. The most sensible ones are listed below.

• Predict or force the initial value of shift register

Maybe the initial value of the shift register is kept or reset to a constant between

different transmissions or when the TNC is powered off. Some dummy data could

be sent to put the shift register to a known state before sending the real data for

example. Or it is possibly not random at all, therefore make the solution to this problem straightforward. It is discovered to actually be the case in 2.3.3.

Replace the TNC by another available hardware TNC, a software TNC, or a custom solution

The only feature of the TNC that makes specific hardware useful is the Nyquist pulses generator. Other than that, the TNC only performs bit operations that can easily be implemented on the computer software.

There exists many software TNCs that take advantage of the sound card of the computer to output the signal. This solution was rejected in 2008 [8] because existing software at that time was not easily configurable and did not perform well, and because basic sound cards were not expected to be able to produce an output signal of the same quality as hardware TNCs.

However, software TNCs have evolved a lot since then. A good example is Direwolf [24]. It is an open-source TNC that includes the necessary features for this application. It is clear in the source code that the scrambler shift register is always initialized to 0, which makes its output totally predictable and solves the issue.

• Bypass the TNC to send the synchronization pattern that wakes up the OBC, then use the TNC to send the effective packet. This would have been simpler than a complete custom hardware TNC. As the pattern can be repeated a high number of times to be detected, this solution would not require the same level of quality as a TNC, and could potentially work without a wavefunction generator.

Some alternative solutions, that also have been considered at some point, are listed for the sake of completeness.

- Capture the TNC output continuously to retrieve the shift register value, and use as described in the first possible solution

This is not really possible or useful, as the TNC waits to have received the complete frame from the computer before starting the transmission

- If the TNC uses a hardware shift register, like the original G3RUH modem [19], it could be probed or reset externally. It is very unlikely though, as the SCS DSP TNC contains a microcontroller that most probably performs all the bit encoding operations

- Access or change the firmware of the TNC. Asking the TNC's manufacturer for information on how the shift register is initialized was possible.

- Having a microcontroller, CPLD/FPGA, or combinational circuit on-board, that continuously descrambles the data between the ADF7021 receiver and the OBC, and performs the pattern detection. But that would add unnecessary complexity to the satellite and would defeat the purpose of removing it from the OBC.

#### 2.3 Observations and solution

Before implementing any solution, a better understanding of the practical behavior of the current TNC is required.

For the purpose of this work, the computer software has been modified in the following ways:

- The packets contain an auto-incrementing sequence number. It was kept to a constant value to be able to send exactly the same data multiple times

- The useful frame is outputted before being sent, so that it can be compared to decoded values during the tests

- Automation of the sending of a large amount of identical packets in a row

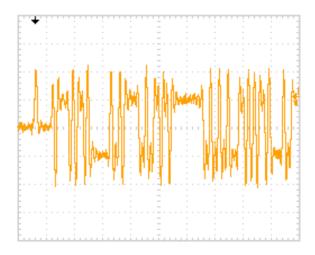

The output of the TNC has been observed using an oscilloscope, by stripping down one end of a mini-DIN cable. The beginning of a frame is shown in Figure 2.13. Although nothing can really be concluded from that observation, one can still note the Nyquist pulses that are clearly visible, and the 9600 bits per second frequency.

Figure 2.13 – Observation of the TNC output at the beginning of a frame

#### 2.3.1 Sampling

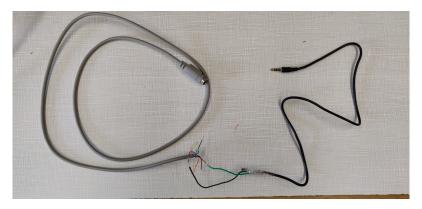

To get real insight on this particular TNC scrambler implementation, a complete frame should be analyzed. The cut end of the mini-DIN cable was attached via the DATA IN and GND wires to a 3.5 mm jack connector, as shown in Figure 2.14. The sound card of a computer was then used to record the signal. With its sampling frequency of 48 kHz, it should be able to decode the signal without any issue. The setup is shown in Figure 2.15 and the result in Figures 2.16 and 2.17. The complete frame is around 1 second long.

Figure 2.14 – Home-made mini-DIN to 3.5 mm audio jack adapter

Figure 2.15 – TNC output sampling setup. Image sources [13, 25–27]

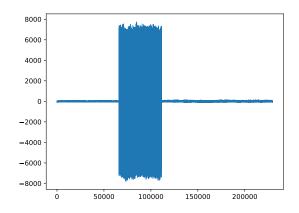

Figure 2.16 – Full recording of the TNC output

Figure 2.17 – Beginning of the transmission in the TNC output recording

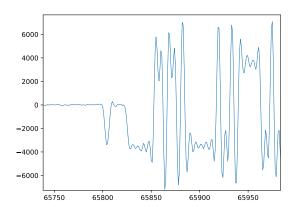

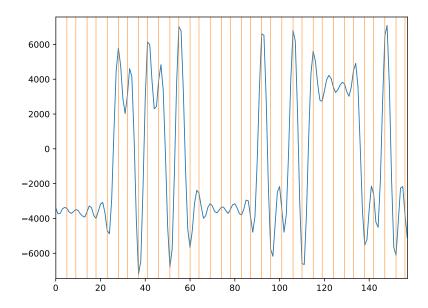

This signal must then be sampled to recover each individual bits. A simple Python script has been written, that samples the signal at 9600 bits/s, effectively taking one out of  $\frac{48000}{9600} = 5$  samples. The sign of the samples gives the corresponding bit value. It takes as input the audio file and the offset of the first bit, and returns the raw bit sequence. A few sampling points are shown in Figure 2.18.

Figure 2.18 – Sampling of the recorded output signal from the TNC

Because the sound card real sampling frequency is not a perfect multiple of the TNC real bit rate, the sampling times eventually drift. After a certain amount of bits, the sign of the sampled values may no longer reflect the correct bit. To check that this doesn't happen during the sampling of the frame, one could visually inspect the sampling points over the whole signal. Though, a much more reliable approach is to compute the absolute value of each sample, shown in Figure 2.19. The margin must be sufficient to ensure the sampled data is correct. This must be verified for each test recording.

Figure 2.19 – Absolute value of the signal at the sample points, showing drift over time

#### 2.3.2 Decoding

The raw bits can then be descrambled, NRZI decoded and bit destuffed. The initial packet is successfully recovered. The transmitted and decoded received frame are showed respectively in Figures 2.20 and 2.21.

As expected, the TNC sends around 1200 0x7E flags before the beginning of the data. This is consistent with the 1 second TX delay in the TNC settings shown in Table 2.1. It also sends 2 flags at the end. There are a few bits at the beginning and at the end of the transmission which are not well understood. They are variable even when the frame is exactly the same. They are not part of the scrambled sequence, as the following flags are scrambled independently of them. They will be ignored.

#### 2.3.3 Shift register value

As the descrambling is performed by a custom script, the contents of the shift register can be easily accessed at any point during the process. The comparison point is chosen at the first useful bit, just after the flags. This point is not chosen at the beginning of the flags as at least 17 bits are required to synchronize the shift register. Moreover, this reference point will is more consistent when the amount of unknown starting bits changes.

A total of 14 different recordings were taken, in different situations: after a power-down or after other transmissions, with packets of different length and contents. Each time, the shift register at the reference point had the same value: 110111100011111.

The state of the shift register, as well as the output, only depend on the initial shift register value and the previous sent data. Before the reference point, the data already sent is always the same as it is just composed of 0x7E flags. This means that the initial value of the shift register is always the same for that TNC.

With that in mind, it is then clear that the flags are always scrambled the same way. So even though the 0x7E flags can't directly be used as a pattern to recognize, the 9600 bits long sequence of the scrambled flags is constant and known. It is indeed verified on the raw sampled test packets. So any 12, 16, 20 or 24 bits long pattern can be selected inside it.

This pattern should preferably be chosen near the end of the flags sequence, to let enough time for the ADF7021 receiver's Phased Lock Loop to synchronize with the signal. At least 17 bits should also be left before the last flag, so that the OBC descrambler can get the correct descrambler shift register value beforehand. A possible pattern verifying these conditions has been selected: 010001010010100011110000.

Figure 2.20 – Console output of the modified software sending the frame to the TNC

```

test1

9920 samples, min abs 971, max abs 7783, min index 9456

Raw [0:100]

1010000100111000110010110001

Descrambled [0:100]

000010000000100000010000000

NRZI [0:100]

111001111110011111110011111110

1199 flags, 9592 flags bits, first flag index 28

Shift register data beginning 110111100011111

After flags

011111100110

Data length 280, remaining flags bits 20

Destuffed

Flipped (LSB first)

Final data

\tt 0x9eaa8ca89262609e9c68aa988e6103f01801c000000a10038000000000101000165ad

```

Figure 2.21 – Console output of the Python script sampling and decoding the recorded frame

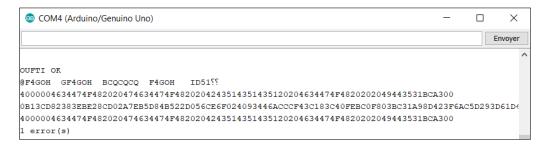

#### 2.3.4 Test of the solution

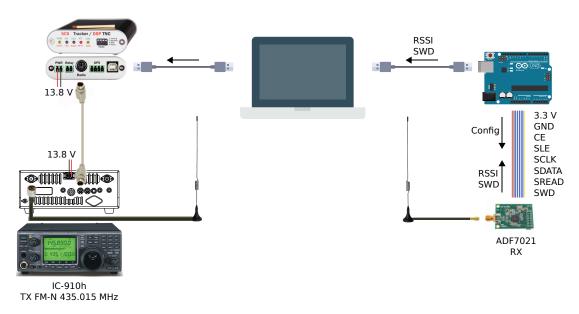

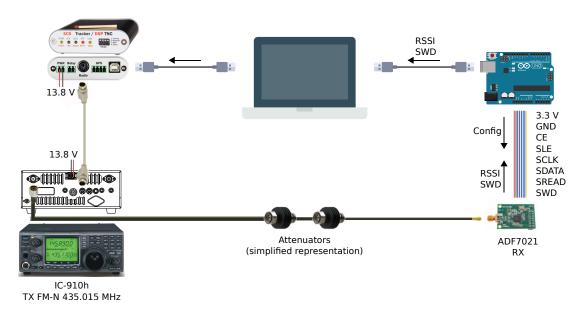

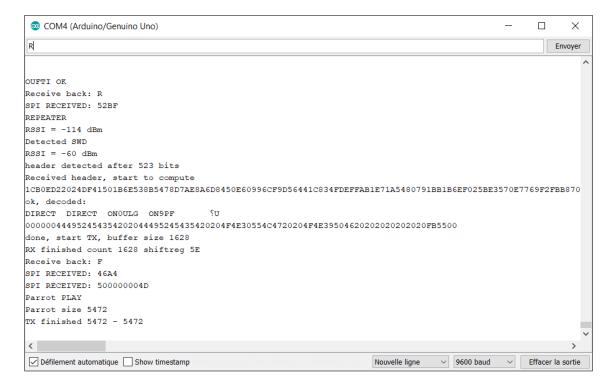

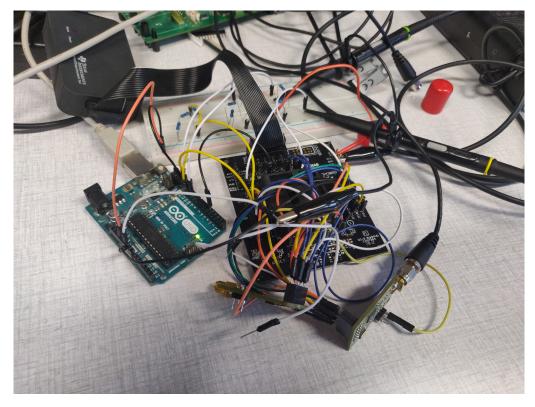

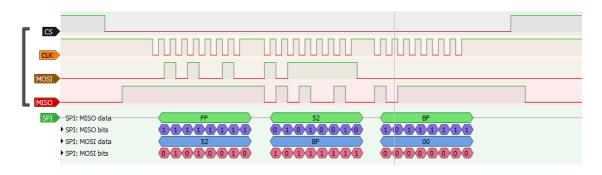

The ADF7021 is configured using a simple Arduino script. Wiring is done following the development board pinout of Table 2.2. The contents of the registers to send is copied from OUFTI-1's code. Additionally, the selected sync word has been placed inside Register 11 in the ADF7021's configuration, as shown in Figures 2.23 and 2.24. Figure 2.22 shows the test setup, where the computer, TNC and IC-910h are used to generate, encode and transmit real AX.25 frames. Meanwhile, the ADF7021's Sync Word Detect output pin is monitored.

Figure 2.22 – SWD test setup (signals from Arduino to ADF7021 must be shifted from 5V to 3.3V). Image sources: [13, 18, 26–30]

After an unsuccessful attempt, it eventually worked with all the bits of the pattern flipped. This is because the output of the TNC has been chosen, arbitrarily, to be interpreted as a '1' when positive and '0' when negative. After being modulated in FSK, this is the opposite as what the ADF7021 considers as a '1' or a '0'. It is not an issue with the useful data, which is encoded in NRZI so only the transitions are important, but it has to be taken care of for the raw pattern detection.

The same test was also successfully performed with another TNC of the same model, to make sure that the scrambling behavior was consistent and could be reproduced without trouble.

Figure 2.23 – Register 11 - Sync Word Detect Register, from ADF7021 datasheet [7] Contents for OUFTI-2: 10111010 11010111 00001111 00111011

Figure 2.24 – Register 12 - SWD/Threshold Setup Register, from ADF7021 datasheet [7] Contents for OUFTI-2: 11111111 10001100

| Dev. board pin no. | Chip pin no. | Pin function |

|--------------------|--------------|--------------|

| 1                  |              | VDD (3.3V)   |

| 2                  |              | GND          |

| 3                  | 37           | MUXOUT       |

| 4                  | 35           | TxRxCLK      |

| 5                  | 34           | TxRxDATA     |

| 6                  | 33           | SWD          |

| 7                  | 28           | SCLK         |

| 8                  | 27           | SREAD        |

| 9                  | 26           | SDATA        |

| 10                 | 25           | SLE          |

| 11                 | 24           | CE           |

| 12                 |              | GND          |

Table 2.2 – ADF7021 development board pin attribution

#### 2.4 Validation

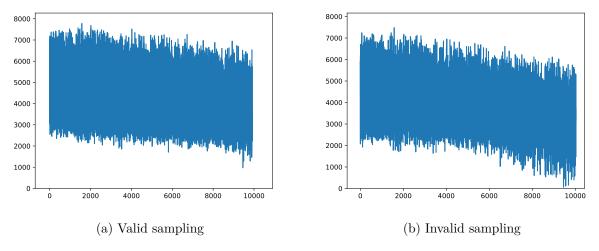

The system works as expected, but the test explained in 2.3.4 was performed in laboratory conditions, which are very different from what the satellite will encounter in space. Namely, the reception power will be much lower in space, in the order of -80 dBm instead of -50 dBm.

It should be noted that this evaluation is only performed as a verification. The ADF7021's Sync Word Detect (SWD) system is purely digital. The ADF7021 continuously demodulates the data, which is always available on the RX output pin. The SWD circuit only pushes the same data into a shift register, which is then compared to the stored pattern. It is safe to assume that if the SWD system has been verified to work at high power, and if the ADF7021 is able to correctly receive some data at some lower power, then the SWD will also work at said lower power. The proper functioning of the SWD depends on the quality of the demodulated output signal of the ADF7021, and not directly on the input signal. If we take into account that the ADF7021 reception has already been thoroughly tested in space conditions for OUFTI-1 [31], the SWD is ensured to work. However, to be on the safe side, it has been decided to perform this evaluation anyway.

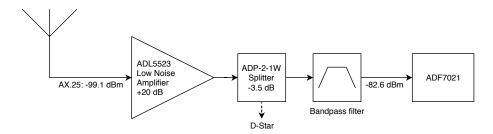

The maximum RF output power of the IC-9100 is 75W in the 430 MHz band [16]. Using an external power amplifier, it was estimated that the final output power would be 100 W. In the AX.25 uplink power budget presented in [32], the power level received by the spacecraft is computed. This gives a resulting power at the input of the satellite Low Noise Amplifier of -129.1 dBW = -99.1 dBm. The receiver noise power is also given and is -165 dBW = -135 dBm.

Figure 2.25 – AX.25 reception RF path, with power levels for 100 W emission [32], see Figure 1.3 for complete RF path

The different stages amplifying and attenuating the signal are depicted in Figure 2.25. The ADL5523 Low Noise Amplifier (LNA) amplifies the signal by 20 dB [33]. It then goes through a splitter, of which the 2 outputs respectively go into the AX.25 and the D-STAR ADF7021s. It attenuates the signal by 3.5 dB. The reason for this splitter was already explained in 2.1.2. When entering the ADF7021, the level of the signal is -82.6 dBm and the level of the noise is around 118.5 dBm. To perform the test on ground, multiple setups have been used but the received signal always directly goes in the ADF7021's input. The goal is to match the -82.6 dBm power level. For information, the sensitivity of the ADF7021 in these conditions is -114 dBm [7].

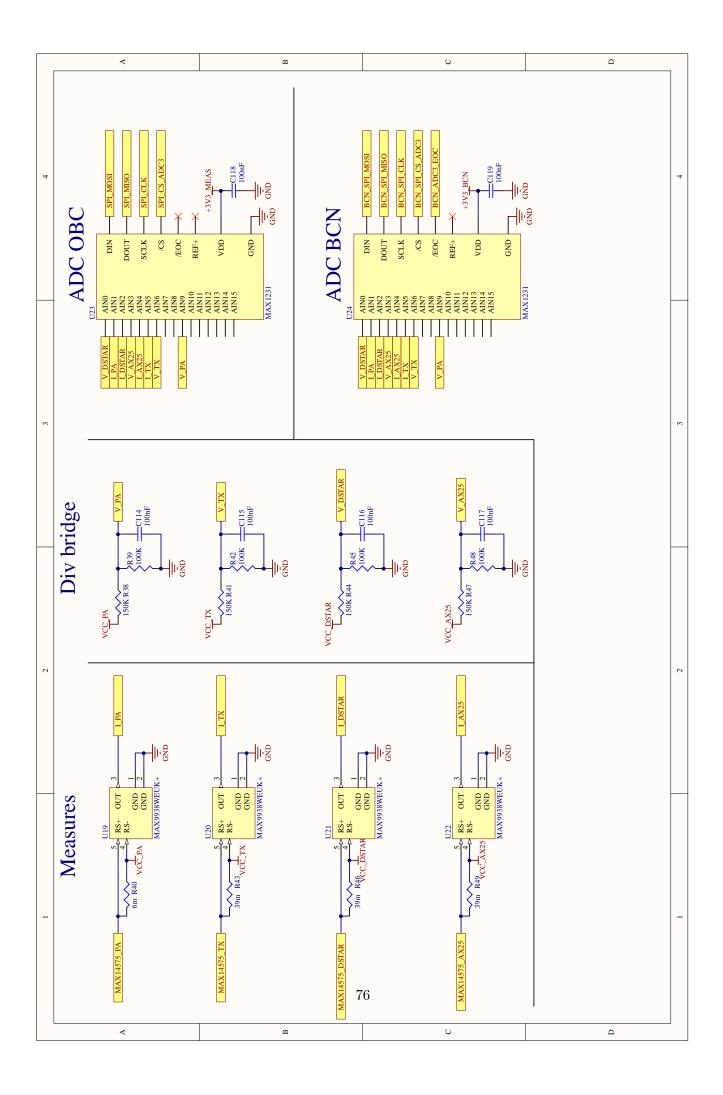

#### 2.4.1 RSSI measurement

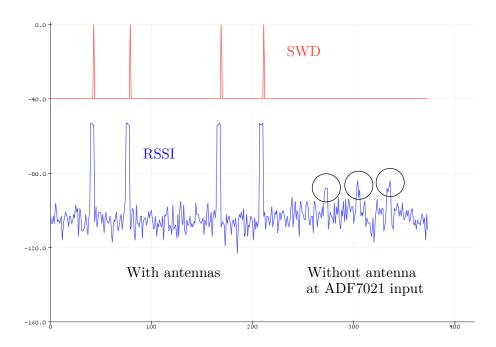

The ADF7021 is able to measure the received power level. To access it, one must send the appropriate value to Register 7, and then read what that ADF7021 send back on the SREAD pin. After a few simple calculations explained in the datasheet, the RSSI can easily be retrieved. The Arduino script that already configures the ADF7021 has been modified to regularly take an RSSI measurement and send it to the computer. The resulting graph is shown in Figure 2.26.

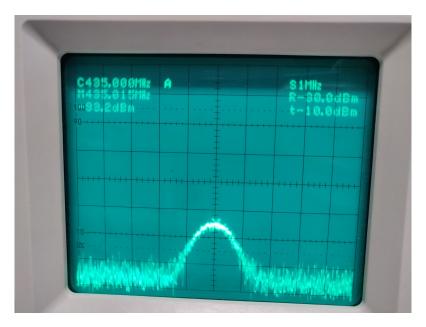

The RSSI given by this method has been compared against the one given by a spectrum analyzer, as shown in Figure 2.27. And this at several occasions during the following tests, in wire and antenna configurations and at different power levels. The difference between the levels was at most of the order of 3-4 dBm. Therefore, the RSSI given by the ADF7021 can be considered as reliable.

#### 2.4.2 Sync Word Detection rate test setup

A simple way to properly evaluate if the SWD works properly is to take the setup of 2.3.4. The software is now configured to send a series of 100 packets with a 2s interval. The Arduino script, after having configured the ADF7021, regularly takes an RSSI measurement and continuously monitors the SWD pin to count the number of times it is triggered.

Figure 2.26 – Arduino serial tracer showing the RSSI and SWD in real-time

Figure 2.27 – Spectrum analyzer measurement of the RSSI in the configuration of Figure 2.32, the ADF7021 outputting approximately the same RSSI value

Many tests were performed using different setups to try to match the -82.6 dBm theoretical power at the input of the ADF7021. Some of them showed a very variable measured RSSI, or the same results as with similar power/setups. That is the reason why only part of the tests were reported to illustrate each method.

#### Test with antennas in the same room

To have a working reference as a starting point, tests were performed using close antennas for both transmission and reception. Even with the RF output power of the IC-910h at the minimum, the ADF7021 input power is still obviously very high. These first results, presented in Table 2.3, show that in ideal RF conditions, the SWD works every time.

| Setup                                  | Measured RSSI      | Detection | rate |

|----------------------------------------|--------------------|-----------|------|

| Antenna - Antenna in the same room     | -50 dBm            | 100/100   | 100% |

| Receiving antenna without ground plane | -63  dBm           | 100/100   | 100% |

| With -20 dB attenuator                 | $-68~\mathrm{dBm}$ | 100/100   | 100% |

| With -40 dB attenuator                 | -80 dBm            | 87/100    | 87%  |

Table 2.3 – Sync Word Detection rate test results for antennas in the same room (IC-910h)

An unexpected phenomenon can already be observed. The measured RSSI only decreases by 12 dB when a -20 dB attenuator is added. This kind of non-idealities will be encountered again and some possible explanations will be given in the wired tests below.

#### Wired test with attenuators

The power obtained using antennas varies a lot over time and when moving the antennas around. The RF characteristics of the signal are difficult to monitor and control. Unknown multi-path effects, due to reflections on the nearby environment, are non-negligible at that small scale. To correctly assess the detection rate to input power relation, a reproducible, consistent, test setup is preferable. A chain of attenuators, shown in Figure 2.28, was used to achieve a completely wired configuration, illustrated in Figure 2.29. As most attenuators can only withstand up to 1 W and the minimum output power of the IC-910h is 5 W, the first one is a R415610000 -10 dB attenuator with a maximum input power of 15 W. Then, several attenuators (up to -20 dB each) are combined to get to the desired power level.

Figure 2.28 – Attenuator chain with the necessary adapters

Figure 2.29 – Sync Word Detect wired test setup (signals from Arduino to ADF7021 must be shifted from 5V to 3.3V). Image sources: [13, 18, 26–29]

As shown in Table 2.4, these tests could not confirm that the system works. As soon as -60 dBm, the SWD starts to fail. An interesting observation is that the measured RSSI begins to rise again when adding more attenuators at some point. This probably means that there are RF interactions between the attenuators or with the transmitter or receiver. For example, the first -10 dB attenuator may radiate some power that will be strong enough to be picked up by another one that works at much lower power. The measured RSSI is indeed very unstable, and varies when the attenuators are moved around and when they are held in hand, sometimes changing from around -70 dBm to -100 dBm. This is not a normal behavior for these attenuators, but it is difficult to diagnose its cause. If one of the attenuators, adapters or cable was malfunctioning, it could have been identified using a VNA (Vector Network Analyzer) to measure the S parameters of the chain. These checks were not performed.

| Setup                         | Theoretical RSSI   | Measured RSSI      | Detection rate |      |

|-------------------------------|--------------------|--------------------|----------------|------|

| Wired with -90 dB             | -53 dBm            | -55 dBm            | 100/100        | 100% |

| Wired with $-100~\mathrm{dB}$ | $-63~\mathrm{dBm}$ |                    | 96/100         | 96%  |

| Wired with -110 $\mathrm{dB}$ | $-73~\mathrm{dBm}$ | $-72~\mathrm{dBm}$ | 194/200        | 97%  |

| Wired with $-120~\mathrm{dB}$ | $-83~\mathrm{dBm}$ | $-65~\mathrm{dBm}$ | 281/300        | 94%  |

| Wired with $-123~\mathrm{dB}$ | $-86~\mathrm{dBm}$ |                    | 188/200        | 94%  |

| Wired with $-126 \text{ dB}$  | $-89~\mathrm{dBm}$ |                    | 97/100         | 97%  |

| Wired with -130 dB            | -93 dBm            |                    | 89/100         | 89%  |

Table 2.4 – Sync Word Detection rate test results for wired link with attenuators (IC-910h)

#### Wired test in a TEM-Cell

In order to mitigate these RF interactions that are the likely cause of the bad results, they were performed again in the TEM (Transverse Electromagnetic) cell of the Electronics Department of the HEPL Industrial School (ISIL). This cell works for electromagnetic waves up to 300 MHz. Therefore, it is not supposed to work perfectly at 435 MHz but should still attenuate the RF signal. As it was easily available, it was tried anyway, with the setup of Figure 2.30.

Figure 2.30 – Setup for the wired test in a TEM-Cell (the cell was closed during the tests)

Multiple configurations have been tested:

- Only all attenuators inside

- Only some (the first or last few) attenuators inside

- Only the receiving ADF7021 inside

- Only the receiving ADF7021 inside, with all or the last few attenuators

None of them worked any better than without the TEM-Cell. Changing the position of the attenuators inside the cell was still creating huge differences in the measured power.

#### Test with antennas at different locations

In order to avoid the interactions and the multi-path effect happening because of the proximity of the transmitter and receiver, the 2 antennas approach was brought back. This time, the low power levels were obtained by physically separating the antennas in different parts of the building.

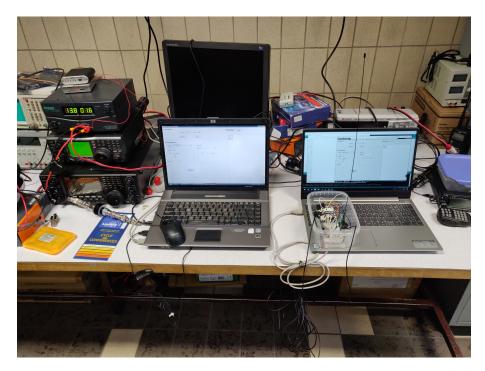

Figure 2.31 – Setup for the test with antennas at different locations. Left: Transmitting PC. Right: Moving receiving PC, controlling the left one

The test setup is, this time, made up of 2 different computers, as shown in Figure 2.31. The one which will be moving with the receiving ADF7021 has control over the transmitter one through TeamViewer. This allows to operate the transmission from the mobile location. The measurements of Table 2.5 were taken from different places in the HEPL (ISIL) building, and from different floors. The maximum distance is estimated to be around 60-80 meters<sup>2</sup>. In most cases, there were several walls between the transmitter and receiver. Again, due to the configuration of the building, the RSSI was varying a lot, probably indicating strong reflections. The results seem more reliable but there are still a lot of missing SWDs. The detection rate does not seem to be as dependent on the RSSI as before.

<sup>&</sup>lt;sup>2</sup>Distance measured on Google Maps satellite view

| Measured RSSI      | Detection | rate |

|--------------------|-----------|------|

| -47 dBm            | 95/100    | 95%  |

| $-55~\mathrm{dBm}$ | 98/100    | 98%  |

| $-60~\mathrm{dBm}$ | 92/100    | 92%  |

| $-70~\mathrm{dBm}$ | 94/100    | 94%  |

Table 2.5 – Sync Word Detection rate test results for antennas at different locations (IC-910h)

To decrease further more the received power level, the transmitting antenna was replaced with a dummy 50  $\Omega$  load. The power levels were lower of a few dB while still way above -80 dBm. The detection rates were similar.

### 2.4.3 Bit Error Rate hypothesis verification

After the unsuccessful described above, it was unclear what the exact cause of the bad detection rates was. Is is correlated with the RSSI, which theoretically isolates the analog parts (transmitter, channel and receiver) as the only possible suspects. The goal is to characterize the SWD system of the ADF7021, which relies on the receiver. The Bit Error Rate (BER) must be measured to verify that the errors are already present at the output of the receiver, and thus are not caused by SWD system.

This is even more concerning knowing that the descrambling process will inevitably multiply the amount of errors, and that AX.25 does not include any error correction mechanism.

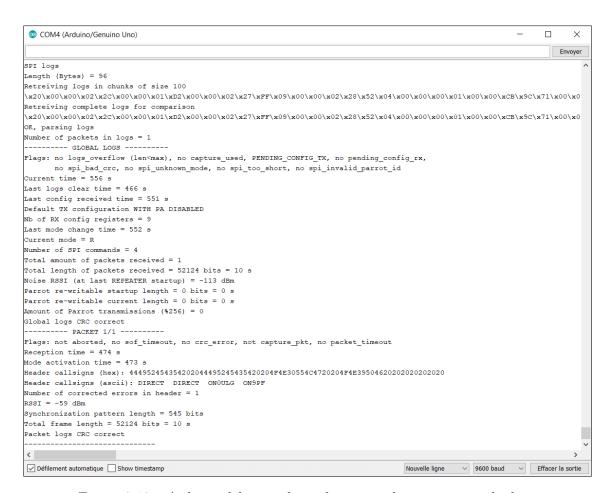

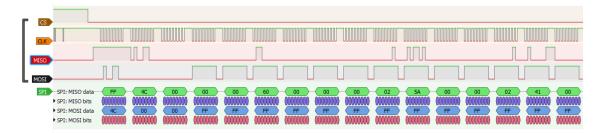

As the D-STAR repeater was developed in parallel, the new tests were performed using the D-STAR microcontroller, instead of the Arduino. The of the microcontroller was modified to configure the ADF7021 with the AX.25 registers, count the number of Sync Word Detections, monitor the RSSI and compare the first 336 bytes received with the given reference AX.25 packet.

As a side note, this test also successfully checks that the packet can be correctly received after a SWD interrupt, and that there is enough data to initialize the descrambler and detect an AX.25 flag before the frame.

The tests with two antennas and with a charge at the transmitter's output were performed again. It is clear that the SWD success rate is function of the BER.

Even though the test setup was probably the cause of the issue, and the SWD system was ruled out, this is still concerning as such a BER in space would make any communication with the satellite impossible. More investigation was thus absolutely necessary.

#### Test with IC-9100

A frequency mismatch was another possible cause for this issue. To be able to tune more precisely the carrier frequency of the transmitter, the IC-910h was replaced by the IC-9100. The IC-9100 minimal output power is 2 W instead of 5 W for the IC-910h, already reducing the level by around 4 dB and possibly avoiding some of the unwanted RF effects. These tests could also eliminate the hypothesis of a defective IC-910h radio. The modified test setup is shown in Figure 2.32.

Figure 2.32 – Bit Error Rate test setup (signals from Arduino to ADF7021 must be shifted from 5V to 3.3V). Image sources: [13, 18, 26–30, 34]

Because the RSSI reading, as well as the power output tuning are not that precise, a large number of packets were sent and processed, with very small changes to the power output. The results in Table 2.6 are not sufficiently accurate to determine the limit power level, but it can be assumed that the system works as it should at power levels close to the -82.6 dBm target. Some tests were also performed with another nearly identical antenna. For unknown reasons, it showed a lower RSSI, so the output power of the IC-9100 was increased to stay around -83 dBm again. In practice, the measured RSSI was varying between -81 dBm and -85 dBm during the test but they were not discriminated. The results were even closer to the goal.

| Setup                      | Radio   | Measured RSSI      | Bit error rate |               | Packet error rate |     |

|----------------------------|---------|--------------------|----------------|---------------|-------------------|-----|

| Charge TX, antenna RX      | IC-910h | -64 dBm            | 0/(10 * 336)   | 0             | 0/10              | 0%  |

| Idem with $-20 \text{ dB}$ | IC-910h | $-71~\mathrm{dBm}$ | 0/(10*336)     | 0             | 0/10              | 0%  |

| Idem with $-20$ dB and     | IC-9100 | $-81~\mathrm{dBm}$ | 0/(13*336)     | 0             | 0/13              | 0%  |

| tuning the radio RF        |         | $-82~\mathrm{dBm}$ | 1/(15*336)     | $2.0*10^{-4}$ | 1/15              | 7%  |

| output power knob          |         | $-83~\mathrm{dBm}$ | 3/(16*336)     | $5.6*10^{-4}$ | 3/16              | 18% |

|                            |         | $-84~\mathrm{dBm}$ | 15/(21*336)    | $2.1*10^{-3}$ | 10/21             | 48% |

|                            |         | $-85~\mathrm{dBm}$ | 10/(17*336)    | $1.8*10^{-3}$ | 6/17              | 35% |

|                            |         | $-86~\mathrm{dBm}$ | 14/(14*336)    | $3.0*10^{-3}$ | 9/14              | 64% |

|                            |         | $-87~\mathrm{dBm}$ | 12/(8*336)     | $4.5*10^{-3}$ | 7/8               | 88% |

|                            |         | -88 dBm            | 2/(1*336)      | $6.0*10^{-3}$ |                   |     |

| Idem with other antenna    | IC-9100 | $\sim$ -83 dBm     | 2/(100*336)    | $6.0*10^{-5}$ | 2/100             | 2%  |

Table 2.6 – Bit Error Rate on 336 bits long packets

#### 2.4.4 Conclusion

In the end, the best Bit Error Rate that has been experimentally achieved for the aimed -82.6 dBm power level is  $\sim 6*10^{-5}$ , which is not the predicted  $10^{-5}$  [32] but still in the same order of magnitude. The test conditions of [31], with few errors<sup>3</sup> at -105 dBm could unfortunately not be reproduced. However, the results obtained here are judged good enough to guarantee that the satellite will eventually be able to receive telecommands without issue, even though it may sometimes need re-transmission. Moreover, the tests were performed in more difficult conditions than in space regarding noise and multi-path. Overall, it was proven that the Sync Word Detect system in itself works, as long as the reception works as well. Because evaluating the telecommand transmission quality was not part of the statement of this thesis, there was no further investigation. The initial issue is considered fixed and validated.

As a reminder, the proposed solution is to set the AX.25 RX ADF7021 configuration register 11 to 10111010 11010111 00001111 00111011 and register 12 to 11111111 10001100. In short, these value will allow AX.25 uplink frames to be detected by the ADF7021, which will then set the SWD pin to high. It does not require any other hardware or software change. It should be noted that the configuration registers bytes are given in reverse order in OUFTI-1's OBC and D-STAR source codes, as well as in the Excel register value computation spreadsheet. For a concrete example and the complete ADF7021 AX.25 configuration, see in file adf7021.c of OUFTI-2's D-STAR repeater source code.

<sup>&</sup>lt;sup>3</sup>But no Bit Error Rate measurement

## Chapter 3

# D-STAR relay

### 3.1 D-STAR

D-STAR<sup>1</sup> is an amateur radio protocol for digital voice and data transmission [35, 36]. It was introduced in 2001 by the Japanese Amateur Radio League (JARL). It is usually used in the 145 MHz, 430 MHz and 1.2 GHz ITU amateur radio bands. The main D-STAR compatible radio manufacturer is Icom. D-STAR is encoded in GMSK (Gaussian Minimum Shift Keying) and occupies a bandwidth of 6.25 kHz per channel. D-STAR offers 2 types of packets: Digital Voice (DV) and Digital Data (DD), which is less common and not supported by the repeater. The structure of a DV D-STAR frame is shown in Figure 3.1. The transmission alternates between 72 bits long voice slots and 24 bits long data slots. The 1<sup>st</sup>, 22<sup>nd</sup>, 43<sup>rd</sup>, ... data slots are replaced with a synchronization flag containing a fixed sequence. This mode works at 4800 bits/s with 3600 bits/s of audio encoded with the AMBE codec, 1200 of which are dedicated to Forward Error Correction (FEC), and the remaining 1200 bits/s available for data. The AMBE (Advanced Multiband Excitation) audio encoding protocol is developed by Digital Voice Systems (DVSI) and is proprietary. The contents of the audio stream is not important for this work as it does not need to be decoded but only repeated. A D-STAR frame can have any arbitrary length after the header but the End Of Frame must be placed in place of a synchronization time slot<sup>2</sup>.

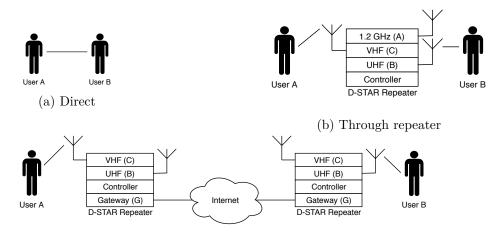

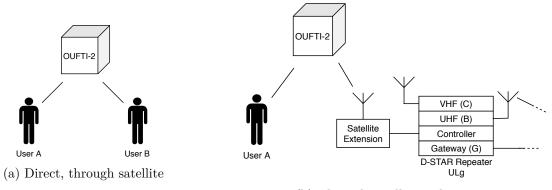

D-STAR provides an addressable repeater feature, typically working on multiple frequency bands, and frame routing between different repeater stations and even through gateways connected to the internet. OUFTI-1 and OUFTI-2 repeaters are not traditional D-STAR repeaters though, in the sense that they repeat every incoming frame, without taking the repeater callsigns of the header into account.

The various modes of operations available with D-STAR are presented in Figure 3.2. The satellite provides the additional options of Figure 3.3. A D-STAR repeater was installed in the University in 2008 [37].

<sup>&</sup>lt;sup>1</sup>Digital Smart Technologies for Amateur Radio

<sup>&</sup>lt;sup>2</sup>This was not taken into account in OUFTI-1's D-STAR relay

Figure 3.1 – D-STAR Digital Voice frame structure [38]

(c) Through different repeaters connected to the internet

Figure 3.2 – D-STAR normal communication modes [35]

(b) Through satellite and repeater

Figure 3.3 – D-STAR communication modes with OUFTI-2 [37]

#### 3.1.1 D-STAR header

The header contains some control flags, the address callsigns and a Frame Check Sequence (FCS). The FCS is a Cyclic Redundancy Check computed same 16 bits CCITT polynomial as AX.25:

$$x^{16} + x^{12} + x^5 + 1$$

The header is first convoluted, doubling in length, going from 41 Bytes = 328 bits to 660 bits. The difference filled with padding '0's. Odd bits are generated with the polynomial  $1 + x + x^2$  and even bits with  $1 + x^2$ , as illustrated in Figure 3.4.

Figure 3.4 – Convolution diagram

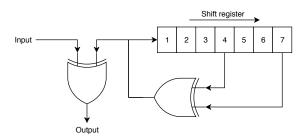

It is then scrambled to eliminate the DC component of the signal, using a 7 bits long shift register and the following polynomial:

$$x^7 + x^4 + 1$$

Unlike AX.25 G3RUH scrambling, detailed in 2.1.3, the generated pseudo-random sequence is independent of the data. The shift register is initialized to 0xFF. Descrambling is identical to scrambling. This process is showed in Figure 3.5.

Figure 3.5 – Scrambler/descrambler diagram

Is is finally interleaved with a depth of 24, to spread error bursts.

The decoding process is straightforward for de-interleaving and descrambling. The deconvolution is performed using the Viterbi algorithm [39], which use a state representation of the convolution to return the most likely initial bit sequence, and correct some errors of the header introduced during the transmission.

### 3.2 Specifications

The initial required specifications for the new repeater as well as the additional modifications are:

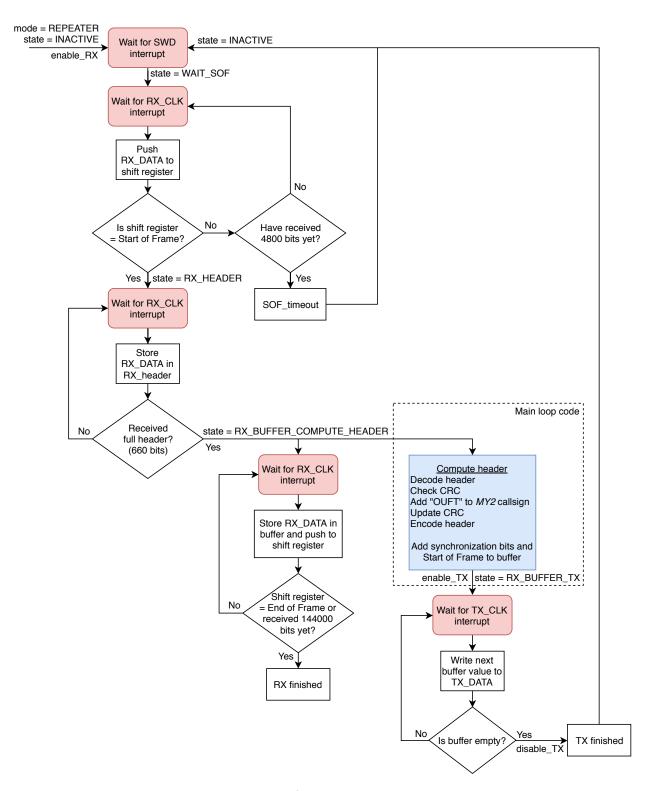

- Repeater mode: as in OUFTI-1, the microcontroller must have a mode in which it receives D-STAR frames at 435.045 MHz and repeats them at 145.950 MHz. The header must be decoded and re-encoded to correct the errors, and the MY2 callsign (see Figure 3.1) must be set to "OUFT" to show that the packet was processed and repeated by the satellite. The repeater operations are detailed in 3.5.

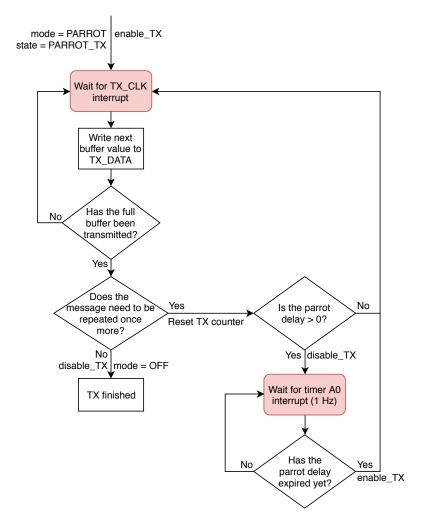

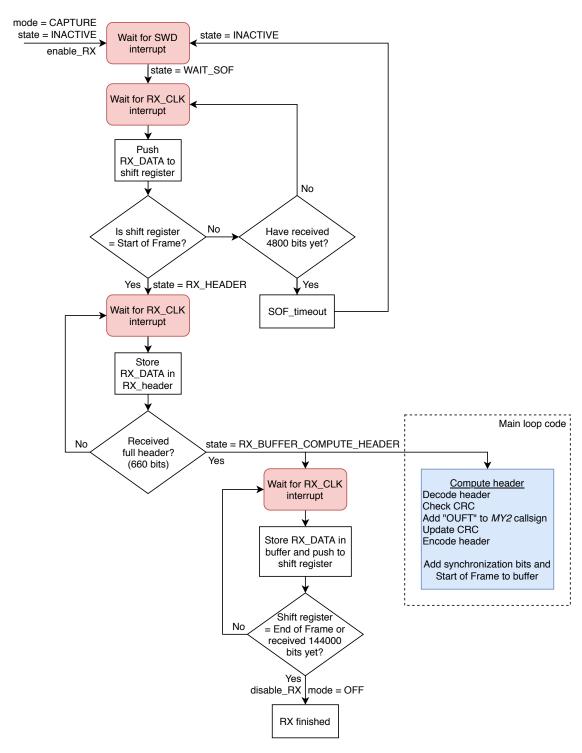

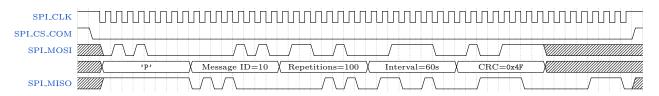

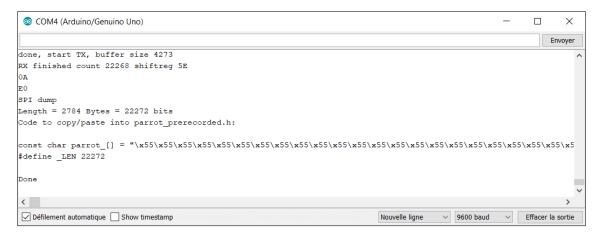

- Parrot mode: in this new mode, the microcontroller must transmit a frame stored in memory when told by the OBC. The goal is to be able to test the transmission independently from the reception. The frame may be transmitted a given amount of times with a given delay. It was not initially planned but the parrot frames may be pre-recorded on ground and there is also a re-writable slot, which can be overwritten in flight. The parrot operations are detailed in 3.6.

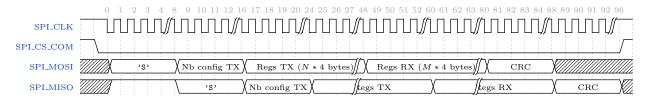

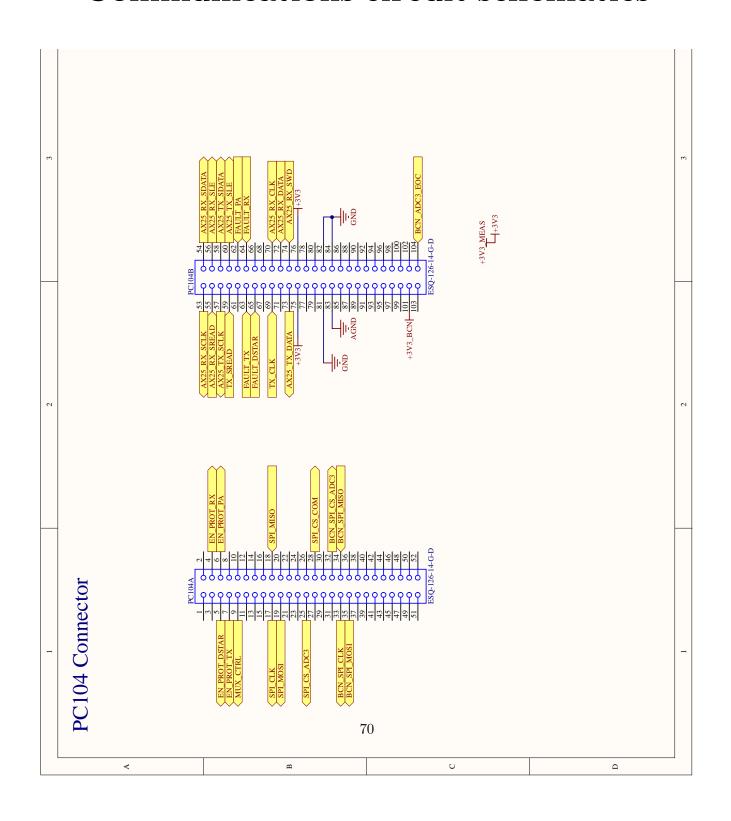

- Communications with the OBC must now be done on an SPI bus instead of the USART channel of OUFTI-1. The bus is shared with other subsystems. The OBC is the master and sends commands which must contain some kind of checksum and be acknowledged by the D-STAR microcontroller. Unlike OUFTI-1, the repeater does not request the OBC to enable or disable the Power Amplifier, but the enable signal goes through the multiplexer, as explained in 1.2. The SPI communications with the OBC are detailed in 3.8.

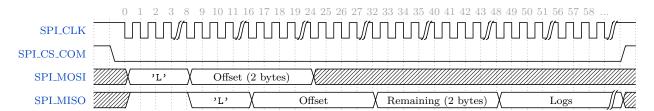

- The repeater must log the callsigns of the processed frames and the number of frames. When ordered so by the OBC, it must respond with those data. The final implementation logs much more data than that for each packet, and all of this is transmitted to the OBC and then to the ground in chunks of length determined by the OBC. The logs contents and SPI command are detailed in 3.8.3.

- As for OUFTI-1, the configuration registers of the ADF7021s must be alterable from the ground. Unlike OUFTI-1 though, the configuration can be sent as a whole and not necessarily one register at a time. Also, the configuration is stored and applied at each ADF7021 startup. In OUFTI-1, it was actually impossible to modify the TX configuration, as it was only applied once and the TX ADF7021 is reset at each transmission. The ADF7021 configuration register modification SPI command is detailed in 3.8.2.